有限状态机

有限状态机是由寄存器组和组合逻辑构成的硬件时序电路,其状态(即由寄存器组的1和0的组合状态

所构成的有限个状态)只可能在同一时钟跳变沿的情况下才能从一个状态转向另一个状态,究竟转向

哪一状态还是留在原状态不但取决于各个输入值,还取决于当前所在状态。(这里指的是米里Mealy型有限状态

机,而莫尔Moore型有限状态机究竟转向哪一状态只决于当前状态。)

例

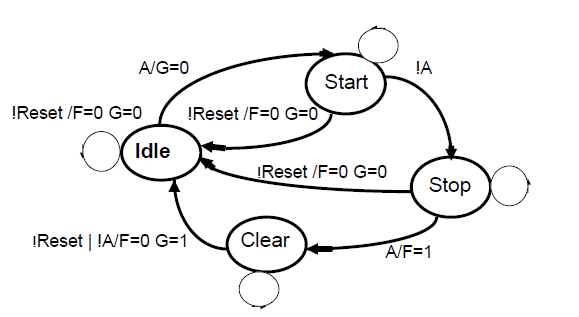

采用独热码实现的有限状态机。采用了独热编码后有了多余的状态,就有一些不可到达的状态,为此在CASE语句的最后需要增加default分支项,以确保多余状态能回到Idle状态。

1 module fsm (Clock, Reset, A, F, G); 2 input Clock, Reset, A; 3 output F,G; 4 reg F,G; 5 reg [3:0] state ; 6 parameter Idle = 4’b1000, 7 Start = 4’b0100, 8 Stop = 4’b0010, 9 Clear = 4’b0001; 10 always @(posedge clock) 11 if (!Reset) 12 begin 13 state <= Idle; F<=0; G<=0; 14 end 15 else 16 case (state) 17 Idle: begin 18 if (A) begin 19 state <= Start; 20 G<=0; 21 end 22 else state <= Idle; 23 end 24 Start: if (!A) state <= Stop; 25 else state <= Start; 26 Stop: begin 27 if (A) begin 28 state <= Clear; 29 F <= 1; 30 end 31 else state <= Stop; 32 end 33 Clear: begin 34 if (!A) begin 35 state <=Idle; 36 F<=0; G<=1; 37 end 38 else state <= Clear; 39 end 40 default: state <=Idle; 41 endcase 42 endmodule

用always语句和连续赋值语句把状态机的触发器部分和组合逻辑部分分成两部分来描述。

1 module fsm (Clock, Reset, A, F, G); 2 input Clock, Reset, A; 3 output F,G; 4 5 reg [1:0] state ; 6 wire [1:0] Nextstate; 7 parameter Idle = 2’b00, 8 Start = 2’b01, 9 Stop = 2’b10, 10 Clear = 2’b11; 11 12 always @(posedge Clock) 13 begin 14 if (!Reset) 15 begin 16 state <= Idle; 17 end 18 else 19 state <= Nextstate; 20 end 21 22 assign Nextstate = ( state == Idle ) ? ( A ? Start : Idle ) : 23 ( state==Start ) ? ( !A ? Stop : Start ) : 24 ( state== Stop ) ? ( A ? Clear : Stop ) : 25 ( state== Clear) ? ( !A ? Idle : Clear) : 26 Idle; 27 assign F = (( state == Stop) && A ); 28 assign G = (( state == Clear) && (!A || !Reset)); 29 30 endmodule

用沿触发的always语句和电平敏感的always语句把状态机的触发器部分和组合逻辑部分分成两部分来描述。

1 module fsm (Clock, Reset, A, F, G); 2 input Clock, Reset, A; 3 output F,G; 4 5 reg [1:0] state, Nextstate; 6 parameter Idle = 2’b00, 7 Start = 2’b01, 8 Stop = 2’b10, 9 Clear = 2’b11; 10 11 always @(posedge Clock) 12 begin 13 if (!Reset) 14 begin 15 state <= Idle; 16 end 17 else 18 state <= Nextstate; 19 end 20 21 always @( state or A ) 22 begin 23 F=0; 24 G=0; 25 if (state == Idle) 26 begin 27 if (A) 28 Nextstate = Start; 29 else 30 Nextstate = Idle; 31 G=1; 32 end 33 else 34 if (state == Start) 35 if (!A) 36 Nextstate = Stop; 37 else 38 Nextstate = Start; 39 else 40 if (state == Stop) 41 if (A) 42 Nextstate = Clear; 43 else 44 Nextstate = Stop; 45 else 46 if (state == Clear) 47 begin 48 if (!A) 49 Nextstate = Idle; 50 else 51 Nextstate = Clear; 52 F=1; 53 end 54 else 55 Nextstate= Idle; 56 end 57 end 58 endmodule

状态必须明确赋值,通常使用参数(parameters)或宏定义(define)语句加上赋值语句来实现。

原则 1:时序电路建模时,用非阻塞赋值。

原则 2:锁存器电路建模时,用非阻塞赋值。

原则 3:用always 块写组合逻辑时,采用阻塞赋值。

原则 4:在同一个always 块中同时建立时序和组合逻辑电路时,用非阻塞赋值。

原则 5:在同一个always 块中不要同时使用非阻塞赋值和阻塞赋值。

原则 6:不要在多个always 块中为同一个变量赋值。