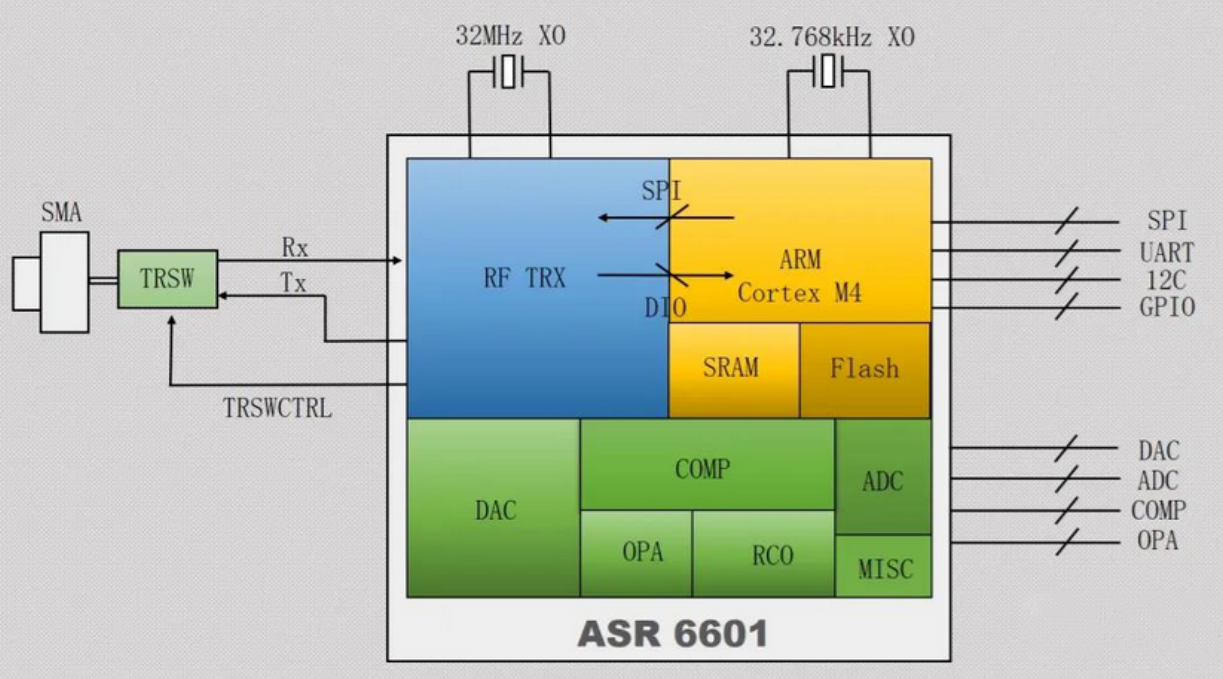

ASR6601为目前首颗国产支持LoRa的LPWAN低功耗广域网无线通信SoC芯片。ASR6601在单一芯片上集成了通用微控制器和射频单元,包括射频收发器,调制解调器和一个48 MHz 主频、采用Arm Cortex M4架构的32位MCU。多种内存选择包括最大256KB的闪存和64KB的SRAM等,内置嵌入式LCD驱动程序,支持AES、DES、RSA、ECC、SHA、SM2/3/4硬件加密。与此同时,ASR6601可以达到-148dBm的超高灵敏度,以及最大22dBm的发射功率,而QFN48最小尺寸仅6mm x 6mm。通过SoC设计,ASR6601成为目前市场上功耗更优、性能最强、成本最低的LPWAN芯片,极大降低了用户设计门槛,同时帮用户节省大量开发时间并减少物料清单和运营成本,尤其适用于大批量应用的项目和需要定制化设计的项目。

关键特性

*SX1262 IP授权+Arm Cortex M4内核*

● 频率范围:150MHz~960MHz

● 最大功率+22 dBm射频输出

● 高灵敏度:-148 dBm

● 支持Class A/B/C/AliWAN协议

● 在LoRa调制模式下可编程比特率高达62.5 Kbps

● 在(G)FSK调制模式下可编程比特率高达300 Kbps

● 前导码检测

● 嵌入式内存(高达256 KB的闪存和64 KB的SRAM)

● 32.768千赫外部手表晶体振荡器

● 射频收发器用32Mhz外部晶体振荡器

● SoC用24 MHz外部晶体振荡器(可选)

● 内置4mhz RC振荡器

● 嵌入式内部高频(48mhz)RC振荡器

● 嵌入式内部低频(32.768 KHz)RC振荡器

● 嵌入式内部锁相环产生48兆赫时钟

● 多达42个可配置GPIO:3 x I2C、1 x I2S、4 x UART、1 x LPUART、1 x SWD、3 x SPI,1 x QSPI和2 x WDG

● 4 x GPtimer、2 x Basic Timer、2 x LP Timer和1 x Sys Ticker

● 48兆赫ARM Cortex-M4 CPU

● 4通道DMA引擎x 2

● 嵌入式12位1 Msps SAR ADC

● 嵌入式12位DAC

● 嵌入式3 x OPA

● 嵌入式2 x低功耗比较器

● 嵌入式LCD驱动程序

● 嵌入式LD、TD、VD和FD

● 支持AES、DES、RSA、ECC、SHA和SM2/3/4

● 封装:QFN48,6 mm x 6 mm(ASR6601CB) GPIO 26个

QFN68,8 mm x 8 mm(ASR6601SE) GPIO 42个

可以使用KEIL开发,也可以使用Makefile的方式进行编译烧录。

ASR6601结构框图

可提供软硬件资料及技术支持,周13682545343