使用Timequest

笔者对Altera较熟悉,这里以quartus ii中的timequest作为讲解。

Timequest分析时序的核心,也就是在于延迟因数的计算。那么建立约束文件,去告诉timequest,哪个地方有什么样的约束,该怎么进行约束。

之所以要建立相关网表的概念,是因为我们在利用quartus ii 中的timequest 时,大致的流程是:建立网表----建立SDC文件----更新网表;

2.1 SDC网表

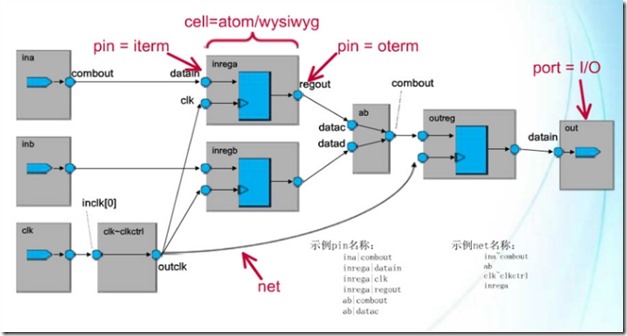

SDC网表包括:端口(port),引脚(pin),单元(cell),网(net),下图可以解释各个部分的概念。

那么接下来我们要使用timequest,同使用signaltap ii一样,在使用之前先建立一个SDC文件,文件名可以任意取,建议和模块名一样吧。然后另存为你所命名的名字。

2.2 建立 timing netlist

然后 在使用timequest之前,先要编译一下源文件,建立好适配文件才可以,请注意!!!

然后点击timequest按钮进入到timequest中,如下面所示,

上述三个命令是比较重要的命令,第一个是创建网表,开始布线,建立硬模型,第二个是读SDC文件,第三个是更新网表,每当有所改动,需要更新一次。

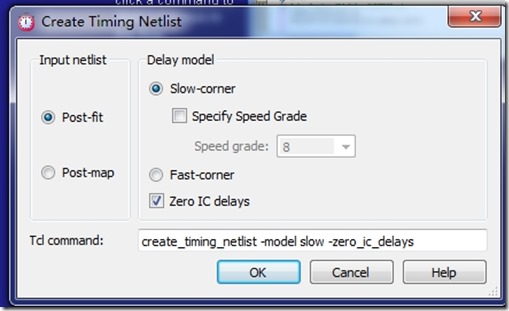

图16.5 适配情况

上面的post-map,是没有经过优化的,更接近与原型。

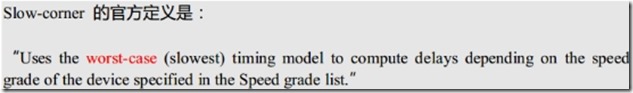

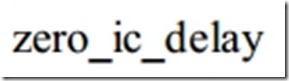

关于是适配较好的情况还是适配较差的情况,这个根据设计去设定,一般最差情况能够通过,那么较好的情况也一定能够通过。

一般按照图16.5就够用了。这也是双击 产生的结果。当然也可以自己手动去设定,那就是

产生的结果。当然也可以自己手动去设定,那就是 即可。

即可。

2.3 建立 SDC文件

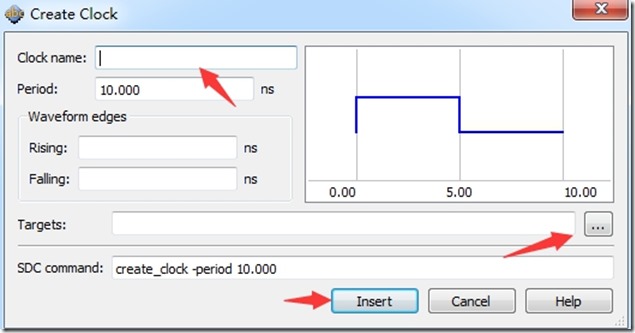

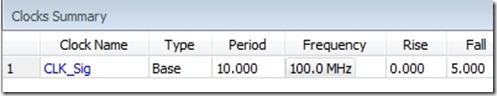

注意上述的clock name是和全局时钟网络的名字是一致的,targets这里选择你所设定的全局时钟网络。

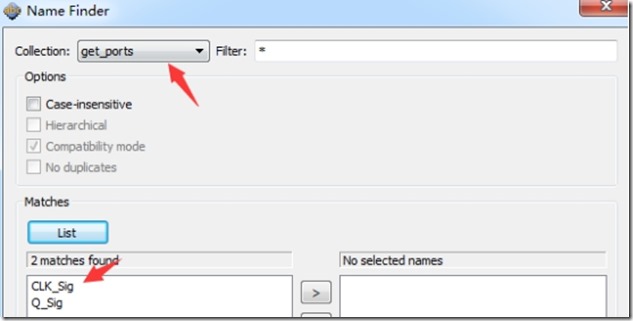

选择get_ports,点击list按钮,选择时钟信号。要约束其他信号方法一样。

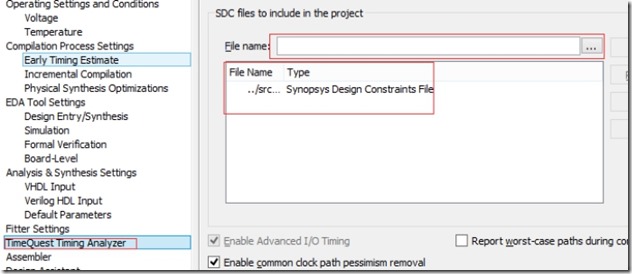

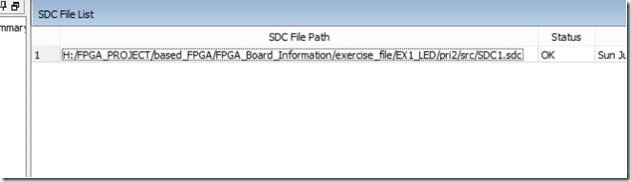

建立完约束之后,开始读取SDC文件,关于读取SDC有两种方法,(1)可以在setting中进行设置,如下图所示。

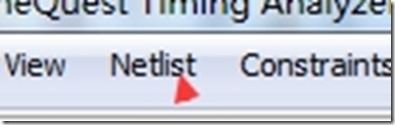

(2)也可以在timequest中进行文件的读取,在timequest界面下点击constraints----read sdc file 即可,如下图所示。

2.4 更新网表别列出时序图

更新网表文件。然后 双击,就可以看到我们的约束内容

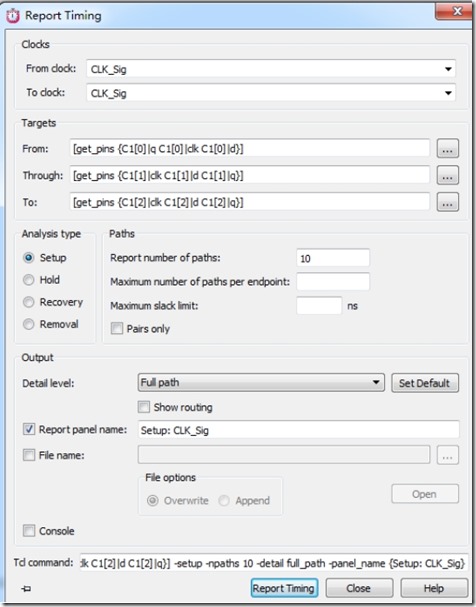

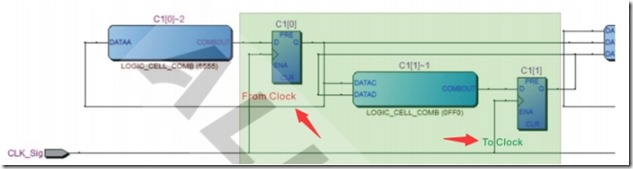

双击,就可以看到我们的约束内容 在此信号上,点击右键,就可以report timing,图16.6是报告时序的界面,第一个从源时钟到目的时钟,这个见图16.7,都会把与之相关联的寄存器节点牵扯进来。

在此信号上,点击右键,就可以report timing,图16.6是报告时序的界面,第一个从源时钟到目的时钟,这个见图16.7,都会把与之相关联的寄存器节点牵扯进来。

图16.6 操作界面

对于上图中的from clock和 to clock ,只要给定一个参数即可,就会把与之时钟相关连的牵扯进来。

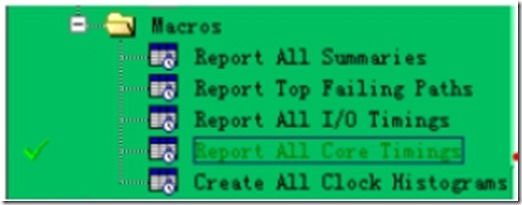

![]() 同时也需要注意,这里的路径数目,如果节点数比较多,那么需要改动这里的路径数目,去分析各路径数目之间的关系。或者也可以双击下图所示的命令,

同时也需要注意,这里的路径数目,如果节点数比较多,那么需要改动这里的路径数目,去分析各路径数目之间的关系。或者也可以双击下图所示的命令,

不过此方法只能实现1000个路径的分析,如果想要更改,还需手动去更改TCL脚本文件,![]()

将1000改成比较大的数,以便完成更多的路径分析。

图 16.7 寄存器相关节点图

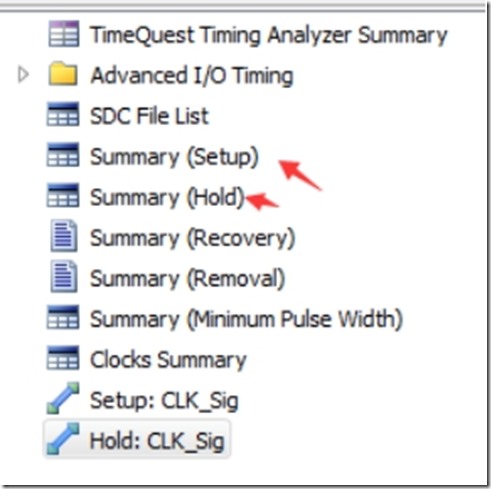

在这里可以去查看建立和保持余量是否符合要求,如下图16.8所示。

图16.8 余量查看

那么timequest的目的是告诉硬件,让你对某个信号加以约束,对于给定的不同的网表形式,所给的余量也是不同的,最坏情况比给最好情况给定的余量较多。Fmax,最高频率,此频率大小是评估走线最长情况的时钟,也是延迟最大的走线,所能够达到的最大频率,一般希望Fmax越大越好。

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================