验证公式正确性

前两篇博客提及了关于时序的建立余量和保持余量的计算。结合实际情况,验证公式的运算正确性。结合之前博客提及的LED实验,看一下建立余量和保持余量是否都合格。

建立余量

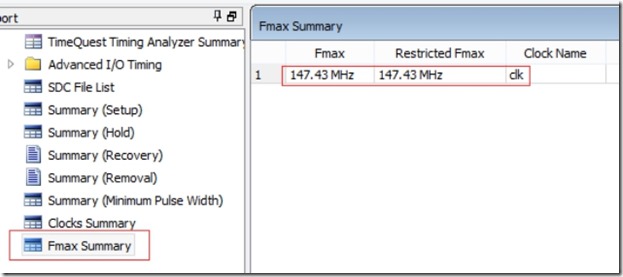

图1是最大时钟频率,可以看到完全满足时钟频率要求,高于主时钟运行频率。

图1 最大时钟频率

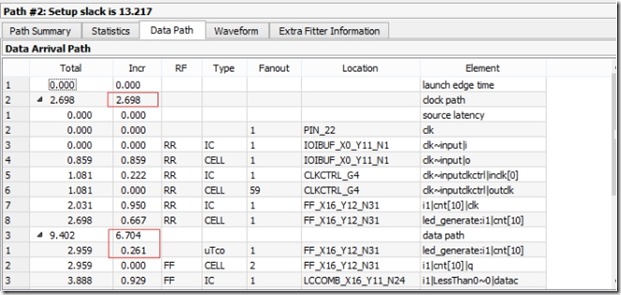

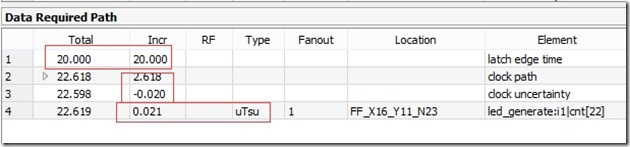

图2所示建立余量的是时序图,首先看到建立余量是13.217,大于0,完全满足数据信号和时钟信号之间的建立时间关系。其中上升沿时间(launch edge time)为0ns,源时钟达到寄存器(Tclk1)的时间为2.698ns,Tco = 0.261ns,Tdata = (6.704 - 0.261) ns,所以数据到达时间 T_A_T = 0 + 2.698 + 0.261 + (6.704 - 0.261) =9.402ns ;对于数据要求时间 T_R_T = 20 +(2.618-0.020) - (-0.021) = 22.619ns,其中数据要求时间各参数可以参看图3所示,所以建立余量 = T_R_T - T_A_T = 13.217ns.

图 2 数据到达时间

图3 数据要求时间

保持余量

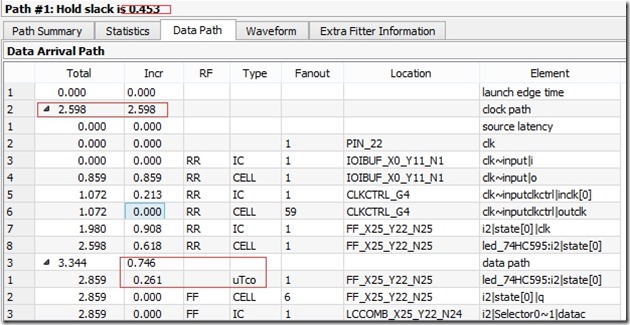

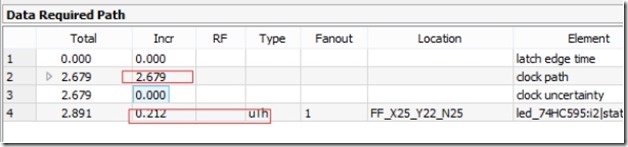

如图4所示,是保持余量相关的数据,可以看到保持余量是0.453,也是正值满足时序要求。从图中可以看到,其中上升沿时间(launch edge time)为0ns,源时钟达到寄存器(Tclk1)的时间为2.598ns,Tco = 0.261ns,Tdata = (0.746 - 0.261) ns,所以数据到达时间 T_A_T = 0 + 2.598 + 0.261 + (0.746 - 0.261) = 3.344ns;对于数据要求时间 T_R_T = 0+ 2.679+0.212 = 2.891ns,其中数据要求时间各参数可以参看图5所示,所以保持余量 = T_A_T - T_R_T = 0.453ns.

图4 数据到达时间

图5 数据要求时间

//=======================================================================

更多详细的资料下载可以登录笔者百度网盘:

网址:http://pan.baidu.com/s/1bnwLaqF

密码:fgtb

//=======================================================================