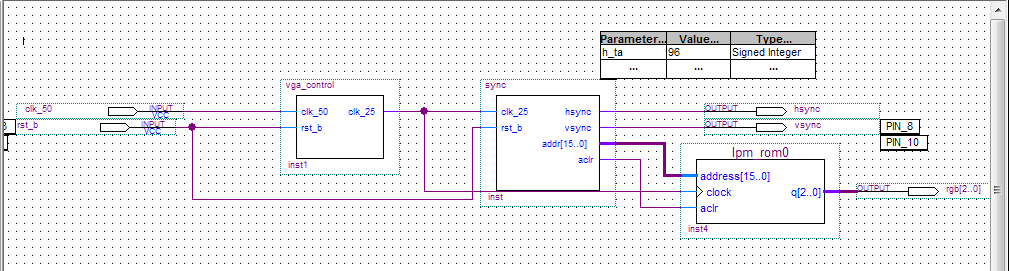

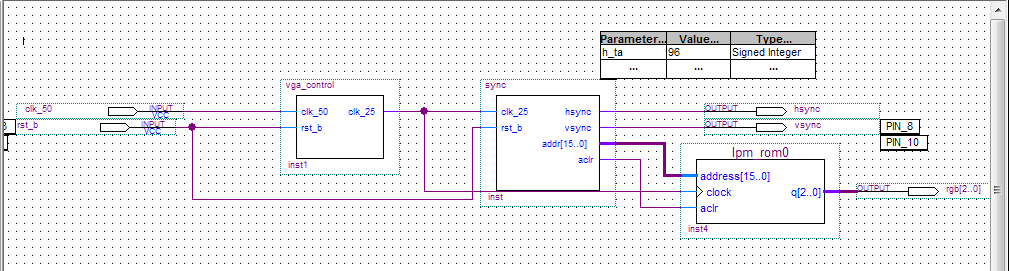

VGA的实现框架图

module sync

( clk_25,

rst_b,

hsync,

vsync,

addr,

aclr)

;

input clk_25;

input rst_b;

output hsync;

output vsync;

output[15:0]addr;

output aclr;

wire clk_25;

wire rst_b;

wire hsync;

wire vsync;

reg[15:0] addr;

reg hsync_n;

reg vsync_n;

reg aclr;

parameter h_ta = 96,h_tb=40,h_tc=8,h_td=640,h_te=8,h_tf=8,h_tg = 10'd800;//hsync时序要求

parameter v_ta = 2,v_tb=25,v_tc=8,v_td=480,v_te=8,v_tf=8,v_tg = 10'd525;//vsync时序要求

parameter h_picture = 165 , v_picture = 220;//图片的分辨率128*128

parameter h_valid_start = h_ta + h_tb + h_tc,h_valid_end =h_valid_start + h_td;//x最大有效数据区域144--784

parameter v_valid_start = v_ta + h_tb + v_tc,v_valid_end =v_valid_start + v_td;//x最大有效数据区域35--515

parameter x_start = h_valid_start+100,x_end = h_valid_start + h_picture+100;//x显示区域

parameter y_start = v_valid_start,y_end = v_valid_start + v_picture;//y显示区域

parameter addr_max = 36300;//最大内存空间

assign hsync = hsync_n;

assign vsync = vsync_n;

reg [9:0] hcnt_n;

reg [9:0]hcnt;

reg [9:0]vcnt;

always@(posedge clk_25 or negedge rst_b)

begin

if(!rst_b)

hcnt <= 10'd0;

else

hcnt <= hcnt_n;

end

always@(*)

begin

if(hcnt == h_tg-1'b1)

hcnt_n <= 10'd0;

else

hcnt_n <= hcnt + 1'b1;

end

always@(negedge hsync or negedge rst_b)

begin

if(!rst_b)

vcnt <= 10'd0;

else

if(vcnt == v_tg-1'b1)

vcnt <= 10'd0;

else

vcnt <= vcnt + 1'b1;

end

always@(posedge clk_25)

begin

if(hcnt < 10'd96)

hsync_n <= 1'b0;

else

hsync_n <= 1'b1;

end

always@(*)

begin

if(vcnt <10'd2)

vsync_n <= 1'b0;

else

vsync_n <= 1'b1;

end

always@(posedge clk_25 or negedge rst_b)

begin

if(!rst_b)

addr <= 16'd0;

else

if((hcnt>x_start - 1 && hcnt < x_end )&&(vcnt>y_start - 1 && vcnt < y_end ))

begin

addr <= addr + 1'b1;

aclr <= 1'b0;

end

else

if(addr ==addr_max)

begin

addr <= 0;

aclr <= 1'b1;

end

else

begin

addr <= addr;//10'd0;

aclr <= 1'b1;

end

end

endmodule