背景:

去年做项目的时候,由于有需要编译出多个可执行文件的需求,修改了Makefile使其支持生成多个结果(编译多个含有main函数的文件),但总觉得自己的实现不够完美。

今年又遇到这样需求的时候,可在网上找了一圈,发现没有找到能够同时编译得到多个结果的Makefile模板。

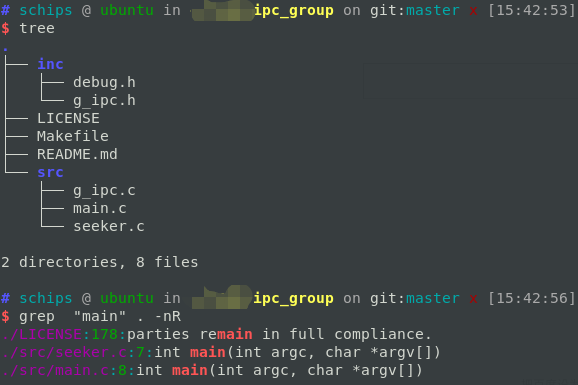

目录结构

可以发现,其中,seeker.c 以及 main.c 中都有 main函数,如果按照以往的编译方式,是会引起冲突的

如果将编译的文件写死而引起的不便又违背了make简洁的初衷,那么本人是怎么解决这样的问题的呢?

解决方法:

其实很简单,只需要

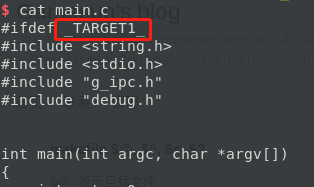

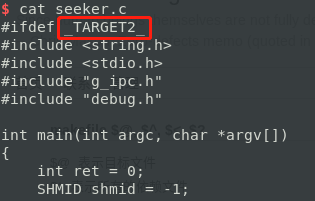

1.在包含main函数的.c文件中,头尾加上条件宏

2.在makefile中的编译规则中指定-D选项(条件编译)

这样一来,当make时,其他包含了main的宏由于条件编译而变成了空文件,自然便不会引起多重main函数编译冲突了。

源码:

以下是本人的makefile,希望各路大神批评指正。如果有更好的实现,请告知我,谢谢。

模板与demo的网址:https://gitee.com/schips/common_code_for_my_self/tree/master/makefile/makefile_for_apps

$ cat Makefile

# 添加所有的.c文件 SRCS = $(wildcard src/*.c) OBJS = $(SRCS:.c = .o) # 指定 头文件目录 INCLUDES = -I ./inc # 指定库目录 LIBS = -L ./lib # 指定编译器 CC = gcc # 指定编译选项(可选) CCFLAGS = -g -Wall -O0 # 编译目标列表 OUTPUT1 = target1 OUTPUT2 = target2 # ... OUTPUTLIST=$(OUTPUT1) $(OUTPUT2)

# 将 所有的目标作为一个列表,便于make clean all : $(OUTPUTLIST) # 编译目标1 $(OUTPUT1) : $(OBJS) @$(CC) $^ -o $@ $(INCLUDES) $(LIBS) -D_$(shell echo $(@)|tr a-z A-Z)_ $(OUTPUT2) : $(OBJS) @$(CC) $^ -o $@ $(INCLUDES) $(LIBS) -D_$(shell echo $(@)|tr a-z A-Z)_ %.o : %.c @$(CC) -c $< $(CCFLAGS) clean: @rm $(OUTPUTLIST) .PHONY:clean

注:红色的处只是为了使得宏与OUTPUTx的名字保持一致,且不是小写形式(习惯上,宏使用大写),这样一来就不需要修改过多的东西就很方便了。

其他:

项目中使用到的2个带有main函数的文件头部(文件最后一行都是 #endif)