前面已经把DDR用app接口的方式控制住了,结果这个工程确要用microblaze。所以还要接到axi上。于是又来了一段苦逼的路程。

要用axi控制ddr,先得把接口给弄清楚了,各个接口干嘛的。把mig上的axi接口全部复制出来。再一个个的查

1 // ************************************************************************************** 2 // ***************************** MIG Interface ************************************ 3 // ************************************************************************************** 4 // output ui_clk, 5 // output ui_clk_sync_rst, 6 // output mmcm_locked, 7 // input aresetn, 8 // input app_sr_req, // assign 0 9 // input app_ref_req, // assign 0 10 // input app_zq_req, // assign 0 11 // output app_sr_active, 12 // output app_ref_ack, 13 // output app_zq_ack, 14 // Slave Interface Write Address Ports 15 input [3:0] s_axi_awid, //写地址信号组的标记 16 input [29:0] s_axi_awaddr, // **************** 写地址 17 input [7:0] s_axi_awlen, //猝发长度 18 input [2:0] s_axi_awsize, //猝发大小 19 input [1:0] s_axi_awburst,//猝发类型 20 input [0:0] s_axi_awlock,//锁类型 00 21 input [3:0] s_axi_awcache,//缓存类型 00 22 input [2:0] s_axi_awprot,//保护类型 00 23 input [3:0] s_axi_awqos, //优先级标志 0 24 input s_axi_awvalid,// *****************写地址有效 25 output s_axi_awready,// *****************写地址准备完成信号,可接收对方写地址操作 26 // Slave Interface Write Data Ports 27 input [511:0] s_axi_wdata, // ****************** 写数据 28 input [63:0] s_axi_wstrb,//WSTRB 写选通,对于数据总线的每8bit有一个写选通。1: active 29 input s_axi_wlast, // ****************** 猝发中写最后一个数据 30 input s_axi_wvalid, // ***************** 写数据有效信号 31 output s_axi_wready, // ***************** 写数据准备完成信号,可接收对方写数据操作 32 // Slave Interface Write Response Ports 33 input s_axi_bready, //表示可接收响应信号 34 output [3:0] s_axi_bid, // 响应ID 35 output [1:0] s_axi_bresp, // ******************* 写回应信号,2‘b00表示写成功 36 output s_axi_bvalid, // 表示所要求的写响应是可用的 37 // Slave Interface Read Address Ports 38 input [3:0] s_axi_arid, // 读地址ID 39 input [29:0] s_axi_araddr, // ********************* 读地址 40 input [7:0] s_axi_arlen, //猝发长度 41 input [2:0] s_axi_arsize, // 猝发大小 42 input [1:0] s_axi_arburst, //猝发类型 00:固定猝发,01:递增猝发 10:回卷猝发 43 input [0:0] s_axi_arlock, //锁类型 44 input [3:0] s_axi_arcache, //锁类型 45 input [2:0] s_axi_arprot, //保护类型 46 input [3:0] s_axi_arqos, // 优先级标志 47 input s_axi_arvalid, // ****************** 读地址有效 48 output s_axi_arready, // **************** 读地址准备信号 49 // Slave Interface Read Data Ports 50 input s_axi_rready, 51 output [3:0] s_axi_rid, 52 output [511:0] s_axi_rdata, 53 output [1:0] s_axi_rresp, // ********************* 读回应信号,2’b00 表示读成功 54 output s_axi_rlast, 55 output s_axi_rvalid, 56 // output init_calib_complete, 57 // output [11:0] device_temp, 58 59 // input sys_rst 60 61 62 /* 63 burst, //猝发类型 00:固定猝发,01:递增猝发 10:回卷猝发 64 回卷猝发必须满足 1,开始地址必须对齐传输大小。2猝发长度必须是2.4.8.16 。大于16拍的猝发传输只支持INCR递增类型 65 在example中 66 lock = 2'b0; 67 cache = 4'b0; 68 prot = 3'b0; 69 burst = 1 // lenth >16 采用递增型 70 size = 6 // data with/8=64 71 72 | arsize/awsize | bytes in transfer 73 |____________________|__________________ 74 | 000 | 1 75 | 001 | 2 76 | 010 | 4 77 | 011 | 8 78 | 100 | 16 79 | 101 | 32 80 | 110 | 64 81 | 111 | 128 82 |--------------------|------------------- 83 */

用 // ************ 注释的信号 表示很清楚这个信号的作用

只有 // 注释的信号 表示用法有些模糊。不过这些信号在example中都给出了基本用法。

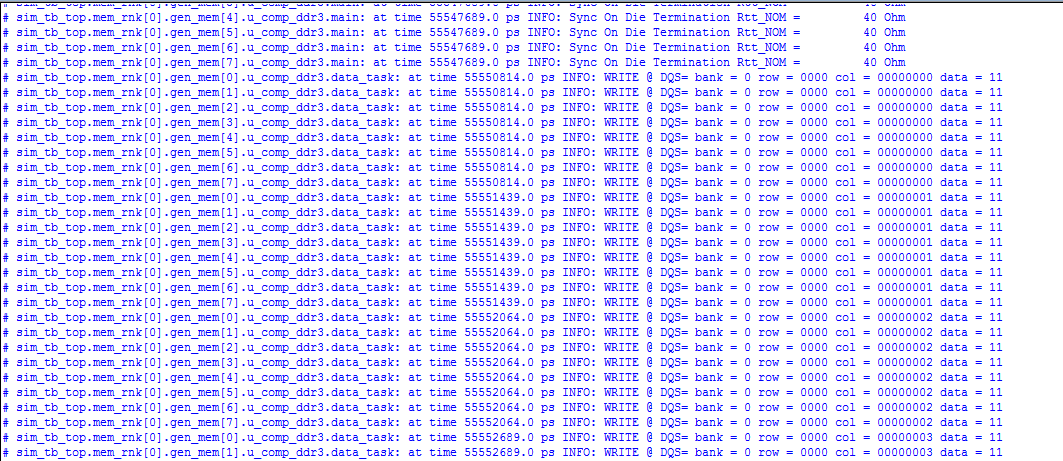

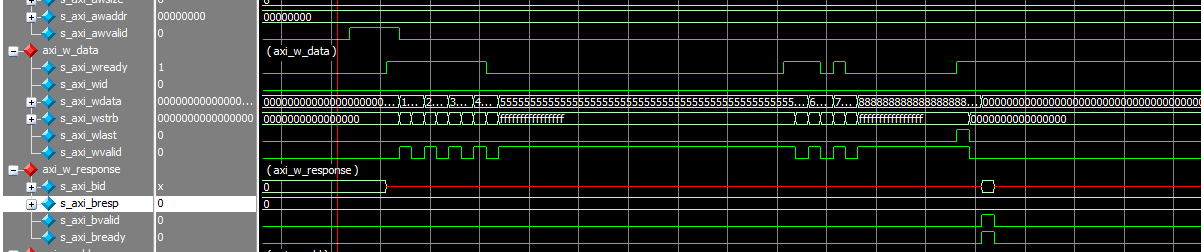

最后是实现了写操作。log中显示确实按照我的要求写进去了,地址数据都正确。可是效率真的太差了

还有一点就是如果你的len是7,那么你就要给它传7+1=8个数,axi总线才会给响应。 开始我的程序就是这样的len设定为8,传了8个数等响应,死等等不来。

代码中写8个数据。从0地址开始存。写8个数据中间需要休息这么久? 还是我控制的有问题啊。

考虑还要不要用axi了

欢迎加入: FPGA广东交流群:162664354

FPGA开发者联盟: 485678884