https://www.cnblogs.com/MAQI/p/7831156.html

PLL

时钟是时序逻辑的灵魂。

在实际应用中,时钟信号在频率或者相位上通常并不满足直接使用的需求,而内部时序逻辑又只能对时钟信号进行整数倍的分频,并且不能保证产生新时钟信号的相位稳定性,所以需要用到时钟管理单元对时钟和时序进行管理。

时钟管理单元可以对时钟信号进行高精度的倍频、分频和相位调整。FPGA中的时钟管理单元有两种:PLL(Phase Locked Loop, 锁相环)和DCM(Digital Colck Manager, 数字时钟管理员)。

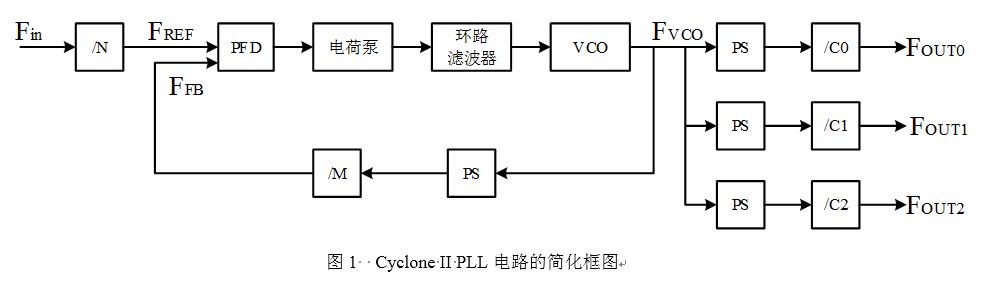

Altera FPGA Cyclone II PLL电路的简化框图如图1所示。包括一个PFD(相位-频率检测器)、一个电荷泵、一个环路滤波器、一个VCO(压控振荡器)和几个分频器以及PS(相位选择)电路。

PFD比较输入时钟和反馈时钟的相位,输出它们的差值。

电荷泵和环路滤波器将差值转换成电压。

VCO基于电压,产生更高或者更低的频率振荡,从而影响反馈时钟的相位和频率。

反馈机制最终迫使反馈时钟和参考时钟有相同的频率和相位,即锁相。

PLL中有几个分频器,通过调整分频器的值进行频率综合。

因为有PLL环路,所以FREF = FFB。因为FREF = Fin / N,FFB = FVCO / M,所以有FVCO = (M/N) Fin

输出时钟的频率是:FOUT0 = FVCO / C0 = (M/(N * C0)) Fin

也可以通过PS电路来调整输出时钟的相位。