1.前言

本文是对K64 datasheet 之ENET部分的功能描述,将对每个部分进行详细说明

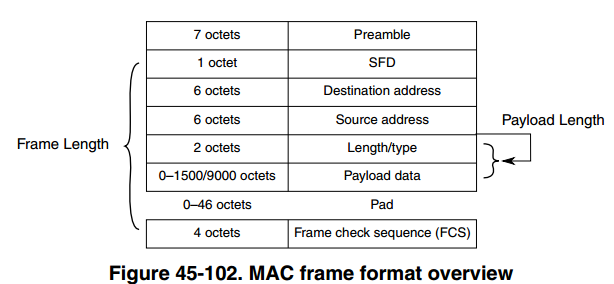

2.Ethernet MAC frame formats

- MAC帧组成格式

(1)7字节前导码:如按最低位先传则为0x55 0x55 0x55 0x55 0x55 0x55;

(2)起始帧定界符(SFD):如按最低位先传则为0XD5;

(3)2个地址域:包括源MAC地址和目的MAC地址;

(4)VLAN-tagged :可选,占4字节

(5)长度或类型域:代表有效负荷的长度或者类型,以太网802.3组帧为例,如果小于0X05DC(1500字节)则为长度信息,如果大于0X0600(1536字节)则为类型信息

常见的类型为:IPV4,ARP等

(6)有效载荷:最小为42 octets(带有VALAN-tagged),46 octets(不带有VALAN-tagged),最大载荷为1500 octets

(7)填充域:有效载荷不足42 octets(带有VALAN-tagged),46 octets(不带有VALAN-tagged),则填充

(8)CRC值:4字节循环冗余校验

注:

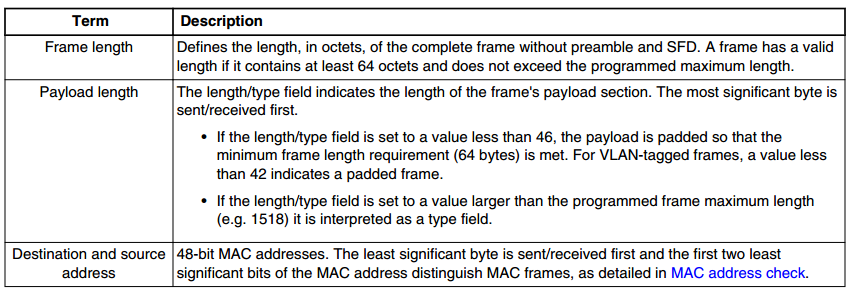

[1]帧长度不包括Preamble和SFD,帧最小长度为64字节,最大长度为1518字节

[2]除去 6 octets的 Destination address+6 octsts Source address+2 octets Length/type+4octets FCS = 18 octets,因此有效载荷需要至少46 octets,需填充0~46octets

[3]可选的是VLAN-tagged 可以插入到MACSource address和Length/type之间4字节,构成VLAN-tagged MAC 帧

- MAC帧定义

- Pause Frames

接收端产生一个pause frame指示当前传输遇到拥堵,发送端需要停止发送数据

- Magic packets

用于实现远程唤醒,当侦测到magic packet,主机会被唤醒

3.IP and higher layers frame format

举例来说IP数据报指定了Ethernet帧的有效负荷,TCP数据报又在IP数据报中指定了有效负荷

- Ethernet types

- IPv4 datagram format

- IPv6 datagram format

- Internet Control Message Protocol (ICMP) datagram format

- User Datagram Protocol (UDP) datagram format

- TCP datagram format

4. IEEE 1588 message formats

- Adjustable timer module

ENET时间戳时钟源既可以来自外部ENET_1588_CLKIN PAD ,也可以来自内部ENET PLL 。最好选择整形值如3ns产生精准计时

通过专用校准逻辑定时器被校准来同步远端master时钟作为本地系统的参考时钟

Adjustable timer implementation

- Transmit timestamping

- Receive timestamping

- Time synchronization

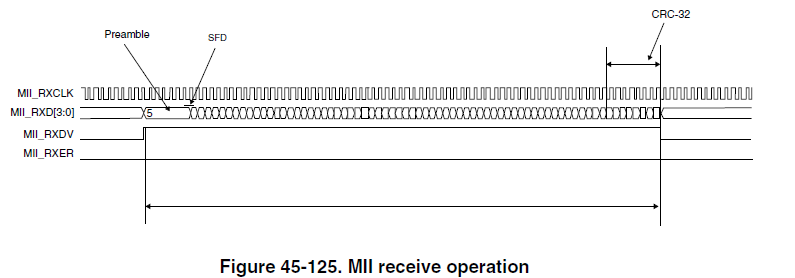

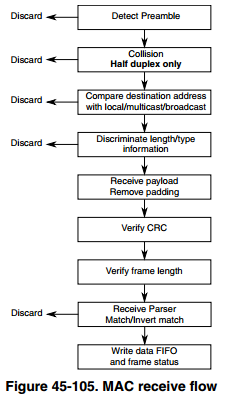

5. MAC receive

- Collision detection in half-duplex mode

- Preamble processing

MAC core允许任意长度的preample,也允许是0长度,如果preample后SFD的首个字节不是0x55也不是0xd5则丢弃

- MAC address check

目的地址bit0区分了不同的地址:

(1)If bit 0 is 0, the MAC address is an individual (unicast) address.

(2)If bit 0 is 1, the MAC address defines a group (multicast) address.

(3)If all 48 bits of the MAC address are set, it indicates a broadcast address.

- Frame length/type verification: payload length check

If the length/type is less than 0x600 and NLC is set, the MAC checks the payload length and reports any error in the frame status word and interrupt bit PLR

If the length/type is greater than or equal to 0x600, the MAC interprets the field as a type and no payload length check is performed

The length check is performed on VLAN and stacked VLAN frames. If a padded frame is received, no length check can be performed

- Frame length/type verification: frame length check

When the receive frame length exceeds MAX_FL bytes, the BABR interrupt is generated and the RxBD[LG] bit is set. - VLAN frames processing

VLAN frames have a length/type field set to 0x8100 immediately followed by a 16-Bit VLAN control information field.

- Pause frame termination

The receive engine terminates pause frames and does not transfer them to the receive FIFO

- CRC check

The CRC-32 field is checked and forwarded to the core FIFO interface if ENETn_RCR[CRCFWD] is cleared and ENETn_RCR[PADEN] is set

- Frame padding removal

- Recieve flushing

RX flushing prevents frames in the RX FIFO from being blocked

6 MAC transmit

- Frame payload padding

The IEEE specification defines a minimum frame length of 64 bytes

- MAC address insertion

- CRC-32 generation

- Inter-packet gap (IPG)

- Collision detection and handling — half-duplex operation only

A collision occurs on a half-duplex network when concurrent transmissions from two or more nodes take place.

7. Full-duplex flow control operation

8 Magic packet detection

Magic packet detection wakes a node that is put in power-down mode by the node management agent

9. IP accelerator functions

- Checksum calculation

The IP and ICMP, TCP, UDP checksums are calculated with one's complement arithmetic summing up 16-bit values

- Additional padding processing

- 32-bit Ethernet payload alignment

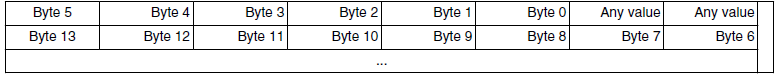

The data FIFOs allow inserting two additional arbitrary bytes in front of a frame. This extends the 14-byte Ethernet header to a 16-byte header, which leads to alignment of the

Ethernet payload

- IPv4 fragments

- IPv6 support

10. Resets and stop controls

- Hardware reset

- Soft reset

- Hardware freeze

- Graceful stop

During a graceful stop, any currently ongoing transactions are completed normally and no further frames are accepted

11 IEEE 1588 functions

- Adjustable timer module

- Transmit timestamping

- Receive timestamping

- Time synchronization

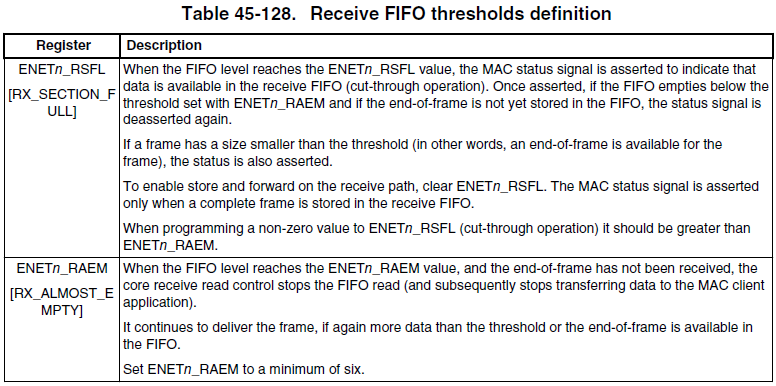

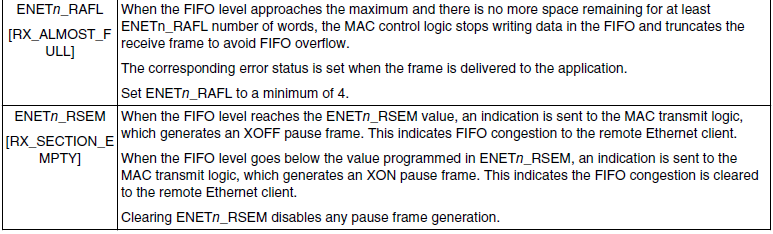

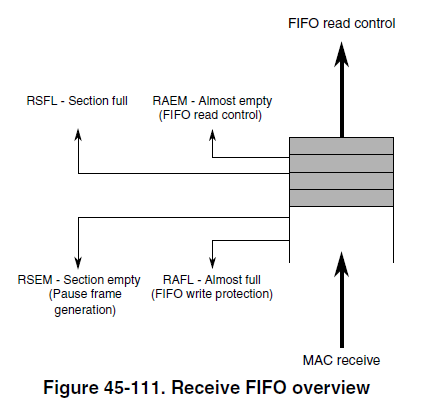

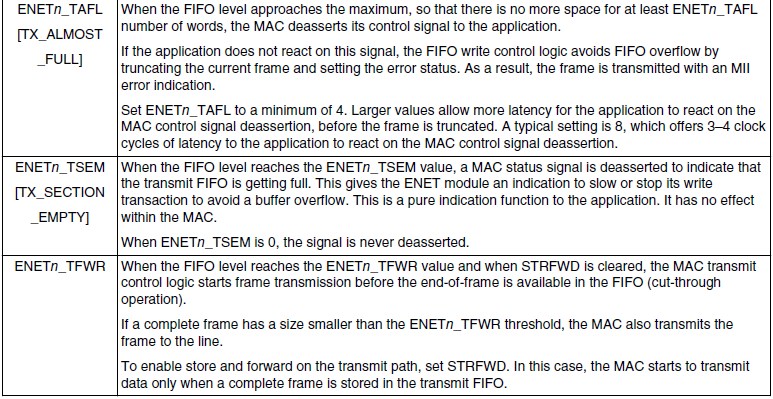

12 FIFO thresholds

- Receive FIFO

- Transmit FIFO

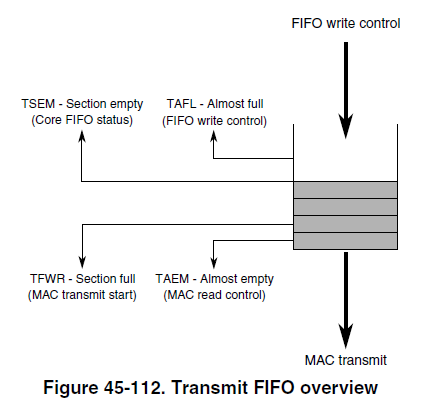

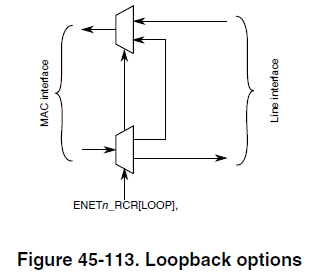

13 Loopback options

14 Legacy buffer descriptors

To support the Ethernet controller on previous Freescale devices, legacy FEC buffer descriptors are available

15 Enhanced buffer descriptors

This section provides a description of the enhanced operation of the driver/DMA via the buffer descriptors

16 Client FIFO application interface

The FIFO interface is completely asynchronous from the Ethernet line, and the transmit and receive interface can operate at a different clock rate

17 FIFO protection

- Transmit FIFO underflow

- Transmit FIFO overflow

- Receive FIFO overflow

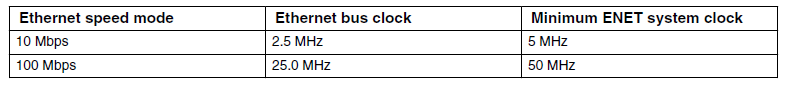

18 Reference clock

The input clocks to the ENET module must meet the specifications in the following table

19 PHY management interface

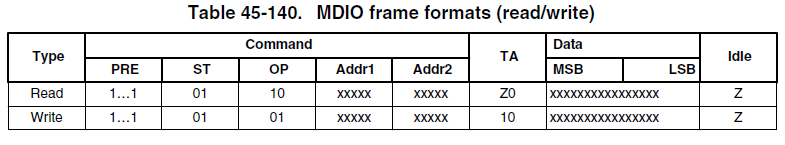

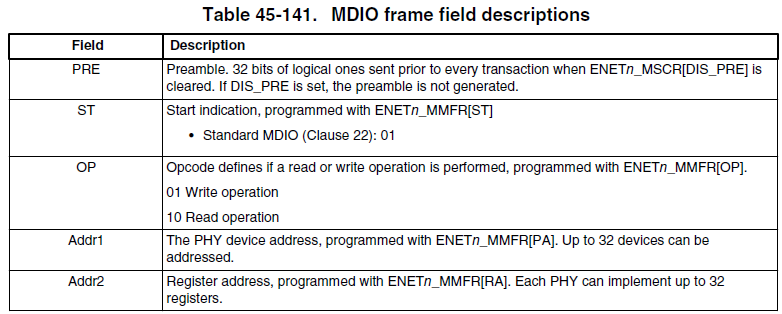

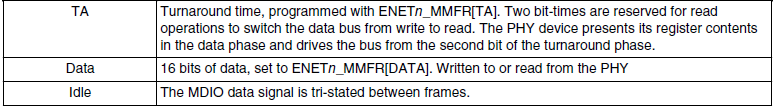

- MDIO frame format

- MDIO clock generation

The MDC clock is generated from the internal bus clock divided by the value programmed in ENETn_MSCR[MII_SPEED].

- MDIO operation

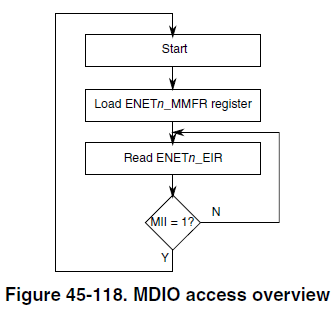

To perform an MDIO access, set the MDIO command register (ENETn_MMFR) according to the description provided in MII Management Frame Register (ENETn_MMFR).

To check when the programmed access completes, read the ENETn_EIR[MII] field.

20 Ethernet interfaces

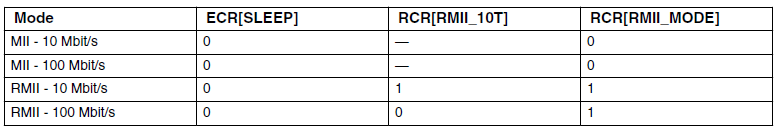

The following Ethernet interfaces are implemented:

-Fast Ethernet MII (Media Independent Interface)

-RMII 10/100 using interface converters/gaskets

The following table shows how to configure ENET registers to select each interface

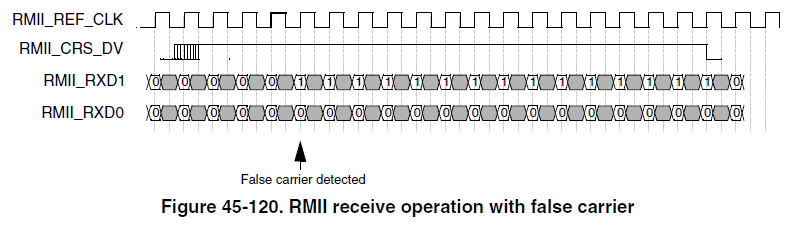

- RMII interface

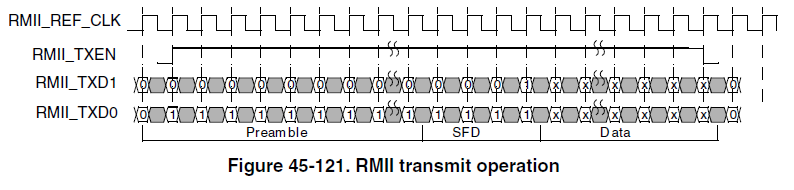

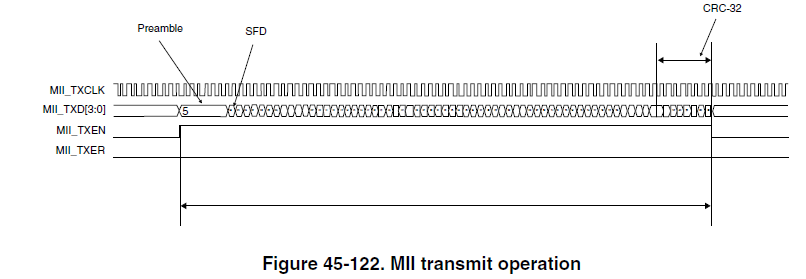

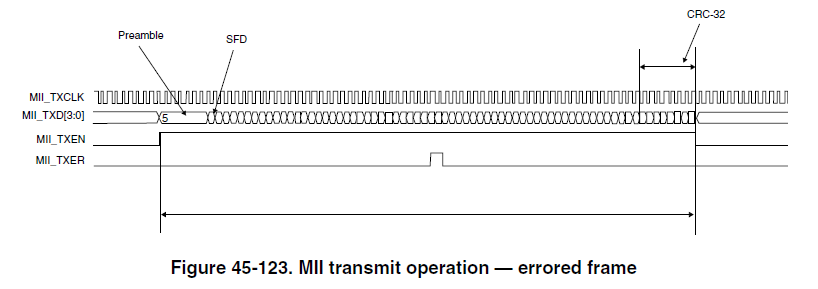

- MII Interface — transmit

MII interface — receive