基于Verilog HDL的数字时钟设计

一、实验内容:

利用FPGA实现数字时钟设计,附带秒表功能及时间设置功能。时间设置由开关S1和S2控制,分别是增和减。开关S3是模式选择:0是正常时钟显示;1是进入调分模式;2是进入调时模式;3是进入秒表模式,当进入秒表模式时,S1具有启动和停止功能,S2具有复位归零功能。只有四位数码管,所以没有做万年历,下一步会在这个基础上加入定时闹钟。

二、实验板

自个制作的实验板,用的是Altera CycloneIII EP3C40Q240C8N。上面的这块板是简单的外围电路,有流水灯、EEPROM、蜂鸣器、MAX3232、拨码开关、开关按键。PS2解码、VGA、AD转换等外围电路正在筹划中。

二、实验原理图设计

1、数码管原理图:利用74HC245驱动7段共阴极数码,其中F_X是代表接入到FPGA的I/O口。

2、开关原理图

三、整体架构设计

1、模块结构

2、RTL Viewer

四、各个击破

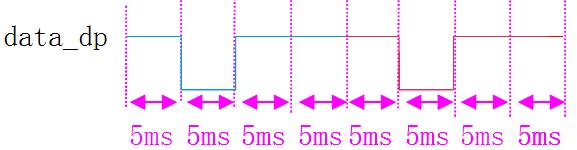

第1步:数码管显示,四位数码管的a~g、dp都是复用的,得先让四位数码管能分别显示不同的数据。大家都应该想到了“同步动态扫描”。我是这样做的:每位数码工作5ms,并采取流水方式进行循环操作(列扫描),每位数码即将工作那一刻,同时给a~g送入数据,数据保留5ms并进行定时更新数据(行扫描),行与列保持同步。定时开关,定时发送数据。下图有点错误,其实是在低电平是有效的,高低电平反了。

第2步:小数点显示,为了与时钟显示格式更为逼真,让中间的小数点一直亮着(充分利用资源吧),其他小数点要灭掉,很不幸运,不能直接把data_dp管脚直接拉高或拉低,这里是给该管脚产生周期为20ms,占空比为3/4的一个时钟信号,下图高低电平反了。

第3步:要让不同数码显示不同数据,那么就得事先编好每位数码管要显示的数据。由于时钟与秒表显示的最大数据不一样,得单独编码,这步很简单,一看代码就知道。

第4步:开关的信号输入,涉及到开关,那么就得消抖。这里借鉴特权的方法实现的。

把要做的实验思路搞清楚后,那么数字时钟设计应该很快就会完成。

五、各模块的信号输入/输出定义

|

Setting.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

add_in |

input |

开关S1的输入 |

|

sub_in |

input |

开关S2的输入 |

|

model_in |

input |

开关S3的输入 |

|

Hour_Ten |

output |

时的十位 |

|

Hour_One |

output |

时的个位 |

|

Minute_Ten |

output |

分的十位 |

|

Minute_One |

output |

分的个位 |

|

Display_Model |

output |

控制时钟与秒表的显示切换 |

|

M_Start |

output |

启动/停止秒表计数器 |

|

M_Reset |

output |

复位归零 |

|

control_wei.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

select_wei |

output |

控制数码管流水工作 |

|

miaobiao.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

M_Start |

input |

启动/停止秒表计数器 |

|

M_Reset |

input |

复位归零 |

|

S_data1 |

output |

秒表:第一位数码管数据编码 |

|

S_data2 |

output |

秒表:第二位数码管数据编码 |

|

S_data3 |

output |

秒表:第三位数码管数据编码 |

|

S_data4 |

output |

秒表:第四位数码管数据编码 |

|

control_display.v |

|||

|

Pin Name |

I/O |

Description |

|

|

clk |

input |

主时钟27MHZ |

|

|

rst_n |

input |

系统复位,低有效 |

|

|

H_data1 |

input |

时钟:第一位数码管数据 |

|

|

H_data2 |

|

时钟:第二位数码管数据 |

|

|

H_data3 |

input |

时钟:第三位数码管数据 |

|

|

H_data4 |

input |

时钟:第四位数码管数据 |

|

|

S_data1 |

input |

秒表:第一位数码管数据 |

|

|

S_data2 |

input |

秒表:第二位数码管数据 |

|

|

S_data3 |

input |

秒表:第三位数码管数据 |

|

|

S_data4 |

input |

秒表:第四位数码管数据 |

|

|

Display_Model |

input |

控制时钟与秒表的显示切换 |

|

|

data |

output |

送出7段a~g数据 |

|

|

data_dp |

output |

小数点 |

|

|

clock_top.v |

||

|

Pin Name |

I/O |

Description |

|

clk |

input |

主时钟27MHZ |

|

rst_n |

input |

系统复位,低有效 |

|

add_in |

input |

开关S1的输入 |

|

sub_in |

input |

开关S2的输入 |

|

model_in |

input |

开关S3的输入 |

|

data |

output |

送出7段a~g数据 |

|

select_wei |

output |

控制数码管流水工作 |

|

data_dp |

output |

小数点 |

六:代码的实现

control_wei.v

1 /***********************************************/ 2 //四位数码管进行流水控制,每位数码管工作5MS 3 /***********************************************/ 4 module control_wei( 5 clk, 6 rst_n, 7 select_wei, 8 ); 9 input clk; 10 input rst_n; 11 output[3:0] select_wei; 12 13 /**********************************************/ 14 parameter T5MS = 18'd134_999; 15 /**********************************************/ 16 reg[3:0] select_wei; 17 reg[17:0] cnt; 18 always @(posedge clk or negedge rst_n) 19 if(!rst_n) cnt <= 18'd0; 20 else if(cnt == T5MS) 21 cnt <= 18'd0; 22 else 23 cnt <= cnt + 1'b1; 24 /**********************************************/ 25 //通过移位方式进行流水工作,定时开关 26 always @(posedge clk or negedge rst_n) 27 if(!rst_n) begin 28 select_wei <= 4'd7; 29 end 30 else if(cnt == T5MS) begin 31 if(select_wei == 4'd14) 32 select_wei <= 4'd7; 33 else 34 select_wei <= {1'b1,select_wei[3:1]}; 35 end 36 endmodule 37 38

setting.v

1 module setting( 2 //input 3 clk, 4 rst_n, 5 add_in,//增加按钮 6 sub_in,//减去按钮 7 model_in,//模式选择 8 9 //output 10 Hour_Ten, 11 Hour_One, 12 Minute_Ten, 13 Minute_One, 14 Display_Model, 15 M_Start, 16 M_Reset, 17 ); 18 input clk; 19 input rst_n; 20 input add_in; 21 input sub_in; 22 input model_in; 23 24 output [1:0] Hour_Ten; 25 output [3:0] Hour_One; 26 output [2:0] Minute_Ten; 27 output [3:0] Minute_One; 28 output Display_Model; 29 output M_Start; 30 output M_Reset; 31 32 /************************************/ 33 parameter T20MS = 20'd539_999; 34 parameter T1S = 25'd26_999_999; 35 parameter T60S = 31'd1_619_999_999; 36 /************************************************/ 37 //检测下降沿脉冲key_en = key_rst_r & (~key_rst); 38 //key_rst_r要晚一个时钟节拍才能得到key_rst的值 39 //key_rst在1变为0时,key_en置位 40 //key_rst 1 1 0 1 1 41 //key_rst_r 1 1 0 1 1 42 //~key_rst 0 0 1 0 0 43 //-------------------------- 44 //key_en 0 0 1 0 0 45 46 //检测上升沿脉冲key_en = (~key_rst_r) & key_rst; 47 //key_rst在0变为1时,key_en置位 48 //key_rst 0 0 1 0 0 49 //key_rst_r 0 0 1 0 0 50 51 //key_rst 0 0 1 0 0 52 //~key_rst_r 1 1 0 1 1 53 //-------------------------- 54 //key_en 0 0 1 0 0 55 /************************************************/ 56 reg[2:0] key_rst; 57 always @(posedge clk or negedge rst_n) 58 if(!rst_n) key_rst <= 3'b111; 59 else key_rst <= {add_in,sub_in,model_in}; 60 61 reg[2:0] key_rst_r; 62 always @(posedge clk or negedge rst_n) 63 if(!rst_n) key_rst_r <= 3'b111; 64 else key_rst_r <= key_rst; 65 66 wire[2:0] key_en; 67 assign key_en = key_rst_r & (~key_rst); 68 /************************************************/ 69 //按键消抖动 70 /************************************************/ 71 reg[19:0] cnt; 72 always @(posedge clk or negedge rst_n) 73 if(!rst_n) cnt <= 20'd0; 74 else if(key_en) cnt <= 20'd0; 75 else cnt <= cnt + 1'b1; 76 //每隔20ms就取按键上的值 77 reg[2:0] pin_status; 78 always @(posedge clk or negedge rst_n) 79 if(!rst_n) pin_status <= 3'b111; 80 else if(cnt == T20MS) pin_status <= {add_in,sub_in,model_in}; 81 82 reg[2:0] pin_status_r; 83 always @(posedge clk or negedge rst_n) 84 if(!rst_n) pin_status_r <= 3'b111; 85 else pin_status_r <= pin_status; 86 //前20MS的值与后20MS的值 87 wire[2:0] pin_status_ctrl; 88 assign pin_status_ctrl = pin_status_r & (~pin_status); 89 90 /**************************************************************************************************/ 91 //60S计数器 92 reg [30:0] cnt60s; 93 always @(posedge clk or negedge rst_n) 94 if(!rst_n) cnt60s <= 31'd0; 95 else if((cnt60s == T60S) || (!isCount)) cnt60s <= 31'd0; 96 else if(isCount) 97 cnt60s <= cnt60s + 1'b1; 98 /**************************************************************************************************/ 99 //模式控制 100 //00:时钟正常跑模式 101 //01:调分模式,在该模式时间计数器停止计数 102 //10: 调时模式,在该模式时间计数器停止计数 103 //11:秒表模式,在该模式时间计数器正常计数 104 reg[1:0] Time_model; 105 always @(posedge clk or negedge rst_n) 106 if(!rst_n) Time_model <= 2'b00; 107 else if(pin_status_ctrl[0]) 108 begin 109 if(Time_model == 2'b11) 110 Time_model <= 2'b00; 111 else 112 Time_model <= Time_model + 1'b1; 113 end 114 115 /************************************************/ 116 reg Display_Model;//时钟与秒表显示 117 reg isCount;//控制时间计数器 118 reg M_Start;//控制秒表计数器 119 reg M_Reset;//秒表复位 120 reg M_flag;//开关S1按第一次代表启动,紧接在按一次代表停止 121 reg [1:0] flag;//用来标志reg1是否到了2,到了2,reg2只能加到4 122 reg [1:0] reg1;//时的第一位:0~2 123 reg [3:0] reg2;//时的第二位:当第一位为0和1时,可以是0~9,当第一位为2时,只能是0~9, 124 reg [2:0] reg3;//分的第一位:只能是0~5 125 reg [3:0] reg4;//分的第二位:是0~9 126 always @(posedge clk or negedge rst_n) 127 if(!rst_n) begin 128 Display_Model <= 1'b0; 129 isCount <= 1'b0; 130 M_Start <= 1'b0; 131 M_Reset <= 1'b0; 132 M_flag <= 1'b0; 133 reg1 <= 2'd0; 134 reg2 <= 4'd0; 135 reg3 <= 3'd0; 136 reg4 <= 4'd0; 137 flag <= 2'd0; 138 end 139 else 140 case(Time_model) 141 //时钟正常开始跑 142 2'b00: 143 begin 144 Display_Model <= 1'b0; 145 isCount <= 1'b1;//启动计数 146 if(cnt60s == T60S) 147 begin 148 reg4 <= reg4 + 1'b1; 149 if(reg4 == 4'd9) 150 begin 151 reg4 <= 4'd0; 152 reg3 <= reg3 + 1'b1; 153 if(reg3 == 3'd5) 154 begin 155 reg3 <= 3'd0; 156 if(reg1 == 2'd2) 157 begin 158 reg2 <= reg2 + 1'b1; 159 if(reg2 == 4'd3) 160 begin 161 reg2 <= 4'd0; 162 reg1 <= 2'd0; 163 end 164 end 165 else 166 begin 167 reg2 <= reg2 + 1'b1; 168 if(reg2 == 4'd9) 169 begin 170 reg2 <= 4'd0; 171 reg1 <= reg1 + 1'b1; 172 end 173 end 174 end 175 176 end 177 end 178 end 179 180 //调分模式 181 2'b01: 182 begin 183 isCount <= 1'b1; 184 if(pin_status_ctrl[2])//加 185 begin 186 reg4 <= reg4 + 1'b1; 187 if(reg4 == 4'd9) 188 begin 189 reg4 <= 4'd0; 190 reg3 <= reg3 + 1'b1; 191 if(reg3 > 3'd5) 192 reg3 <= 3'd0; 193 end 194 end 195 else if(pin_status_ctrl[1])//减 196 begin 197 reg4 <= reg4 - 1'b1; 198 if(reg4 == 4'd0) 199 begin 200 reg4 <= 4'd9; 201 reg3 <= reg3 - 1'b1; 202 if(reg3 == 3'd5) 203 reg3 <= 3'd0; 204 end 205 end 206 end 207 208 //调时模式 209 2'b10: 210 begin 211 isCount <= 1'b1; 212 if(pin_status_ctrl[2])//加 213 begin 214 if(flag == 2'd2) 215 begin 216 reg2 <= reg2 + 1'b1; 217 if(reg2 >= 4'd3) 218 begin 219 reg2 <= 4'd0; 220 reg1 <= 2'd0; 221 flag <= 2'd0; 222 end 223 end 224 else 225 begin 226 reg2 <= reg2 + 1'b1; 227 if(reg2 == 4'd9) 228 begin 229 flag <= flag + 1'b1; 230 reg2 <= 4'd0; 231 reg1 <= reg1 + 1'b1; 232 if(reg1 == 2'd2) 233 begin 234 reg1 <= 2'd0; 235 end 236 end 237 end 238 end 239 else if(pin_status_ctrl[1])//减 240 begin 241 reg2 <= reg2 - 1'b1; 242 if(reg2 == 4'd0) 243 begin 244 reg2 <= 4'd9; 245 reg1 <= reg1 - 1'b1; 246 if(reg1 == 2'd2) 247 reg1 <= 2'd0; 248 end 249 end 250 end 251 252 2'b11:begin 253 isCount <= 1'b1;//时间计数还得继续接着跑 254 Display_Model <= 1'b1;//显示秒表 255 if(pin_status_ctrl[2])//启动秒表计数 256 begin 257 if(M_flag == 1'b1) begin 258 M_flag <= 1'b0; 259 M_Start <= 1'b0; 260 end 261 else begin 262 M_flag <= M_flag + 1'b1; 263 M_Start <= 1'b1; 264 M_Reset <= 1'b0; 265 266 end 267 end 268 else if(pin_status_ctrl[1])//复位并停止 269 begin 270 M_Start <= 1'b0; 271 M_flag <= 1'b0; 272 M_Reset <= 1'b1; 273 end 274 end 275 endcase 276 /************************************************/ 277 assign Hour_Ten = reg1; 278 assign Hour_One = reg2; 279 assign Minute_Ten = reg3; 280 assign Minute_One = reg4; 281 /************************************************/ 282 283 endmodule

control_data.v

1 module control_data( 2 //input 3 clk, 4 rst_n, 5 Hour_Ten, 6 Hour_One, 7 Minute_Ten, 8 Minute_One, 9 10 //output 11 H_data1, 12 H_data2, 13 H_data3, 14 H_data4 15 ); 16 input clk; 17 input rst_n; 18 input [1:0] Hour_Ten; 19 input [3:0] Hour_One; 20 input [2:0] Minute_Ten; 21 input [3:0] Minute_One; 22 output [6:0] H_data1; 23 output [6:0] H_data2; 24 output [6:0] H_data3; 25 output [6:0] H_data4; 26 /***********************************/ 27 parameter SEG_NUM0 = 7'h3f,//c0, 28 SEG_NUM1 = 7'h06,//f9, 29 SEG_NUM2 = 7'h5b,//a4, 30 SEG_NUM3 = 7'h4f,//b0, 31 SEG_NUM4 = 7'h66,//99, 32 SEG_NUM5 = 7'h6d,//92, 33 SEG_NUM6 = 7'h7d,//82, 34 SEG_NUM7 = 7'h07,//F8, 35 SEG_NUM8 = 7'h7f,//80, 36 SEG_NUM9 = 7'h6f;//90, 37 /***********************************/ 38 //时钟数据编码 39 /***********************************/ 40 //数码管一要显示的列表数据(0~2) 41 reg [6:0] data1_temp; 42 always @(posedge clk or negedge rst_n) 43 if(!rst_n) 44 data1_temp <= 7'h3f; 45 else 46 case(Hour_Ten) 47 2'd0: data1_temp <= SEG_NUM0; 48 2'd1: data1_temp <= SEG_NUM1; 49 2'd2: data1_temp <= SEG_NUM2; 50 default: data1_temp <= SEG_NUM0; 51 endcase 52 /***********************************/ 53 //数码管二要显示的列表数据(0~9) 54 reg [6:0] data2_temp; 55 always @(posedge clk or negedge rst_n) 56 if(!rst_n) 57 data2_temp <= 7'h3f; 58 else 59 case(Hour_One) 60 4'd0: data2_temp <= SEG_NUM0; 61 4'd1: data2_temp <= SEG_NUM1; 62 4'd2: data2_temp <= SEG_NUM2; 63 4'd3: data2_temp <= SEG_NUM3; 64 4'd4: data2_temp <= SEG_NUM4; 65 4'd5: data2_temp <= SEG_NUM5; 66 4'd6: data2_temp <= SEG_NUM6; 67 4'd7: data2_temp <= SEG_NUM7; 68 4'd8: data2_temp <= SEG_NUM8; 69 4'd9: data2_temp <= SEG_NUM9; 70 default: data2_temp <= SEG_NUM0; 71 endcase 72 /***********************************/ 73 //数码管三要显示的列表数据 (0~5) 74 reg [6:0] data3_temp; 75 always @(posedge clk or negedge rst_n) 76 if(!rst_n) 77 data3_temp <= 7'h3f; 78 else 79 case(Minute_Ten) 80 3'd0: data3_temp <= SEG_NUM0; 81 3'd1: data3_temp <= SEG_NUM1; 82 3'd2: data3_temp <= SEG_NUM2; 83 3'd3: data3_temp <= SEG_NUM3; 84 3'd4: data3_temp <= SEG_NUM4; 85 3'd5: data3_temp <= SEG_NUM5; 86 default: data3_temp <= SEG_NUM0; 87 endcase 88 /***********************************/ 89 //数码管四要显示的列表数据(1~9) 90 reg [6:0] data4_temp; 91 always @(posedge clk or negedge rst_n) 92 if(!rst_n) 93 data4_temp <= 7'h3f; 94 else 95 case(Minute_One) 96 4'd0: data4_temp <= SEG_NUM0; 97 4'd1: data4_temp <= SEG_NUM1; 98 4'd2: data4_temp <= SEG_NUM2; 99 4'd3: data4_temp <= SEG_NUM3; 100 4'd4: data4_temp <= SEG_NUM4; 101 4'd5: data4_temp <= SEG_NUM5; 102 4'd6: data4_temp <= SEG_NUM6; 103 4'd7: data4_temp <= SEG_NUM7; 104 4'd8: data4_temp <= SEG_NUM8; 105 4'd9: data4_temp <= SEG_NUM9; 106 default: data4_temp <= SEG_NUM0; 107 endcase 108 /*****************************************/ 109 assign H_data1 = data1_temp; 110 assign H_data2 = data2_temp; 111 assign H_data3 = data3_temp; 112 assign H_data4 = data4_temp; 113 /*****************************************/ 114 endmodule

control_display.v

1 module control_display( 2 //input 3 clk, 4 rst_n, 5 H_data1, 6 H_data2, 7 H_data3, 8 H_data4, 9 10 S_data1, 11 S_data2, 12 S_data3, 13 S_data4, 14 15 Display_Model, 16 17 //output 18 data, 19 data_dp 20 ); 21 input clk; 22 input rst_n; 23 //时钟模式要显示数据 24 input [6:0] H_data1; 25 input [6:0] H_data2; 26 input [6:0] H_data3; 27 input [6:0] H_data4; 28 //秒表模式要显示数据 29 input [6:0] S_data1; 30 input [6:0] S_data2; 31 input [6:0] S_data3; 32 input [6:0] S_data4; 33 input Display_Model;//0:时钟模式,1:秒表模式 34 35 output [6:0] data;//不包括小数点 36 output data_dp; 37 /******************************************/ 38 parameter T5MS = 18'd134_999; 39 parameter T10MS = 19'd269_999; 40 parameter T20MS = 20'd539_999; 41 /****************************************************************/ 42 reg [19:0]cnt_ms; 43 always @(posedge clk or negedge rst_n) 44 if(!rst_n) 45 cnt_ms <= 20'd0; 46 else if(cnt_ms == T20MS) 47 cnt_ms <= 20'd0; 48 else 49 cnt_ms <= cnt_ms + 1'b1; 50 51 /****************************************************************/ 52 //小数点显示 53 reg [1:0] i; 54 reg data_dp; 55 always @(posedge clk or negedge rst_n) 56 if(!rst_n) 57 i <= 2'd0; 58 else 59 case(i) 60 2'd0: 61 if(cnt_ms != T5MS) 62 data_dp = 1'b0; 63 else begin 64 data_dp= 1'b1; 65 i <= i + 1'b1; 66 end 67 68 2'd1: 69 if(cnt_ms != T10MS) 70 data_dp = 1'b1; 71 else begin 72 data_dp <= 1'b0; 73 i <= i + 1'b1; 74 end 75 76 2'd2: 77 if(cnt_ms != T20MS) 78 data_dp <= 1'b0; 79 else 80 i <= 4'd0; 81 endcase 82 /******************************************/ 83 //定时发送数据 84 reg [17:0] cnt; 85 reg [1:0] num;//每隔5MS,num加1 86 always @(posedge clk or negedge rst_n) 87 if(!rst_n) begin 88 cnt <= 18'd0; 89 num <= 2'd0; 90 end 91 else if(cnt == T5MS) begin 92 num <= num + 1'b1; 93 cnt <= 18'd0; 94 end 95 else 96 cnt <= cnt + 1'b1; 97 /******************************************/ 98 //通过Display_Model来确定是要送秒表数据还是时钟数据 99 reg [6:0] data_temp; 100 always @(posedge clk or negedge rst_n) 101 if(!rst_n) 102 data_temp <= 7'h3f; 103 else 104 case(num) 105 2'd0: data_temp <= Display_Model ? S_data1:H_data1;//给第一个数码管送数据 106 2'd1: data_temp <= Display_Model ? S_data2:H_data2;//给第二个数码管送数据 107 2'd2: data_temp <= Display_Model ? S_data3:H_data3;//给第二个数码管送数据 108 2'd3: data_temp <= Display_Model ? S_data4:H_data4;//给第二个数码管送数据 109 endcase 110 /******************************************/ 111 assign data = data_temp; 112 /******************************************/ 113 endmodule

miaobiao.v

1 module miaobiao( 2 //input 3 clk, 4 rst_n, 5 M_Start, 6 M_Reset, 7 8 //ouput 9 S_data1, 10 S_data2, 11 S_data3, 12 S_data4 13 ); 14 input clk; 15 input rst_n; 16 input M_Start;//控制秒表计数器 17 input M_Reset;//秒表复位 18 output [6:0] S_data1; 19 output [6:0] S_data2; 20 output [6:0] S_data3; 21 output [6:0] S_data4; 22 23 /************************************************************/ 24 parameter T_fenMiao = 19'd269_999; 25 parameter SEG_NUM0 = 7'h3f,//c0, 26 SEG_NUM1 = 7'h06,//f9, 27 SEG_NUM2 = 7'h5b,//a4, 28 SEG_NUM3 = 7'h4f,//b0, 29 SEG_NUM4 = 7'h66,//99, 30 SEG_NUM5 = 7'h6d,//92, 31 SEG_NUM6 = 7'h7d,//82, 32 SEG_NUM7 = 7'h07,//F8, 33 SEG_NUM8 = 7'h7f,//80, 34 SEG_NUM9 = 7'h6f;//90, 35 /************************************************************/ 36 //分秒计数器 37 reg [18:0] Cnt_FenMiao; 38 always @(posedge clk or negedge rst_n) 39 if(!rst_n) Cnt_FenMiao <= 19'd0; 40 else if((Cnt_FenMiao == T_fenMiao) || (!M_Start)) Cnt_FenMiao <= 19'd0; 41 else if(M_Start) 42 Cnt_FenMiao <= Cnt_FenMiao + 1'b1; 43 /************************************************************/ 44 //分秒向秒进位 45 reg [2:0] reg1; 46 reg [3:0] reg2; 47 reg [3:0] reg3; 48 reg [3:0] reg4; 49 always @(posedge clk or negedge rst_n) 50 if(!rst_n) begin 51 reg1 <= 3'd0; 52 reg2 <= 4'd0; 53 reg3 <= 4'd0; 54 reg4 <= 4'd0; 55 end 56 else if(M_Reset) begin 57 reg1 <= 3'd0; 58 reg2 <= 4'd0; 59 reg3 <= 4'd0; 60 reg4 <= 4'd0; 61 end 62 else if(Cnt_FenMiao == T_fenMiao) 63 begin 64 if(reg4 == 4'd9) begin 65 reg4 <= 4'd0; 66 if(reg3 == 4'd9) begin 67 reg3 <= 4'd0; 68 if(reg2 == 4'd9) begin 69 reg2 <= 4'd0; 70 if(reg1 == 3'd5) 71 reg1 <= 3'd0; 72 else reg1 <= reg1 + 1'b1; 73 end 74 else 75 reg2 <= reg2 + 1'b1; 76 end 77 else 78 reg3 <= reg3 + 1'b1; 79 end 80 else 81 reg4 <= reg4 + 1'b1; 82 end 83 /************************************************************/ 84 //数据编码 85 /************************************************************/ 86 //数码管一要显示的列表数据(0~5) 87 reg [6:0] S_data1_temp; 88 always @(posedge clk or negedge rst_n) 89 if(!rst_n) S_data1_temp <= 7'h3f; 90 else 91 case(reg1) 92 3'd0: S_data1_temp <= SEG_NUM0; 93 3'd1: S_data1_temp <= SEG_NUM1; 94 3'd2: S_data1_temp <= SEG_NUM2; 95 3'd3: S_data1_temp <= SEG_NUM3; 96 3'd4: S_data1_temp <= SEG_NUM4; 97 3'd5: S_data1_temp <= SEG_NUM5; 98 default: S_data1_temp <= SEG_NUM0; 99 endcase 100 /***********************************/ 101 //数码管二要显示的列表数据(0~9) 102 reg [6:0] S_data2_temp; 103 always @(posedge clk or negedge rst_n) 104 if(!rst_n) S_data2_temp <= 7'h3f; 105 else 106 case(reg2) 107 4'd0: S_data2_temp <= SEG_NUM0; 108 4'd1: S_data2_temp <= SEG_NUM1; 109 4'd2: S_data2_temp <= SEG_NUM2; 110 4'd3: S_data2_temp <= SEG_NUM3; 111 4'd4: S_data2_temp <= SEG_NUM4; 112 4'd5: S_data2_temp <= SEG_NUM5; 113 4'd6: S_data2_temp <= SEG_NUM6; 114 4'd7: S_data2_temp <= SEG_NUM7; 115 4'd8: S_data2_temp <= SEG_NUM8; 116 4'd9: S_data2_temp <= SEG_NUM9; 117 default: S_data2_temp <= SEG_NUM0; 118 endcase 119 /*****************************************/ 120 //数码管三要显示的列表数据(0~9) 121 reg [6:0] S_data3_temp; 122 always @(posedge clk or negedge rst_n) 123 if(!rst_n) S_data3_temp <= 7'h3f; 124 else 125 case(reg3) 126 4'd0: S_data3_temp <= SEG_NUM0; 127 4'd1: S_data3_temp <= SEG_NUM1; 128 4'd2: S_data3_temp <= SEG_NUM2; 129 4'd3: S_data3_temp <= SEG_NUM3; 130 4'd4: S_data3_temp <= SEG_NUM4; 131 4'd5: S_data3_temp <= SEG_NUM5; 132 4'd6: S_data3_temp <= SEG_NUM6; 133 4'd7: S_data3_temp <= SEG_NUM7; 134 4'd8: S_data3_temp <= SEG_NUM8; 135 4'd9: S_data3_temp <= SEG_NUM9; 136 default: S_data3_temp <= SEG_NUM0; 137 endcase 138 /***********************************/ 139 //数码管四要显示的列表数据(0~9) 140 reg [6:0] S_data4_temp; 141 always @(posedge clk or negedge rst_n) 142 if(!rst_n) S_data4_temp <= 7'h3f; 143 else 144 case(reg4) 145 4'd0: S_data4_temp <= SEG_NUM0; 146 4'd1: S_data4_temp <= SEG_NUM1; 147 4'd2: S_data4_temp <= SEG_NUM2; 148 4'd3: S_data4_temp <= SEG_NUM3; 149 4'd4: S_data4_temp <= SEG_NUM4; 150 4'd5: S_data4_temp <= SEG_NUM5; 151 4'd6: S_data4_temp <= SEG_NUM6; 152 4'd7: S_data4_temp <= SEG_NUM7; 153 4'd8: S_data4_temp <= SEG_NUM8; 154 4'd9: S_data4_temp <= SEG_NUM9; 155 default: S_data4_temp <= SEG_NUM0; 156 endcase 157 /*******************************************************/ 158 assign S_data1 = S_data1_temp; 159 assign S_data2 = S_data2_temp; 160 assign S_data3 = S_data3_temp; 161 assign S_data4 = S_data4_temp; 162 /*******************************************************/ 163 endmodule

clock_top

1 module clock_top( 2 //input 3 clk, 4 rst_n, 5 add_in, 6 sub_in, 7 model_in, 8 9 //output 10 data, 11 select_wei, 12 data_dp, 13 ); 14 input clk; 15 input rst_n; 16 input add_in; 17 input sub_in; 18 input model_in; 19 20 output [6:0] data; 21 output [3:0] select_wei; 22 output data_dp; 23 24 wire [1:0] Hour_Ten; 25 wire [3:0] Hour_One; 26 wire [2:0] Minute_Ten; 27 wire [3:0] Minute_One; 28 wire [6:0] H_data1,H_data2,H_data3,H_data4; 29 wire [6:0] S_data1,S_data2,S_data3,S_data4; 30 wire Display_Model; 31 wire M_Start; 32 wire M_Reset; 33 34 control_wei U1( 35 //input 36 .clk(clk), 37 .rst_n(rst_n), 38 39 //output 40 .select_wei(select_wei), 41 ); 42 43 setting U2( 44 //input 45 .clk(clk), 46 .rst_n(rst_n), 47 .add_in(add_in),//增加按钮 48 .sub_in(sub_in),//减去按钮 49 .model_in(model_in),//模式选择 50 51 //output 52 .Hour_Ten(Hour_Ten), 53 .Hour_One(Hour_One), 54 .Minute_Ten(Minute_Ten), 55 .Minute_One(Minute_One), 56 .Display_Model(Display_Model), 57 .M_Start(M_Start), 58 .M_Reset(M_Reset), 59 ); 60 61 control_data U3( 62 //input 63 .clk(clk), 64 .rst_n(rst_n), 65 .Hour_Ten(Hour_Ten),//from to U2 66 .Hour_One(Hour_One),//from to U2 67 .Minute_Ten(Minute_Ten),//from to U2 68 .Minute_One(Minute_One),//from to U2 69 70 //output 71 .H_data1(H_data1), 72 .H_data2(H_data2), 73 .H_data3(H_data3), 74 .H_data4(H_data4) 75 ); 76 77 control_display U4( 78 //input 79 .clk(clk), 80 .rst_n(rst_n), 81 .H_data1(H_data1),//from to U3 82 .H_data2(H_data2),//from to U3 83 .H_data3(H_data3),//from to U3 84 .H_data4(H_data4),//from to U3 85 .S_data1(S_data1),//from to U5 86 .S_data2(S_data2),//from to U5 87 .S_data3(S_data3),//from to U5 88 .S_data4(S_data4),//from to U5 89 .Display_Model(Display_Model),//from to U2 90 91 //output 92 .data(data), 93 .data_dp(data_dp) 94 ); 95 96 miaobiao U5( 97 //input 98 .clk(clk), 99 .rst_n(rst_n), 100 .M_Start(M_Start),//from to U2 101 .M_Reset(M_Reset),//from to U2 102 103 //ouput 104 .S_data1(S_data1), 105 .S_data2(S_data2), 106 .S_data3(S_data3), 107 .S_data4(S_data4), 108 ); 109 endmodule