一:verilog强度

1:概念

当一个线型由多个驱动时,才会有强度的概念;强度分为驱动强度和充电强度

2:驱动强度

分别为supply,strong,pull,weak,强度依次递减。

3:在进行RTL或者门级模型的设计时,只会用到强驱动(1,0,x)或者比weak还弱的驱动(z)。驱动强度只在如下的两种情况下才会被用到

(1)用连续赋值语句对一个线性进行赋值

(2)Verilog内建的原语逻辑门的门级输出(如and以及后面例子里使用的bufif1)

4:驱动强度必须以一对出现(high,low)

5:强度的语法是不可综合的

二:实验观察4种驱动强度之间的竞争

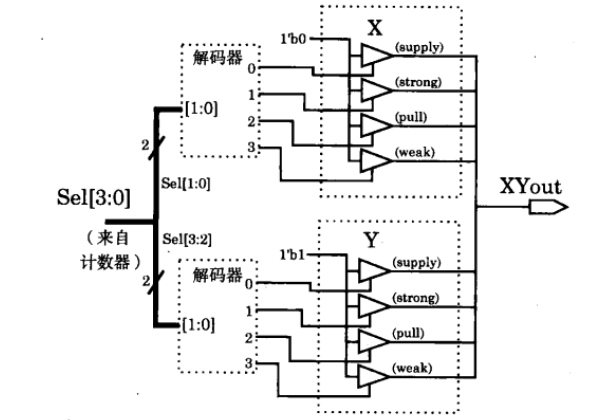

1:如图,共分为三个模块:计数器模块,解码器模块,三态缓冲器模块

2:计数器模块

使用上节的行为级计数器(参见verilog实战10之计数器)

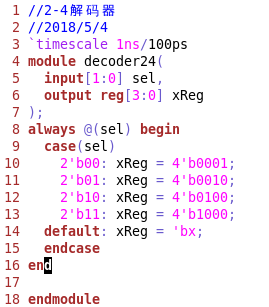

3:解码器模块

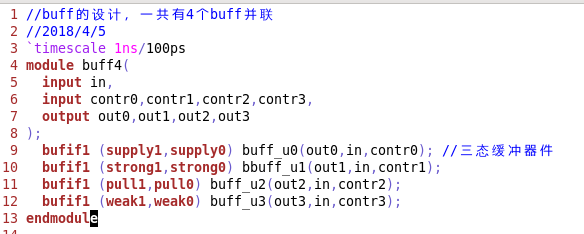

4:缓冲器模块(例化内建的逻辑门bufif1)

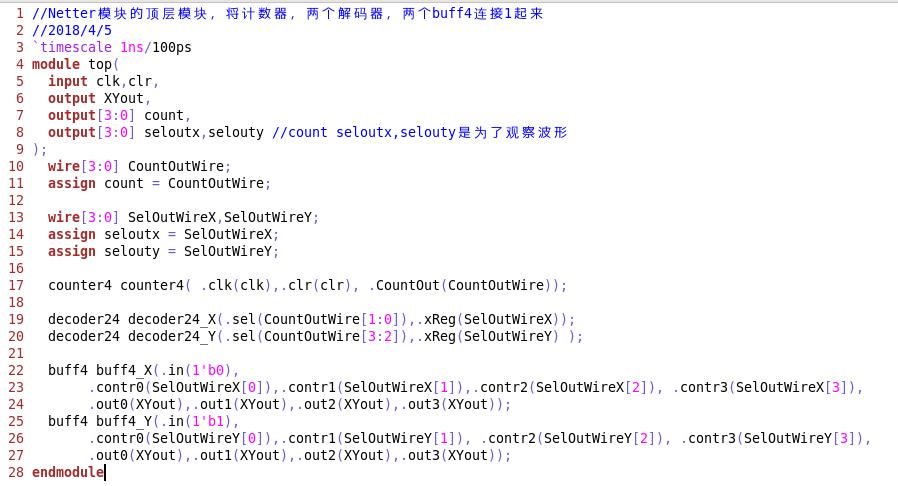

5:顶层设计

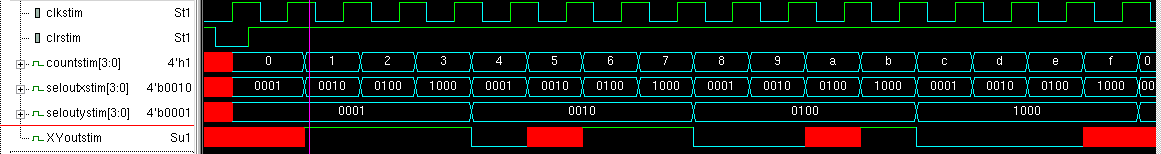

6:vcs dump波形

从波形分析可得:supply,strong,pull,weak强度依次下降。当X与Y输出强度一致时,输出不定,例如:计数在0,5,a时,X,Y强度一致,输出不定态。