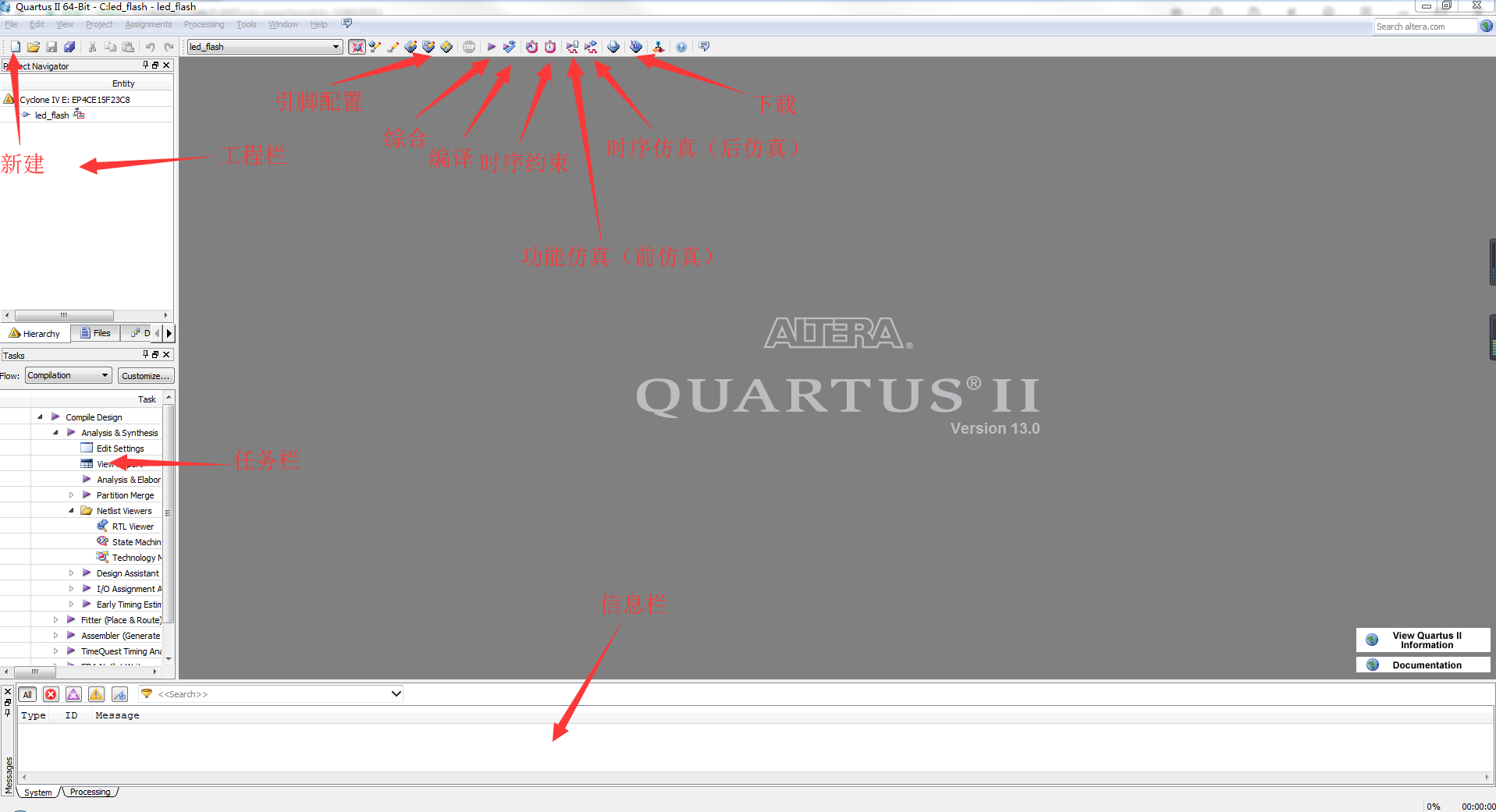

Quartus ii是针对Altera FPGA的一款EDA软件,在此以一个led闪烁工程来简单说一下基本操作:

一、注意事项

Quartus ii最大的注意事项就一点:工程名称以及工程里面的文件名称,都不能出现中文!

二、工程建立

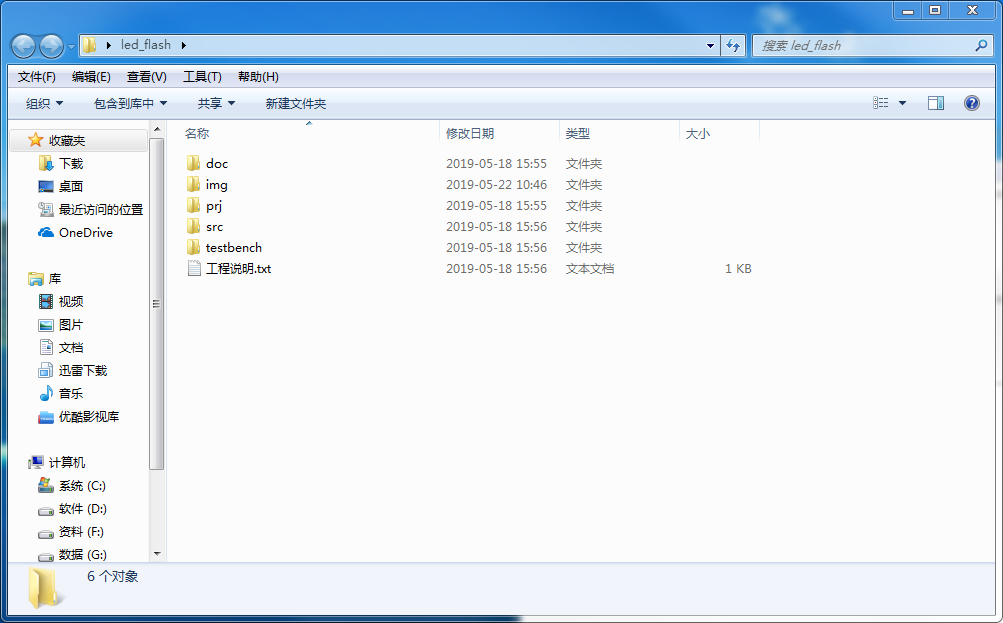

1.新建一个文件夹,并在里面按照自己习惯新建一些常用的文件夹,以后查看时会很方便。我的建立如下:

doc : 相关资料

img : 图片文件

prj : 工程文件

rtl : 代码文件

test : 测试文件

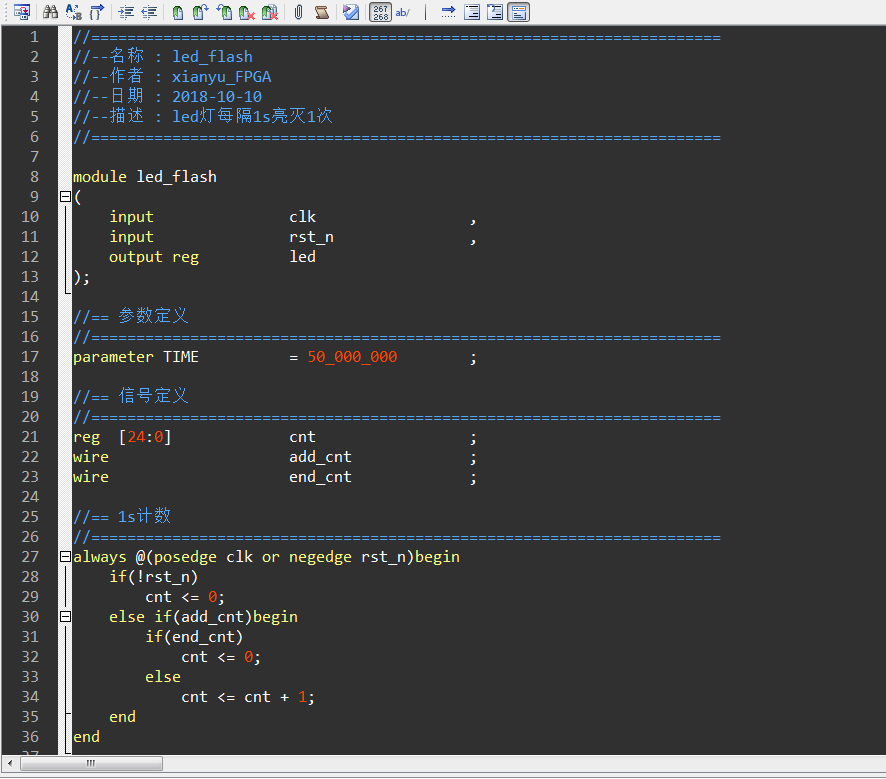

2.代码编写。因为quartus ii自带编译器不是很好用,建议用第三方编译器写好代码,再用quartus ii进行综合编译。

1 //====================================================================== 2 //--名称 : led_flash 3 //--作者 : xianyu_FPGA 4 //--日期 : 2018-10-10 5 //--描述 : led灯每隔1s亮灭1次 6 //====================================================================== 7 8 module led_flash 9 ( 10 input clk , 11 input rst_n , 12 output reg led 13 ); 14 15 //== 参数定义 16 //====================================================================== 17 parameter TIME = 50_000_000 ; 18 19 //== 信号定义 20 //====================================================================== 21 reg [24:0] cnt ; 22 wire add_cnt ; 23 wire end_cnt ; 24 25 //== 1s计数 26 //====================================================================== 27 always @(posedge clk or negedge rst_n)begin 28 if(!rst_n) 29 cnt <= 0; 30 else if(add_cnt)begin 31 if(end_cnt) 32 cnt <= 0; 33 else 34 cnt <= cnt + 1; 35 end 36 end 37 38 assign add_cnt = 1; 39 assign end_cnt = add_cnt && cnt== TIME-1; 40 41 //== led闪烁 42 //====================================================================== 43 always @(posedge clk or negedge rst_n)begin 44 if(!rst_n) 45 led <= 1; 46 else if(end_cnt) 47 led <= ~led; 48 else 49 led <= led; 50 end 51 52 53 endmodule

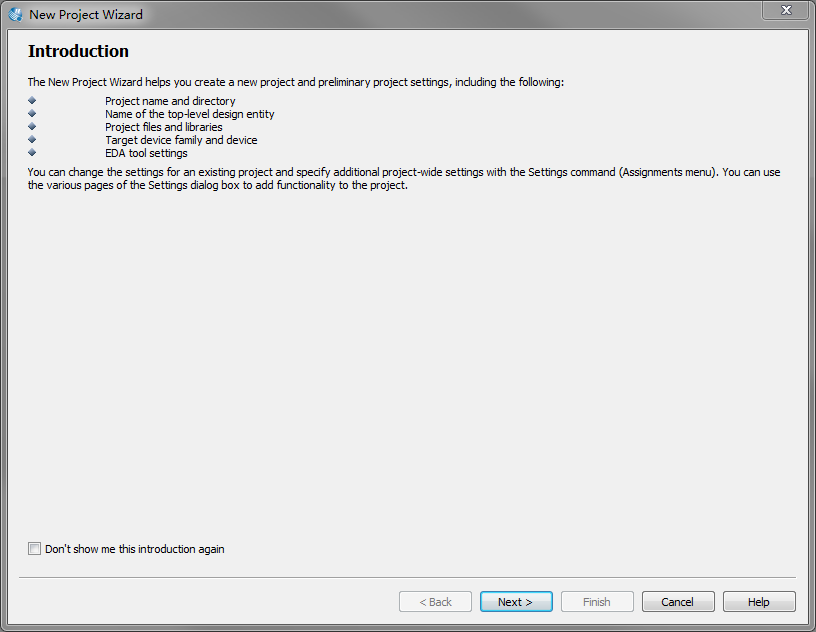

3.开始建立工程,打开quartus ii,点击左上角File --- New Project Wizard,出现下图界面:

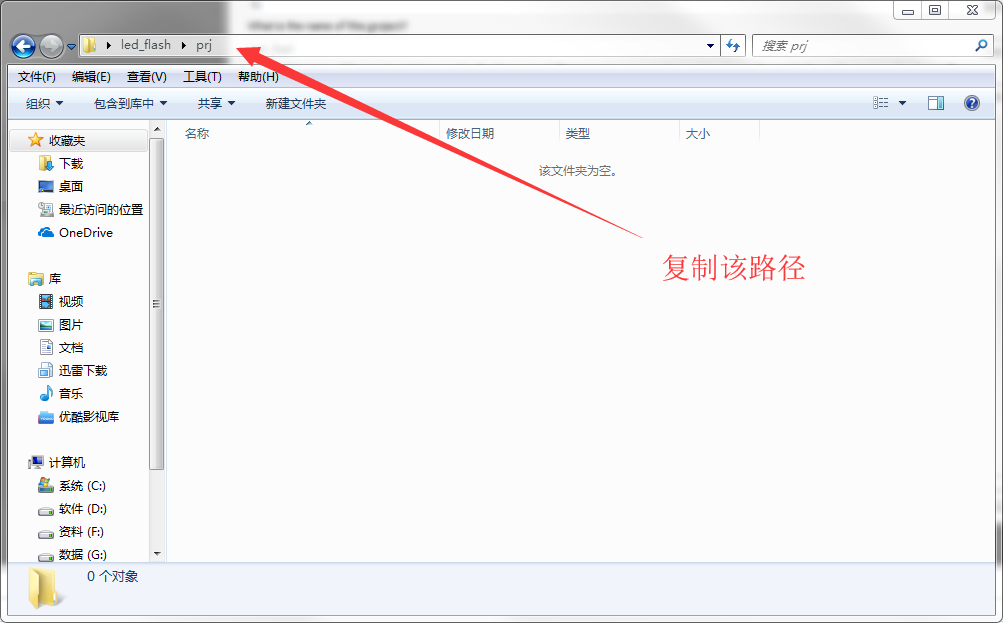

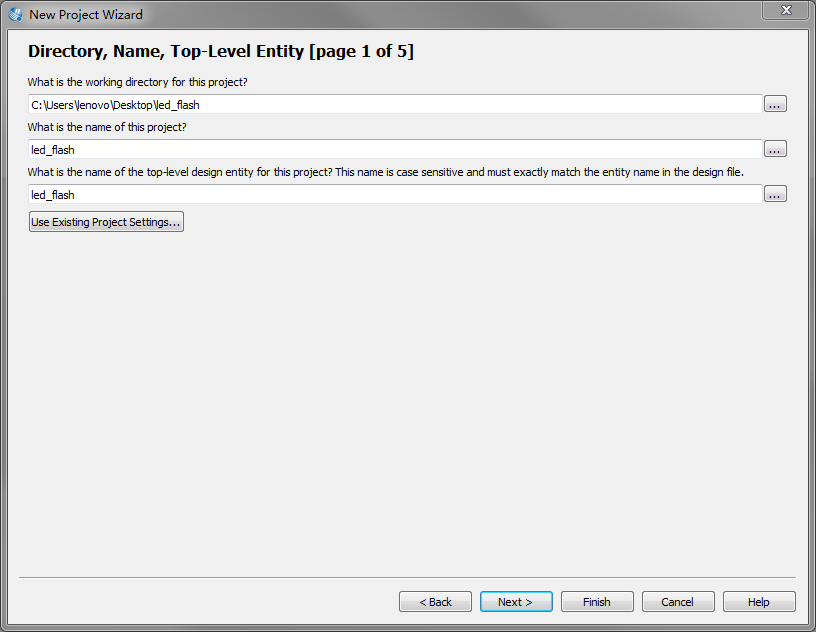

4.点击Next >,出现下图界面。第一行是设置工程的文件夹,我们打开刚刚建立的文件夹:led_flash --- prj,将这个路径复制到这就可以了。第二是工程名称,第三行是top文件名称,这两行会自动保持一致,就让他和我们建立的文件夹命名保持一致吧。

5.点击Next >,出现以下界面,是否添加文件。如果我们之前写好了代码文件,就可以在此处添加,如果没有就直接Next >。如果误点,后面也还是可以添加文件的,不慌。

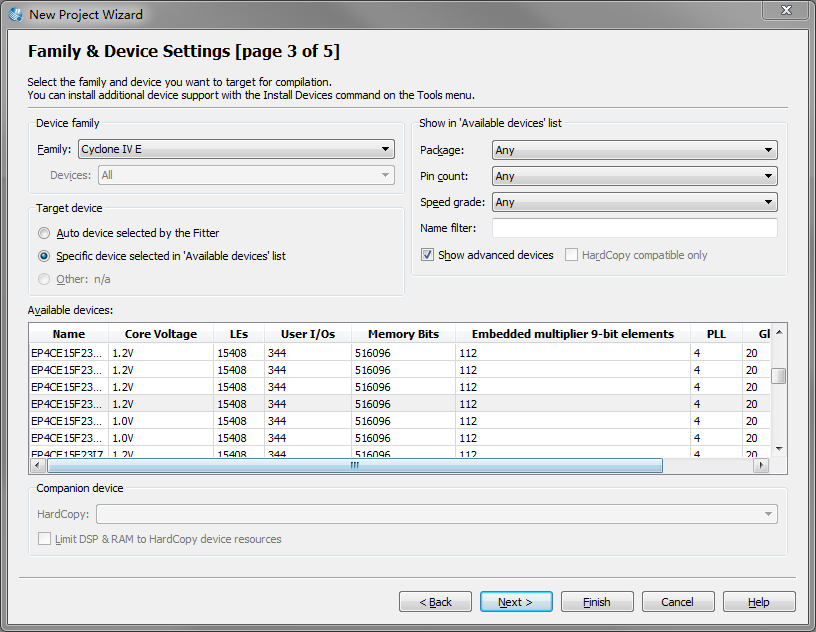

6.Next >之后出现以下界面,FPGA的器件选择,按照手上有的FPGA选择正确的器件就行了。

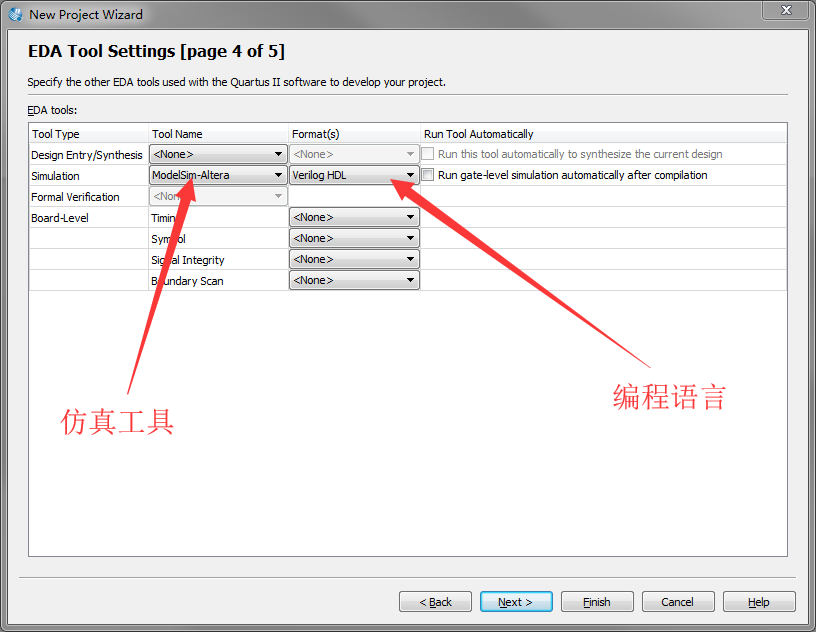

7.Next >之后出现以下界面,EDA工具选择,一般来说我们把VHDL改成Verilog就行。

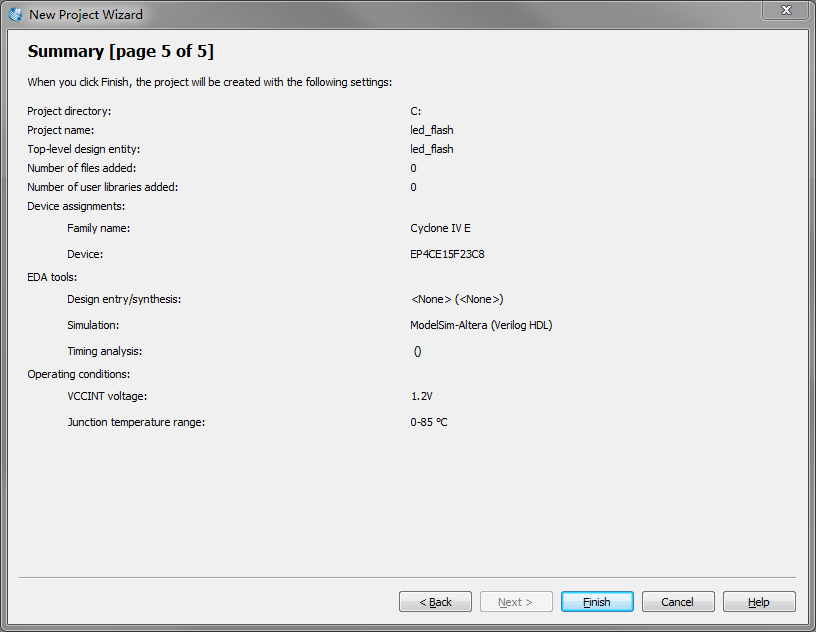

8.Next > 之后出现以下界面,把之前的选择再陈列给你看,如果没有问题点击Finish即可,这样一个工程就建好了。

9.回到了quartus ii主页面,点击左上角的New图标即可新建各种文件,没什么好说的。

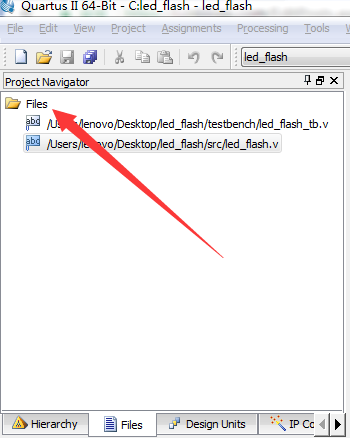

10.在工程栏中选择Files,点击此处可以继续添加文件。

三、常用设置

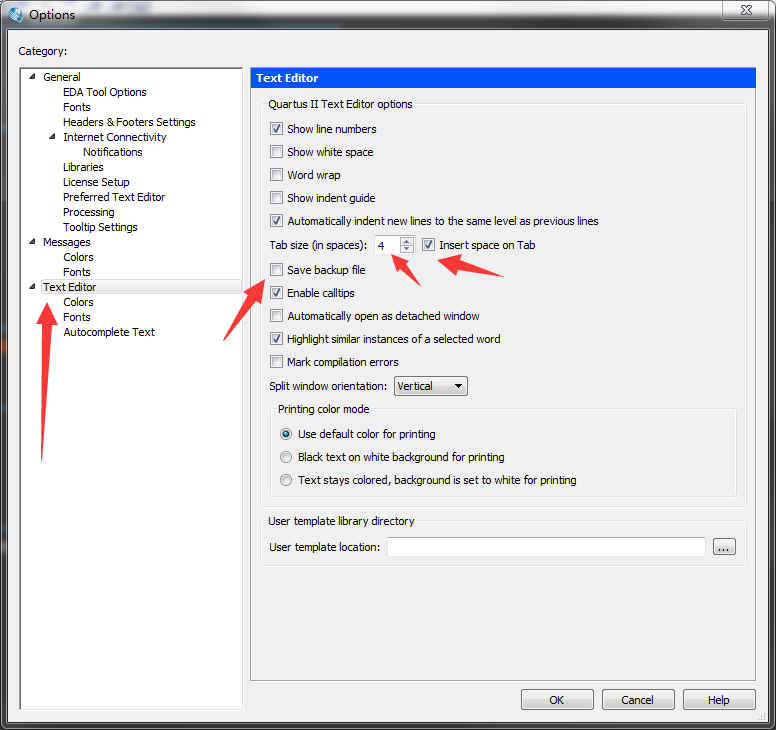

1.quartus ii自带文本编辑器的设置,一次设置成功以后都会默认如此。

在打开了代码文件的情况下,点击Tools --- Options --- Text Editor,出现以下界面。Tab size默认是3我们改成4,后面的Tab符转空格符打上勾,这样代码就不会因为Tab符和其他编译器不同而导致看上去没对齐了。下面还有一个Save backup file,我们不打勾,不然每次都出现备份文件其实挺烦的。

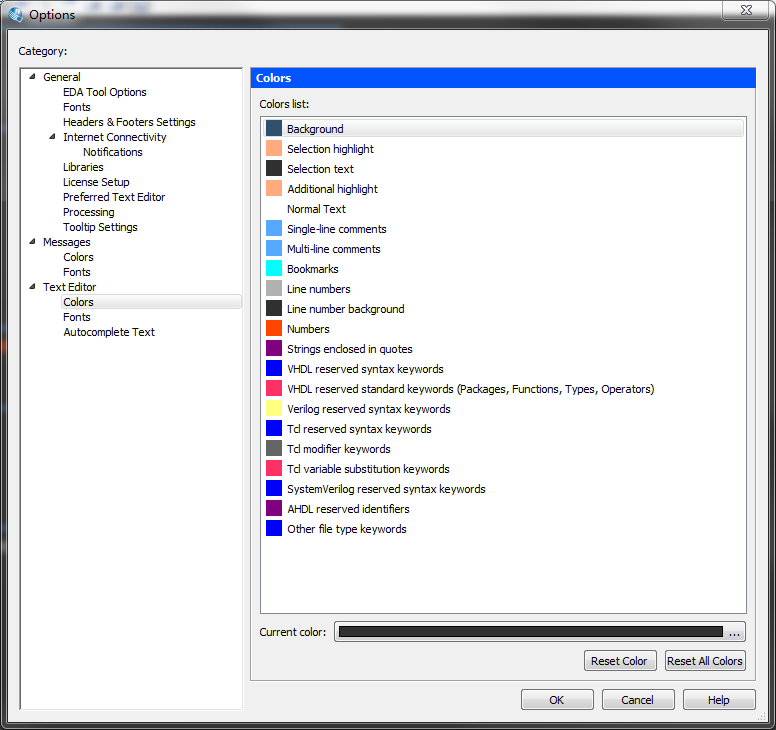

同时看到Text Editor下还有Colors设置,我们可以调整成自己喜欢的风格。我的设置如下:

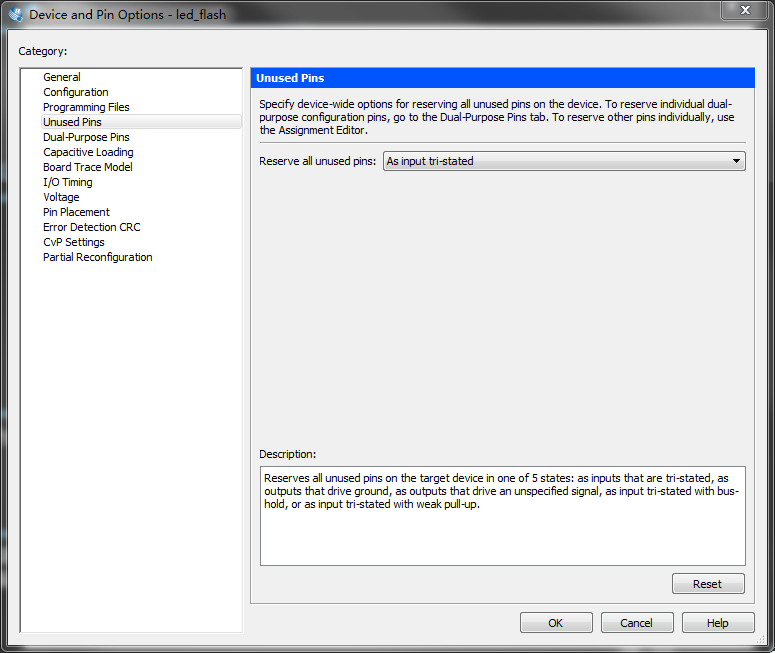

2.建立工程后,不用引脚设置成三态:Assignment --- Device --- Device and Pin Options... --- Unused Pins --- As input tri-stated

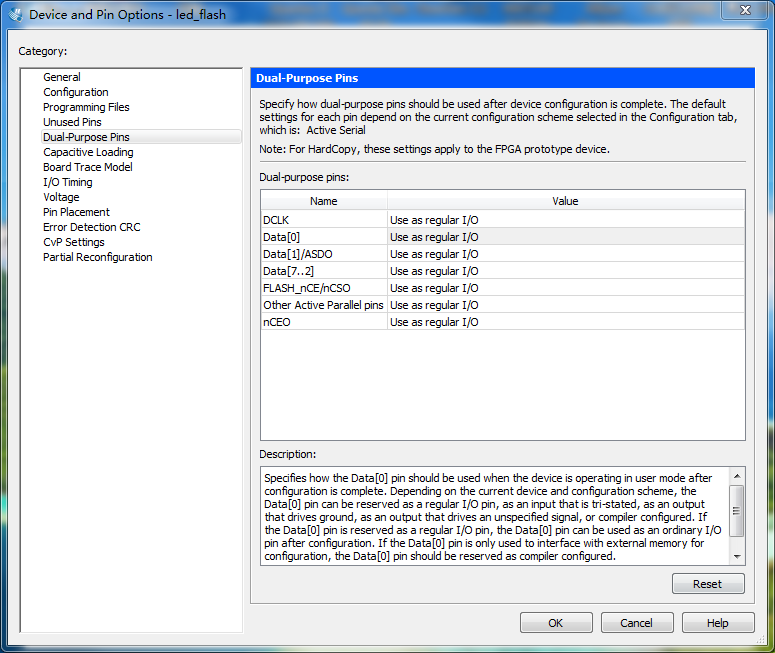

3.建立工程后,多功能引脚全设置成I/O口,或者只把nCEO设置成I/O口,关于这个我不是很明白。Assignment --- Device --- Device and Pin Options... --- Dual-Purpose Pins --- Use as regular I/O

四、VWF仿真的使用

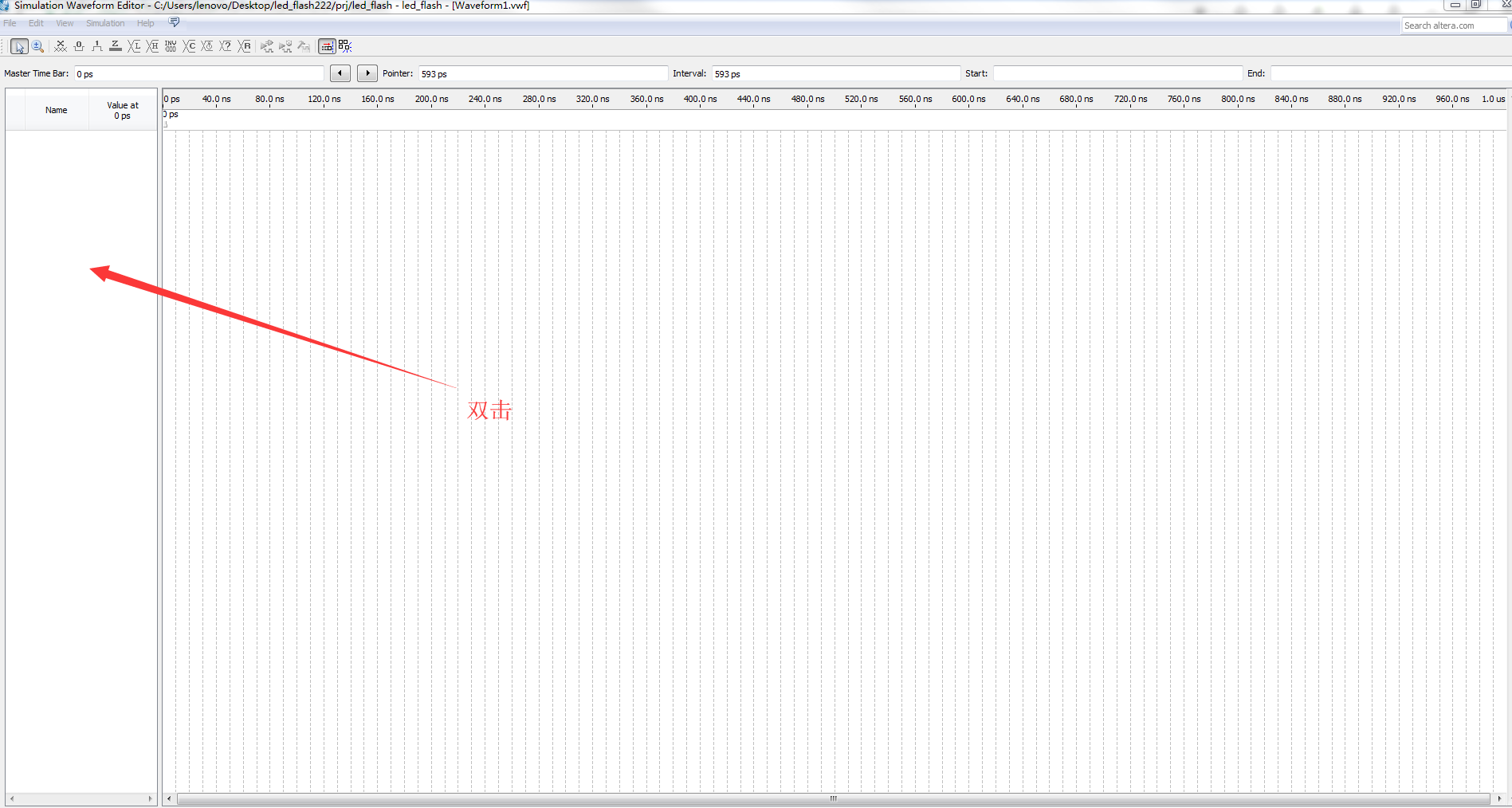

1.仿真我们一般是用modelsim,但如果是简单的设计可以直接使用VWF。点击New --- University Prgram VWF,出现以下界面。

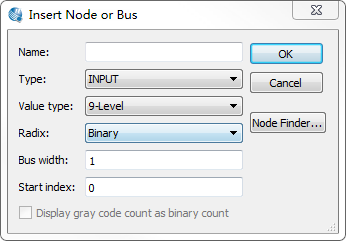

2.双击空白处,添加信号,点击Node Finder

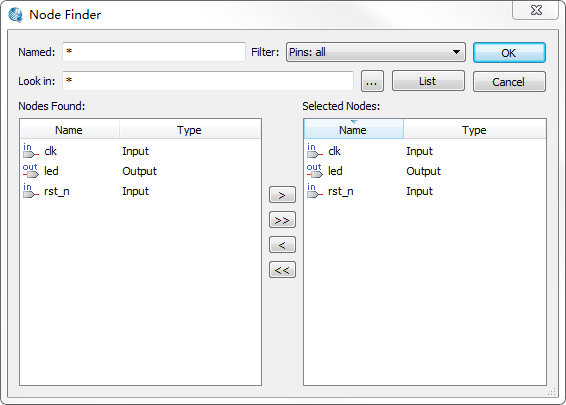

3.点击list,把信号添加进去。然后OK --- OK

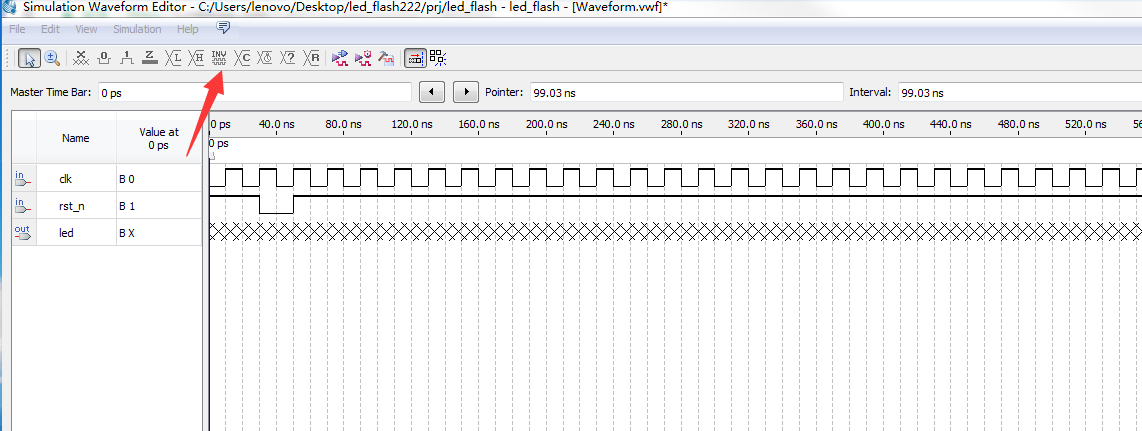

5.设置一下结束时间,Edit --- Set End Time,默认是1us,最大只能到100us,比modelsim弱爆了,为了配合这个工程,我把代码里的50_000_000改成了50。

4.将输入信号手动添加激励,点击上面的快捷图标就行了。

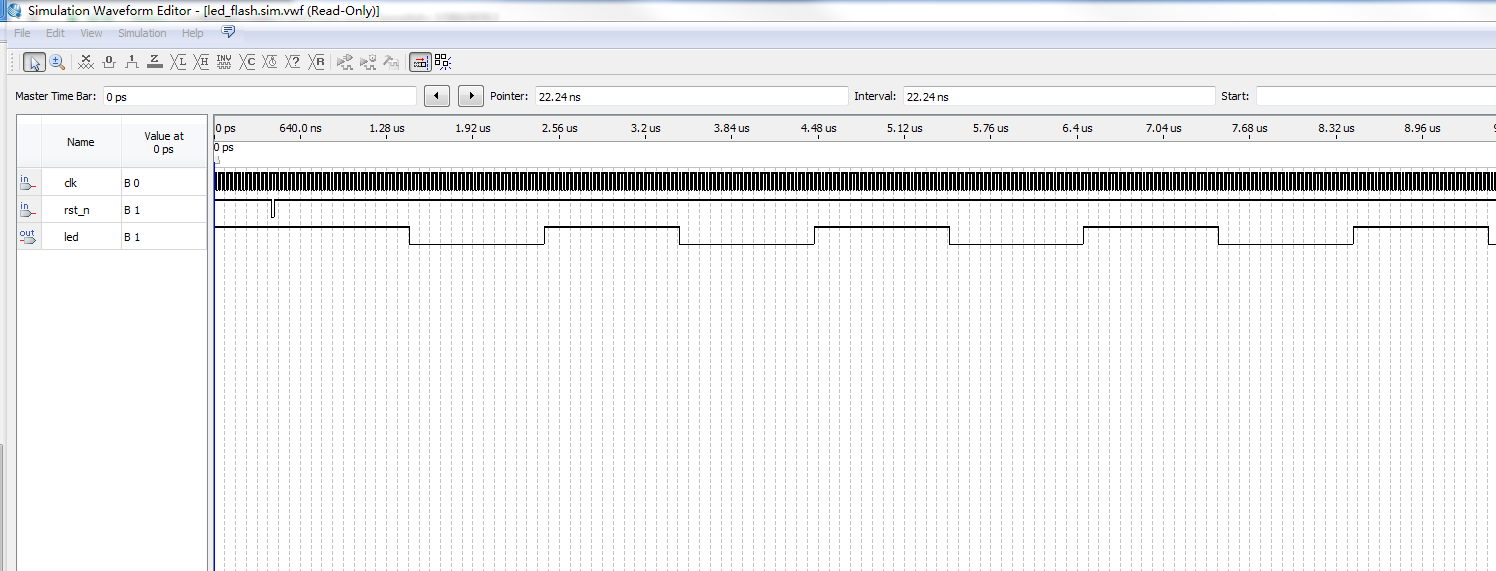

5.进行保存,然后点击那两个仿真图标,它会自动编译,自动弹出仿真结果。

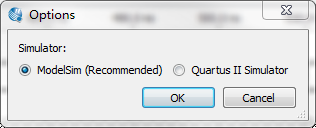

6.如果你打开别人的工程,发现波形无法仿真出现,可以这样试试:点击simulation --- Options,更改一下这个选项试试。

Quartus ii真的很强大,我才刚入门,以后遇到问题再记录下来吧。