一、基本概念

1.时序:时钟和数据的对应关系

2.约束:告诉综合工具,我们希望时序达到什么样的标准

3.违例:时序达不到需要的标准

4.收敛:通过调整布局布线方案来达到这个标准

5.静态时序分析:电路未跑起来时,延时等已知,以此分析时序

6.动态时序分析:电路跑起来,如Modelsim软件(理想状态)

二、时序分析基本模型

模型分为以下四种:(注:PAD指管脚)

- 寄存器与寄存器之间

- 输入PAD与寄存器之间

- 寄存器与输出PAD之间

- 输入PAD 与输出PAD之间(太极端,不讨论)

知识补充:

1、全局时钟:FPGA时钟到各个寄存器的时间非常接近。

2、自分频时钟:走的是数据线,到各个寄存器的时间差异非常大。

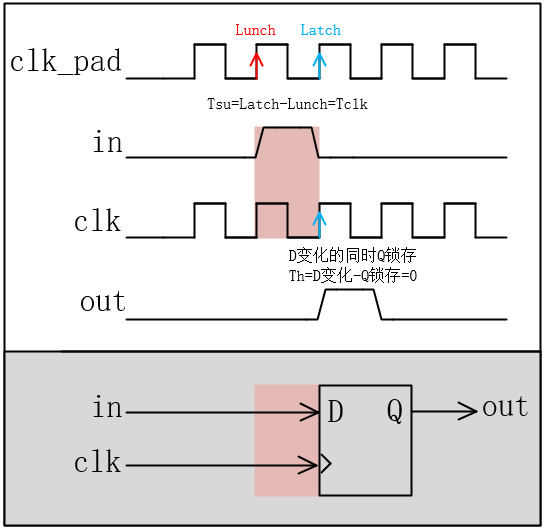

三、理想状态的建立时间和保持时间

1、建立时间 Time setup

(1) 接收时钟上升沿前,发送数据要准备好的时间

(2) Tsu = 数据锁存沿(Latch)- 数据发送沿(Lanch)= 时钟周期

2、保持时间 Time hold

(1) 接收时钟上升沿后,发送数据要保持住的时间

(2) Th = 发送端数据变化时 - 接收端数据锁存 = 0

3、补充

(1) D触发器本身也有建立/保持时间的概念,称之为寄存器建立时间门限和寄存器保持时间门限,这是一个固有属性,是确定的、不变的。当理想状态时,我们讨论建立/保持时间就相当于讨论D触发器的这一固有属性。

(2) FPGA所有时序问题,根本原因都是“建立时间和保持时间”的问题。

(3) 解决建立时间不足的方法是“减少延时”,而解决保持时间不足的方法是“增加延时”。

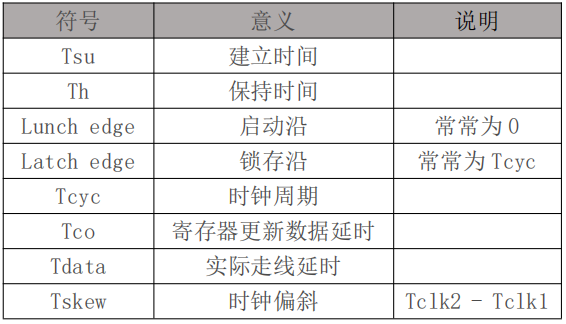

4、符号说明

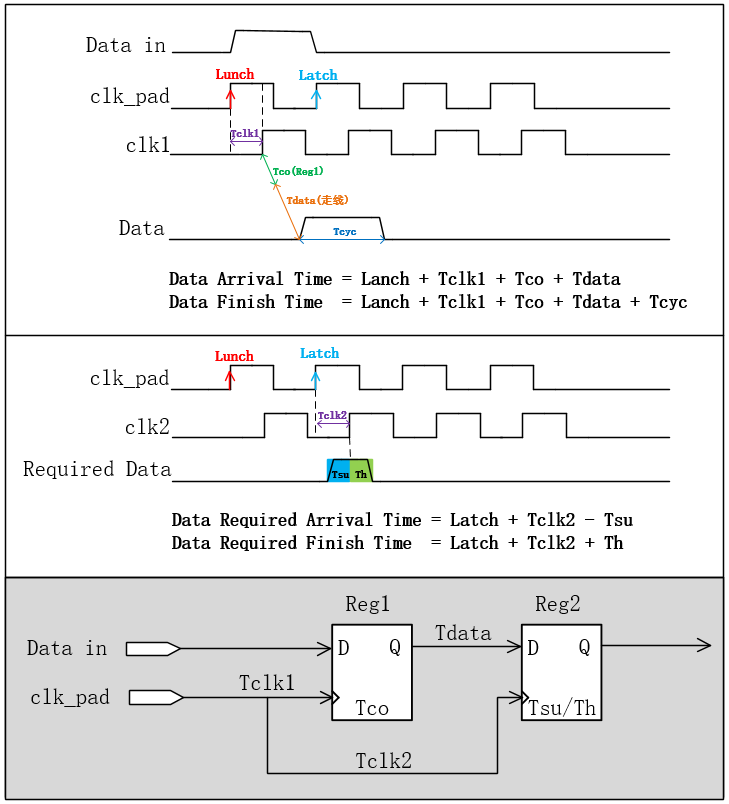

四、建立时间余量和保持时间余量

- Lunch edge:发射沿,以 clk_pad 为基准,一般看成 0 时刻。实际时间是上一个寄存器所用的时间,因此用 clk1,看数据到达下一个寄存器的 D 端用了多久时间,结束时间又是多久。

- Latch edge:接收沿,以 clk_pad 为基准,一般看成 0+Tcyc 时刻,要求时间是下一个寄存器计算的时间,所以用 clk2,看它自身需要的到达时间和结束时间是什么时候。

1、时间

- 建立时间余量:Tsu slack = Data Required Arrival time - Data Arrival Time = Tskew -(Tco + Tdata)- Tsu + Tcyc

- 保持时间余量:Th slack = Data Finish time - Data Required Finish time = (Tco + Tdata)- Tskew - Th

2、最小时间(余量为0)

- 最小建立时间 Tsu ≤ Tskew - (Tco + Tdata) +Tcyc

- 最小保持时间 Th ≤ (Tco + Tdata)- Tskew

3、最小时钟周期

- Tcyc = (Tco + Tdata) - Tskew + Tsu + Tjitter

4、组合逻辑最大延时

- Tdata = Tcyc - (Tsu + Th)

参考资料:V3学院FPGA教程