原文链接:https://blog.csdn.net/silent123go/article/details/70147287

原文作者:o倚楼听风雨o

-------------------------------------------------------------------------------------------------

MII (Media Independent Interface(介质无关接口)或称为媒体独立接口,它是IEEE-802.3定义的以太网行业标准。它包括一个数据接口和一个MAC和PHY之间的管理接口。“媒体独立”表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作。MII接口的类型有很多,常用的有MII、RMII、SMII、SSMII、SSSMII、GMII、RGMII、SGMII,下面对它们进行一一介绍。

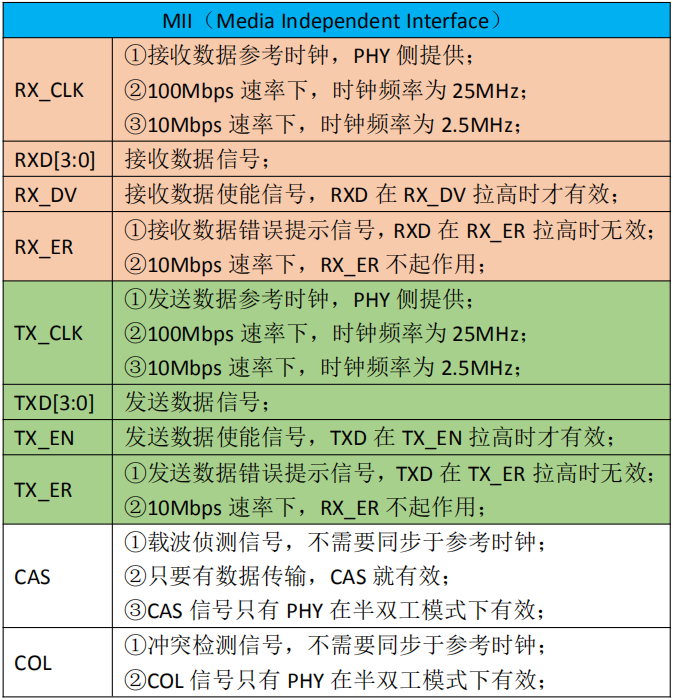

一、MII

MII接口共有 16 根线,说明如下:

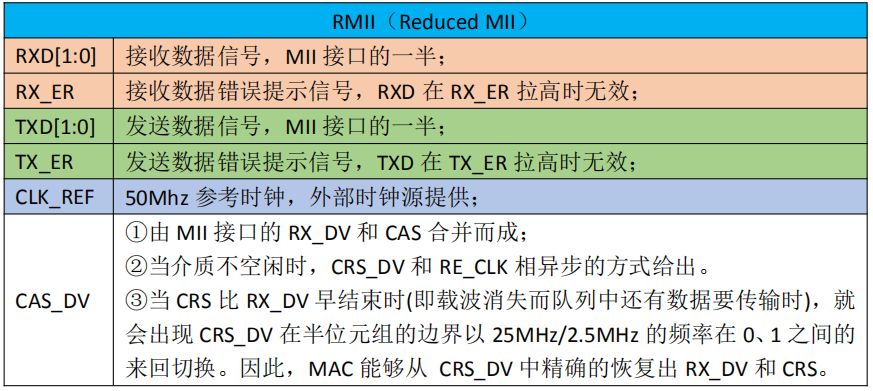

二、RMII

RMII 即 Reduced MII,是MII的简化板,连线数量由MII的16根减少为8根,说明如下:

在100Mbps速率时,TX/RX每个时钟周期采样一个数据;在10Mbps速率时,TX/RX每隔10个周期采样一个数据,因而TX/RX数据需要在数据线上保留10个周期,相当于一个数据发送10次。

当PHY层芯片收到有效的载波信号后,CRS_DV信号变为有效,此时如果FIFO中还没有数据,则它会发送出全0的数据给MAC,然后当FIFO中填入有效的数据帧,数据帧的开头是“101010—”交叉的前导码,当数据中出现“01”的比特时,代表正式数据传输开始,MAC芯片检测到这一变化,从而开始接收数据。

当外部载波信号消失后,CRS_DV会变为无效,但如果FIFO中还有数据要发送时,CRS_DV在下一周期又会变为有效,然后再无效再有效,直到FIFO中数据发送完为止。在接收过程中如果出现无效的载波信号或者无效的数据编码,则RX_ER会变为有效,表示物理层芯片接收出错。

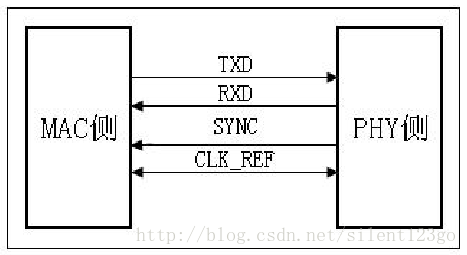

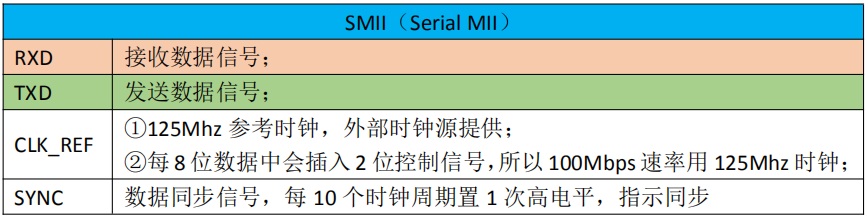

三、SMII

SMII即Serial MII,串行MII的意思,跟RMII相比,连线进一步减少到4根,说明如下:

TXD/RXD以10比特为一组,以SYNC为高电平来指示一组数据的开始,在SYNC变高后的10个时钟周期内,TXD上依次输出的数据是:TXD[7:0]、TX_EN、TX_ER,控制信号的含义与MII接口中的相同;RXD上依次输出的数据是:RXD[7:0]、RX_DV、CRS,RXD[7:0]的含义与RX_DV有关,当RX_DV为有效时(高电平),RXD[7:0]上传输的是物理层接收的数据。当RX_DV为无效时(低电平),RXD[7:0]上传输的是物理层的状态信息数据。见下表:

当速率为10Mbps时,每一组数据要重复10次,MAC/PHY芯片每10个周期采样一次。MAC/PHY芯片在接收到数据后会进行串/并转换。

四、SSMII

SSMII即Serial Sync MII,叫串行同步接口,跟SMII接口很类似,只是收发使用独立的参考时钟和同步时钟,不再像SMII那样收发共用参考时钟和同步时钟,传输距离比SMII更远。说明如下:

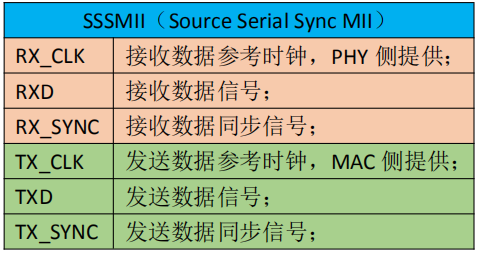

五、SSSMII

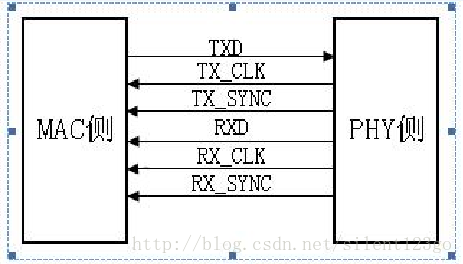

SSSMII即Source Sync Serial MII,叫源同步串行MII接口,SSSMII与SSMII的区别在于参考时钟和同步时钟的方向,SSMII的TX/RX参考时钟和同步时钟都是由PHY芯片提供的,而SSSMII的TX参考时钟和同步时钟是由MAC芯片提供的,RX参考时钟和同步时钟是由PHY芯片提供的,所以顾名思义叫源同步串行。说明如下:

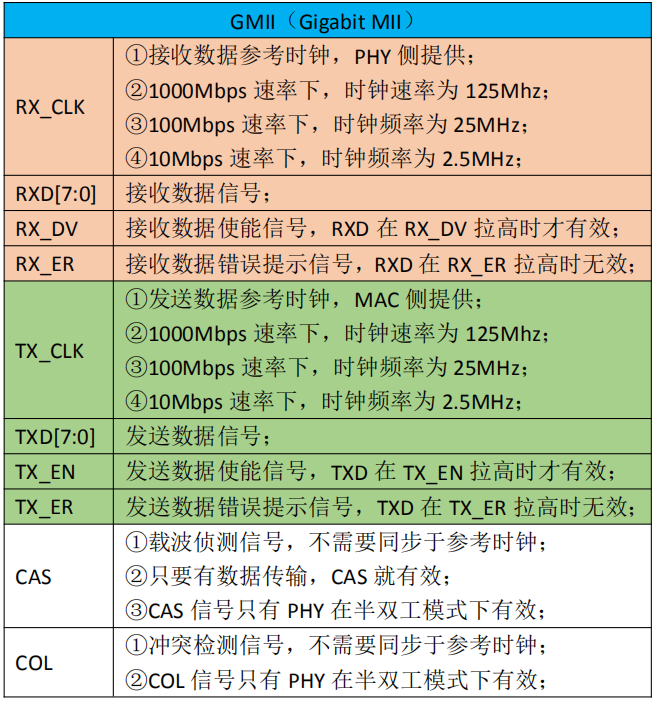

六、GMII

与MII接口相比,GMII的数据宽度由4位变为8位,在实际应用中,绝大多数GMII接口都是兼容MII接口的,所以,一般的GMII接口都有两个发送参考时钟:TX_CLK和GTX_CLK(两者的方向是不一样的,前面已经说过了),在用作MII模式时,使用TX_CLK和8根数据线中的4根。说明如下:

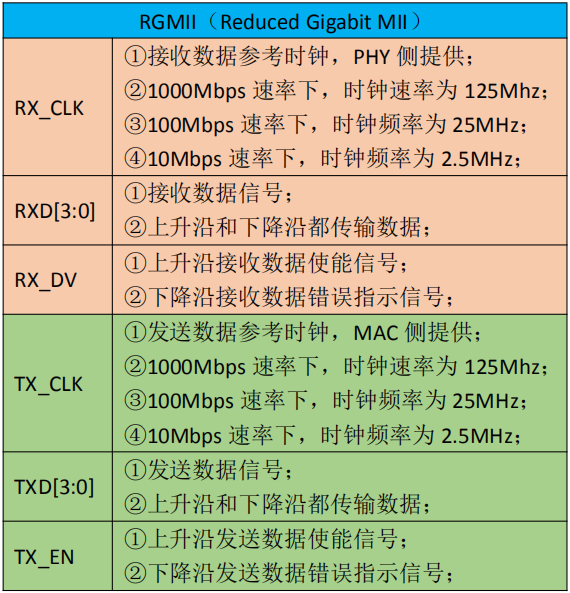

七、RGMII

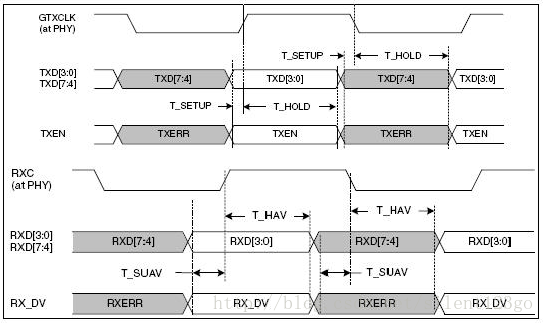

RGMII即Reduced GMII,是RGMII的简化版本,将接口信号线数量从24根减少到14根(COL/CRS端口状态指示信号,这里没有画出),上升沿和下降沿都传输数据,说明如下:

补充:很多接口的时钟都是外部提供,如果那个时钟引脚接的是 FPGA 的普通 IO 口,那么该时钟的扇出会非常大,可以将该时钟转换为全局时钟,例如 Quartus 中开发百兆网 MII 接口时,可以采用 Altclkctrl IP 将 RX_CLK 设置为全局时钟,或者对时钟添加一下约束,可以改善工程的时序。