系统总线指处理器总线(又称前端总线,Intel体系结构系统总线特指处理器总线)、存储器总线、I/O总线。传输的信息包括:数据(指令、操作数、中断号)、地址、其他控制/状态/定时等信号

系统总线通常由一组控制线、一组数据线和一组地址线构成。

也有些总线没有单独的地址线,地址信息通过数据线来传送,这种情况称为数据/地址复用。

数据线(Data Bus)承载在源和目部件之间传输的信息。数据线的宽度反映一次能传送的数据的位数。

地址线(Address Bus)给出源数据或目的数据所在的主存单元或I/O端口的地址。地址线的宽度反映最大的寻址空间。

控制线(Control Bus)控制对数据线和地址线的访问和使用。用来传输定时信号和命令信息。典型的控制信号包括:

- 时钟(Clock):用于总线同步

- 复位(Reset):初始化所有设备

- 总线请求(Bus Request):表明发出该请求信号的设备要使用总线

- 总线允许(Bus Grant):表明接收到该允许信号的设备可以使用总线

- 中断请求(Interrupt Request):表明某个中断正在请求

- 中断回答(Interrupt Acknowledge):表明某个中断请求已被接受

- 存储器读(memory read):从指定的主存单元中读数据到数据总线上

- 存储器写(memory read):将数据总线上的数据写到指定主存单元中

- I/O读(I/O read):从指定的I/O端口中读数据到数据总线上

- I/O写(I/O Write) :将数据总线上的数据写到指定的I/O端口中

- 传输确认(transmission Acknowledge):数据已被接收或已送总线

IO发展对总线的影响

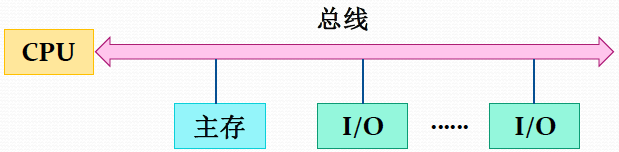

- 单总线: 将CPU、主存和I/O模块连接到同一组总线上

优点:结构简单,易于扩充

缺点:主存需要和I/O模块共用总线;设备增多会造成总线变长,进而增加传输时延;无法适用于大量高速设备

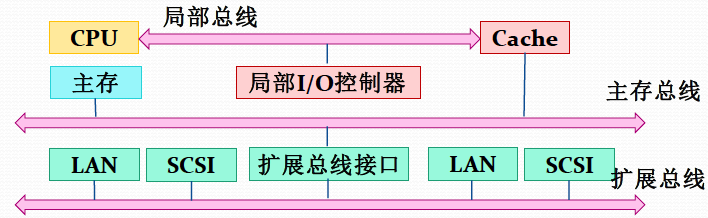

- 传统的三级总线:主存和Cache通过主存总线传送数据,主存总线和扩展总线上的I/O设备之间传送数据通过扩展总线接口缓冲

优点:主存与I/O之间的数据传送与处理器的活动分离;可以支持更多的I/O设备

缺点:不适用于I/O设备数据速率相差太大的情形

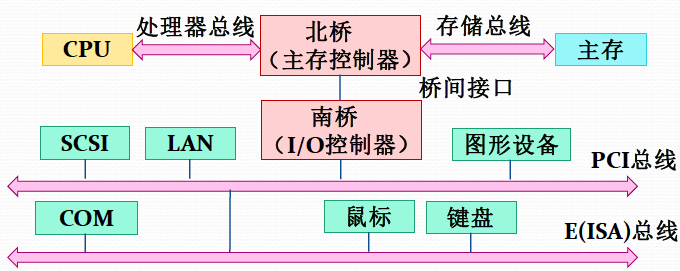

- 采用南北桥的多级总线:通过存储总线、PCI总线、E(ISA)总线分别连接主存、高速I/O设备和低速I/O设备

优点:可以支持不同数据速率的I/O设备

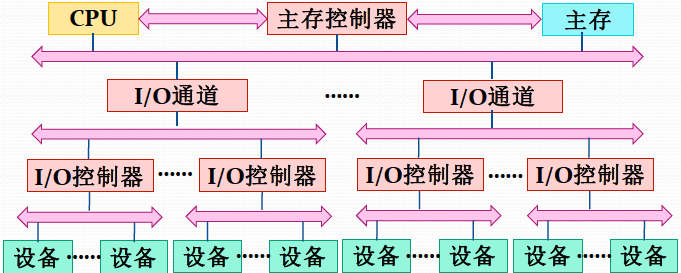

- 采用I/O通道的多级总线

支持CPU、主存和多个I/O通道之间的数据传送

支持I/O通道和I/O控制器,以及I/O控制器和设备

- 总线裁决

早期:总线多是共享传输,需确定哪个设备使用总线。

现在:总线多是点对点传输,无需裁决。

- 总线定时

定义总线事务中的每一步何时开始、何时结束。

Synchronous (同步):用时钟信号来确定每个步骤

Asynchronous(异步):用握手信号来定时,前一个信号结束就是下一个信号的开始

半同步:结合使用时钟信号和握手信号来定时

- 并行/串行传输

并行传输:一个方向同时传输多位数据信号,故位与位需同步,慢

串行传输:一个方向只传输一位数据信号,无需在位之间同步,快

现在总线设计的趋势是:点对点、同步、串行

总线的性能指标:

- 总线宽度:总线中数据线的条数,决定了每次能同时传输的信息位数

- 总线工作频率:每秒传送次数(MT/s或GT/s)。

早期的总线通常一个时钟传送一次数据 ,此时,工作频率等于总线时钟频率;

现在总线一个时钟周期可传送2次或4次数据,因此,工作频率是时钟频率的2倍或4倍

- 总线带宽

总线的最大数据传输率(一秒钟内传输的数据量)

总线带宽计算公式: B=W×F/N

W-总线宽度;F-总线时钟频率;N-完成一次数据传送所用时钟周期数;F/N实际上就是总线工作频率

- 总线传送方式:

非突发传送:每个总线事务都传送地址,一个地址对应一次数据传送

突发(Burst)传送:即成块数据传送。突发传送总线事务中,先传送一个地址,后传送多次数据,后续数据的地址默认为前面地址自动增量

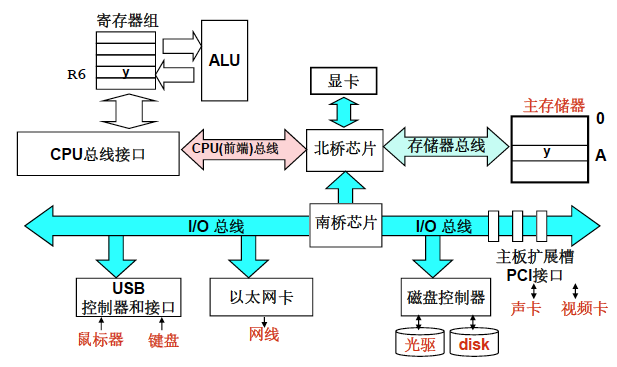

以下图为例:

存储器控制器单独做到了北桥芯片。

扩展槽(就是一种总线)用来插网卡、声卡等

声卡等也可以直接集成在主板上,做到南桥芯片里。

存储器总线实际上是内存条的插槽。

处理器总线:

前端总线(Front Side Bus,FSB)

早期Intel架构使用,位于CPU芯片与北桥芯片之间互连

从Pentium Pro开始,FSB采用quad pumped技术:每个总线时钟周期传送4次数据

并行传输、同步定时方式

若工作频率为1333MHz(实际单位应是MT/s,表示每秒传送1333M次 ,实际时钟频率为333MHz),总线宽度为64位,则总线带宽为1333MT/s×8B=10.5GB/s

QPI(Quick Path Interconnect)总线

目前在Intel架构中CPU芯片内部核之间、CPU芯片之间、CPU芯片与IOH(I/O Hub)芯片之间,都通过QPI总线互连。

QPI是基于包交换的串行、高速点对点连接:发送方和接收方各有时钟信号 ,双方同时传输数据(各有20条数据线,相互之间不需要同步),每个QPI数据包含80位,分两个时钟周期传送,每个时钟周期传两次(上升沿下降沿各一次),每次传20位(16位数据+4位校验位)。

QPI总线的速度单位(工作频率)为GT/s,表示每秒传送多少G次。若QPI时钟频率为2.4GHz,则速度为4.8GT/s,带宽为4.8G×2B×2=19.2GB/s(发送接收同时进行)

存储器总线:

以Intel Core i7为例:

core通过QPI总线与另外三个core相连

北桥和三个存储器控制器做在了CPU芯片内,CPU通过存储器总线(即内存条插槽,图中为三通道插槽)直接和内存条相连。

内存条应该插在工作频率为1333MT/s的总线上,每次读64位,最多可以三通道同时传输。

I/O总线:

I/O总线用于为系统中的各种I/O设备提供输入输出通路,在物理上可以是主板上的I/O扩展槽,如:

第一代:ISA/EISA总线、VESA总线,早被淘汰

第二代:PCI、AGP、PCI-X,被逐渐淘汰

第三代:PCI-Express(串行总线,主流总线)

两个PCI-Express设备之间以一个链路(link)相连,每个链路包含多条通路(lane),可以是1、2、4、8、16或32条

PCI-Express×n表示一个具有n条通路的PCI-Express链路

每条通路可同时发送和接受,每个数据字节被转换为10位信息被传输PCI-Express1.0下,每条通路的发送和接受速率都是2.5Gb/s,故PCI-Express×n的带宽为:2.5Gb/s×2×n/10=0.5nGB/s。

如:PCI-Express1.0下,PCI-Express×2的带宽为1GB/s,PCI-Express×4的带宽为2GB/s,PCI-Express×16的带宽为8GB/s。

以Intel Core i7为例:

高速设备挂接在IOH,慢速设备挂接在ICH。

QPI总线的带宽为:6.4GT/s×2B×2=25.6GB/s

每个存储器总线的带宽为:64b/8×1066 MT/s = 8.5 GB/s