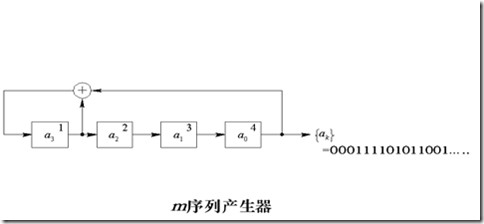

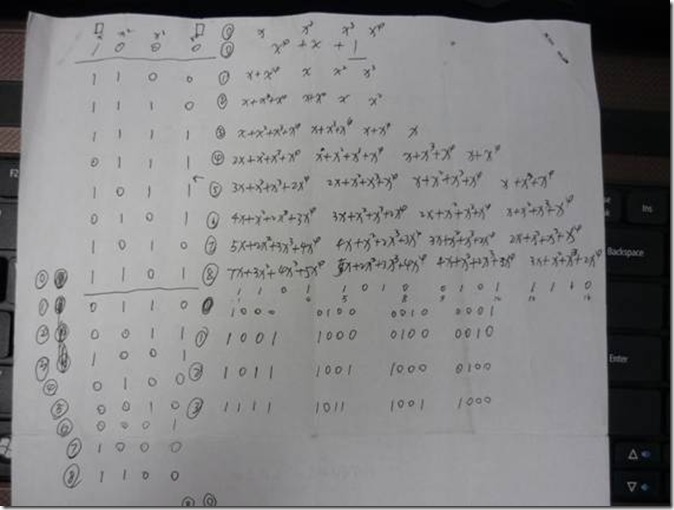

1. 4阶m序列生成器

一开始希望通过使用8个PN序列生成器并行实现,但是,每个生成器都不能得到后8个状态的值。

由于后面的8bit PN序列,通过一个clk不可能通过状态转换实现,所以,只能通过计算得到

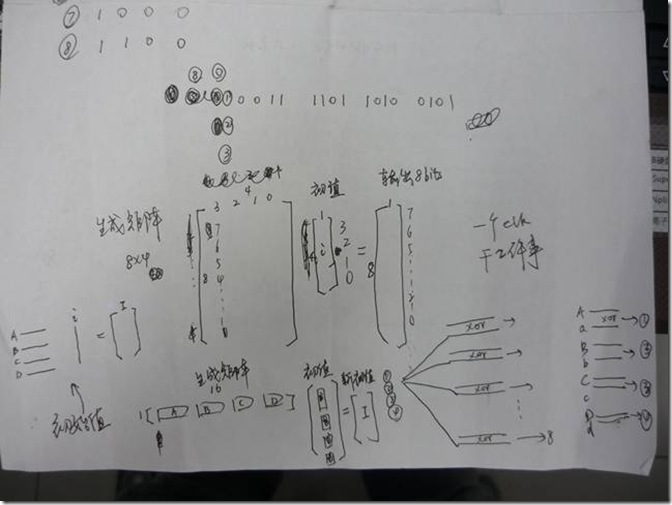

利用Matlab计算得到后8位PN码与初始状态的关系,得到一个输出生成矩阵,使用生成矩阵与初始状态相乘,即可得到8位PN码

同时,计算得到生成第8位PN码时移位寄存器的状态,得到一个初始值生成矩阵,使用此矩阵与初始状态相乘,即可得到生成第8位PN码时移位寄存器的状态,从而为下一次迭代提供初始状态。

两个矩阵在PN码生成过程中保持不变,而初始状态得到不断更新,8位PN码不断输出。

clc; clear;

n = 4; % 4 order

bit = zeros(9,n^2);

bit(1,:) = [1 0 0 0 0 1 0 0 0 0 1 0 0 0 0 1];

initial = [1 0 0 0];

for i = 2:9

% generate polynimial, 1 + x + x^4, ==========x + x^4,

bit(i,:) = [ mod( bit(i-1,1:n)+bit(i-1,3*n+1:4*n), 2), bit(i-1,1:3*n)];

end

genmatrix = bit(2:9,3*n+1:4*n) % generate matrix remain the same

for j = 1:1

mseq = mod(genmatrix*initial', 2)

% Update initial

temp = initial;

for k = 1:n

initial(k) = mod( sum(bit(9,(k-1)*n+1:k*n)*temp'), 2);

end

end

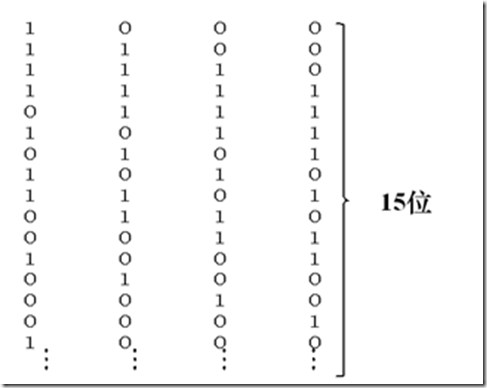

输出生成矩阵为:

genmatrix =

0 0 1 0

0 1 0 0

1 0 0 0

1 0 0 1

1 0 1 1

1 1 1 1

0 1 1 1

1 1 1 0

初始状态值生成矩阵为:

gm_init =

1 1 0 1

1 0 1 0

0 1 0 1

1 1 1 0

Verilog代码:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 15:24:21 05/01/2012

// Design Name:

// Module Name: PNcode8bit

//

//////////////////////////////////////////////////////////////////////////////////

module PNcode8bit(

clk,

rst,

init,

PNout

);

// PN code n = 4, f(x) = 1 + x + x^4

// Output 8 bit per clk

parameter order = 4;

input clk;

input rst;

output [order-1 : 0] init;

output [7 : 0] PNout;

// Output use register

reg [7 : 0] PNout = 0;

reg [order-1 : 0] init = 0;

// Generate matrix of output, use memory

reg [order-1 : 0] gm_out [7 : 0];

// Generate matrix of initial state, use memory

reg [order-1 : 0] gm_init [3 : 0];

integer i, j;

//////////////////////////////////////////

// Memory initialization file read here, generate by Matlab

initial

begin

$readmemb("gm_out.txt", gm_out, 7, 0);

$readmemb("gm_init.txt", gm_init, 3, 0);

end

//////////////////////////////////////////

always @ (posedge clk)

if(rst == 1)

begin

PNout <= 8'b0;

init <= 4'b1000;

end

else

begin

for(i=0; i<8; i=i+1)

PNout[i] <= (gm_out[i][3] & init[3]) ^ (gm_out[i][2] & init[2]) ^ (gm_out[i][1] & init[1]) ^ (gm_out[i][0] & init[0]);

for(j=0; j<4; j=j+1)

init[j] <= (gm_init[j][0] & init[0]) ^ (gm_init[j][1] & init[1]) ^ (gm_init[j][2] & init[2]) ^ (gm_init[j][3] & init[3]);

end

endmodule

说明:

1. 使用readmemb实现存储器数据的初始化,读取二进制内容,因为两个生成矩阵会比较大

$readmemb("gm_out.txt", gm_out, 7, 0);

"gm_out.txt"为读取的文件,gm_out为存放的存储器名字,

7, 0为起始地址和结束地址,最好注明地址范围,不注明好像不太确定

2. 按位与、按位异或 实现二进制矩阵乘法

第一个for是输出生成矩阵(8x4)与初始值(4x1)相乘,得到8bit PN码的输出

第二个for是初始状态值生成矩阵(4x4)与初始值(4x1)相乘,得到新的初始值

gm_out.txt内容:没有空格

0010

0100

1000

1001

1011

1111

0111

1110

gm_init.txt内容:没有空格

1101

1010

0101

1110

测试文件代码:

`timescale 1ns / 1ps

////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 16:27:38 05/01/2012

// Design Name: PNcode8bit

// Module Name: E:/me/CAST/Project/FPGAcomm/PNcode8bit/PNcode8bit_tb.v

// Project Name: PNcode8bit

//

////////////////////////////////////////////////////////////////////////////////

module PNcode8bit_tb;

// Inputs

reg clk;

reg rst;

// Outputs

wire [3:0] init;

wire [7:0] PNout;

// Instantiate the Unit Under Test (UUT)

PNcode8bit uut (

.clk(clk),

.rst(rst),

.init(init),

.PNout(PNout)

);

initial begin

// Initialize Inputs

clk = 0;

rst = 1;

// Wait 100 ns for global reset to finish

#100;

rst = 0;

// Add stimulus here

end

always begin

forever #10 clk = !clk;

end

endmodule

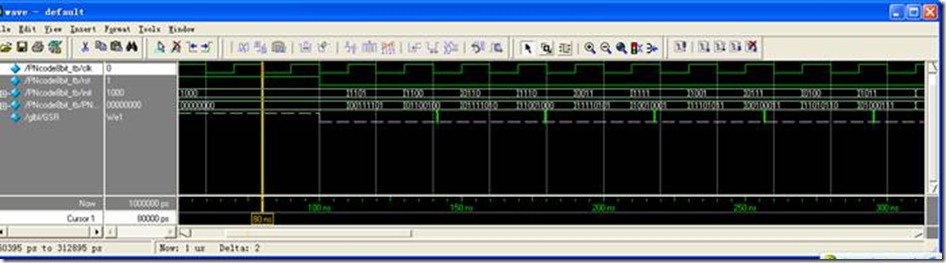

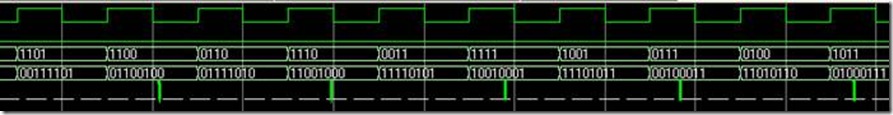

ModelSim仿真结果

局部放大图,绿色竖线为周期间隔,一个周期的PN码为:001111010110010