反馈与触发器

振荡器

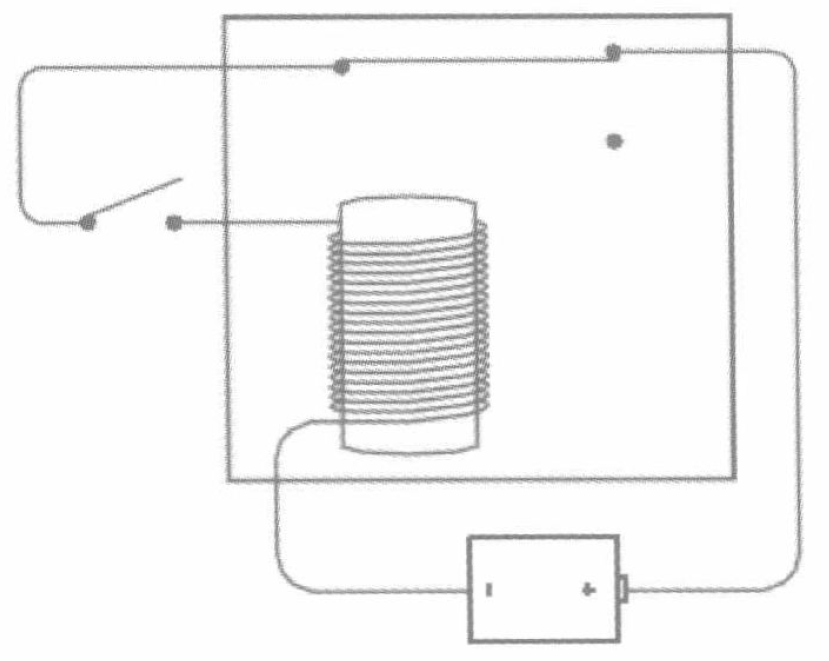

观察如下电路:

这个电路的继电器输入和输出是在一起的,当开关闭合后,电路就会连通,而电路连通后又会让继电器影响的开关断开,就这样,整个电路在连通和断开之间不断切换。如果跳动的开关是一个金属簧片,这个电路就能制作成一个蜂鸣器或电铃。

这种电路回路中只有一个反向器的电路被称为振荡器,反向器不断将电路状态转变,这种转变是需要一些时间的。振荡器不需要人干涉,完全可以自发的工作。

振荡器的输出可以用下幅图来表示:

输出在0和1之间按规律变化,振荡器又被称为时钟,因为可以通过振荡进行计数。振荡器还有自己的周期和频率。

触发器原理

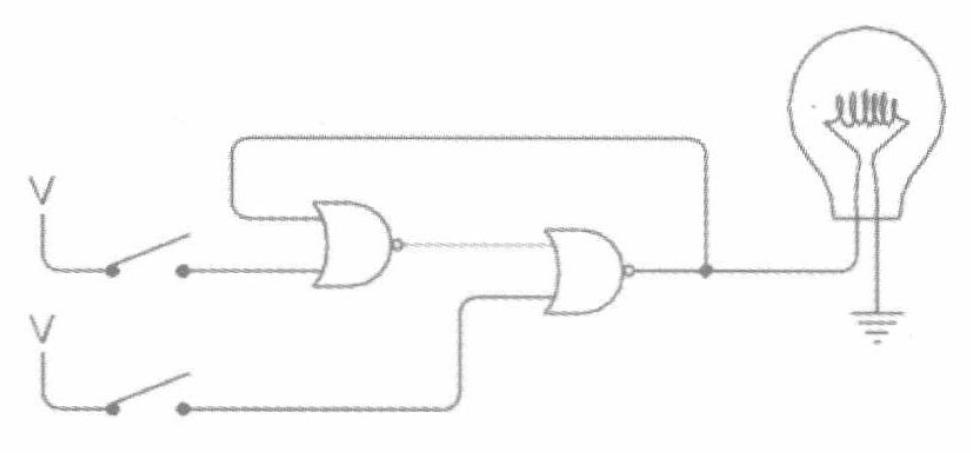

观察下列电路,该电路有一对或非门:

这个电路的连接方式比较特别,左边或非门的输出是右边的输入,右边门的输出是左边的输入,这种连接方式称之为反馈。

当闭合上面的开关时,左边门的输出变为0,右边门的输出变为1,灯泡会被点亮。当断开上面的开关,左边门的输出还是0,右边门依然输出1,灯泡依然发亮。这种电路与之前的情况不同,左上的开关无论开启还是闭合都不会对灯泡发亮产生影响。

当闭合下面的开关时,右边门的输出立刻变为0,灯泡熄灭。此时断开下面的开关,灯泡还是处于熄灭状态,因为之前的操作已经让左边门的输出一直是1了。

综上,这个电路有两个稳定状态,一直熄灭和一直发亮,同样的开关状态可能产生不同的电路状态,这类电路被称为触发器。这个电路如果灯泡是亮着的,说明最后一次连通的是上面的开关,如果是熄灭的,说明最后一次连通的是下面的开关,也就是它可以记住某些信息。

R-S触发器

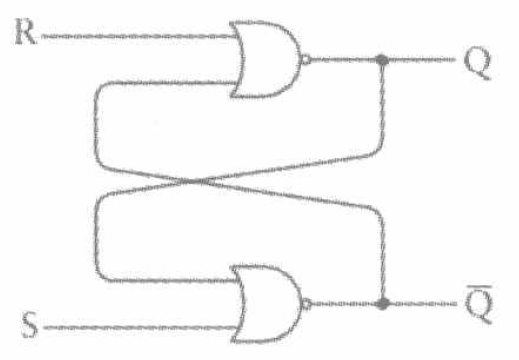

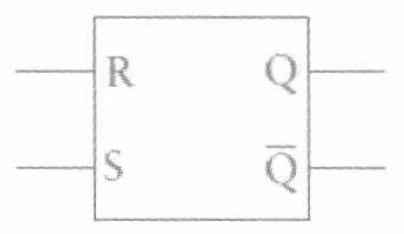

R-S(Reset-Set)触发器是比较简单的触发器,它也是两个或非门的连接:

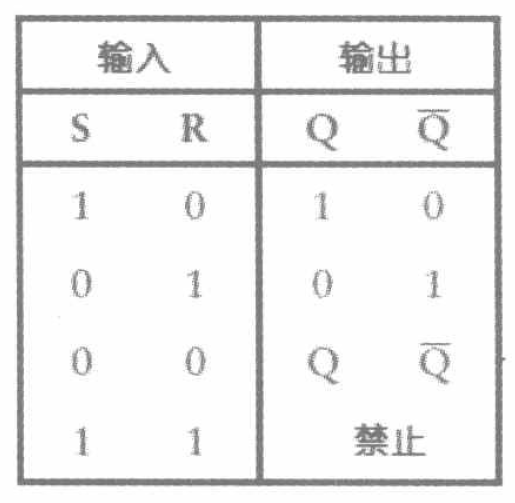

Q代表输出的状态,另一个Q是它的取反。S用来置位(相当于将Q设置为1),R用来复位(相当于将Q设置为0)。当调整S和R为1的时候,Q就会发生变化,当S和R均为0时,Q的状态不变。规律可以总结为下表:

当S和R都为1时的情况是不合法的,这会导致两个Q的状态不互补。R-S触发器可以进一步简化为下列符号:

R-S触发器的特点在于它可以根据Q的状态,反推出来哪个输入端(S还是R)的最终状态为1.

D型锁存器

现在我们要构造一个电路,该电路能记住在某个特定时间的信号。

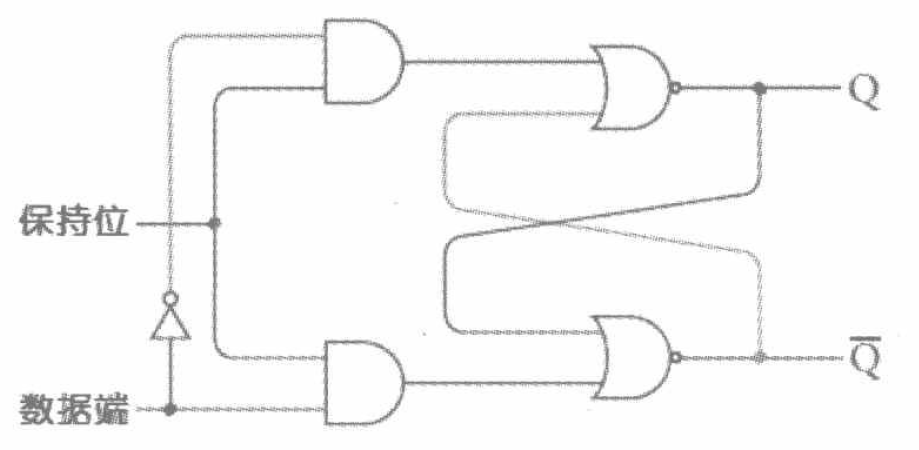

这个电路存在两个输入,一个被称为数据端,一个被称为保持位,保持位通常情况下被设置为0,此时数据端对电路不产生影响,当保持位置为1时,数据端的值就会被电路记住。此时电路的真值表为:

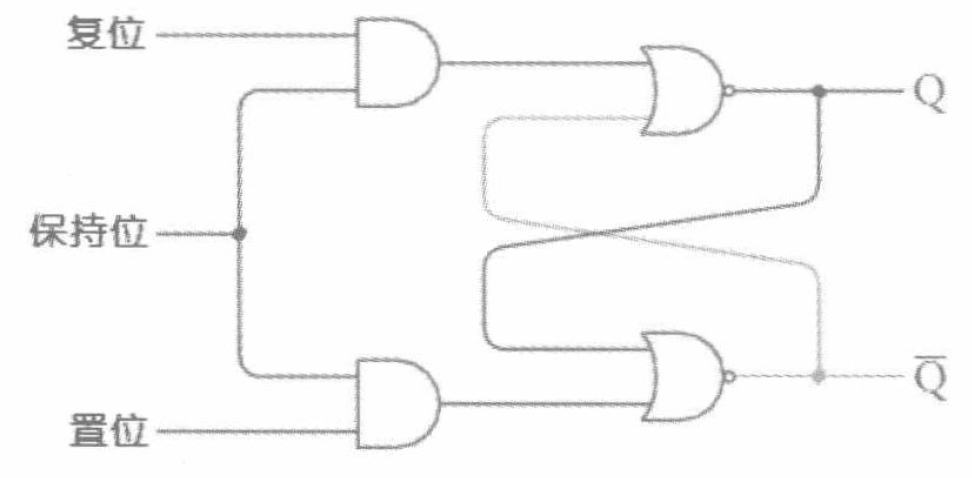

基于R-S触发器,再加上两个与门,就可以构造一个电路系统:

当保持位是0,复位和置位都不会对电路产生影响。当保持位是1时,这个电路就是R-S触发器。但是这个电路有一个弊端,那就是输入是三个而不是两个,我们可以把复位和置位当做一对相反数,因为其余的情况可以认为不是有效的输入,此时我们可以用一个数字来表示复位和置位,那就是数据端,数据端表示置位信号,取反后的值表示复位信号,对应的电路如下:

保持位是0时,电路不受影响。保持位为1时,Q等于数据端的值。若保持位再次变成0,电路的状态不变,相当于记住了保持位最后一次置为1时数据端输入的值。直到保持位再次被置为1的时候,又可以重新记忆了。

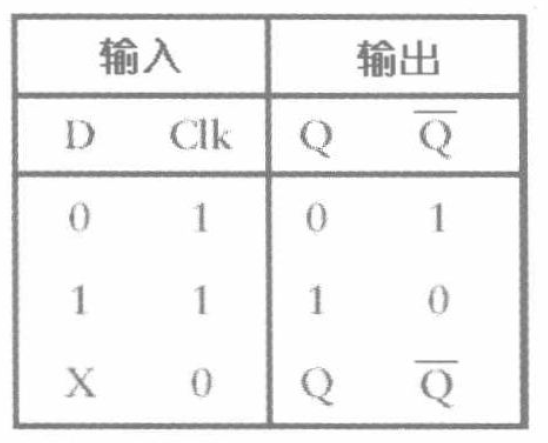

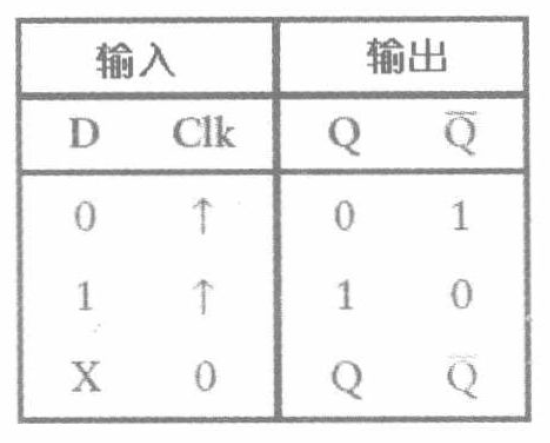

这个电路被称为电平触发的D型触发器(或者D型锁存器),所谓电平触发就是只有当保持位为1时,电路才有保存功能。保持位也可以被称为时钟端,如果数据端简写为D,时钟端简写为Clk,其功能表如下所示:

用锁存器改进加法

当计算三个二进制数字的加法时,就可以利用锁存器来记住两个数字的和,然后再次进行加法得到结果。

我们可以制作一个8位锁存器:

上面的8个输入端为D,输出端标记位Q,Clk为时钟,当时钟信号为1时,D端的输入被送到Q输出,当时钟信号为0时,这8位值将保持不变,直到时钟信号再次被置为1.

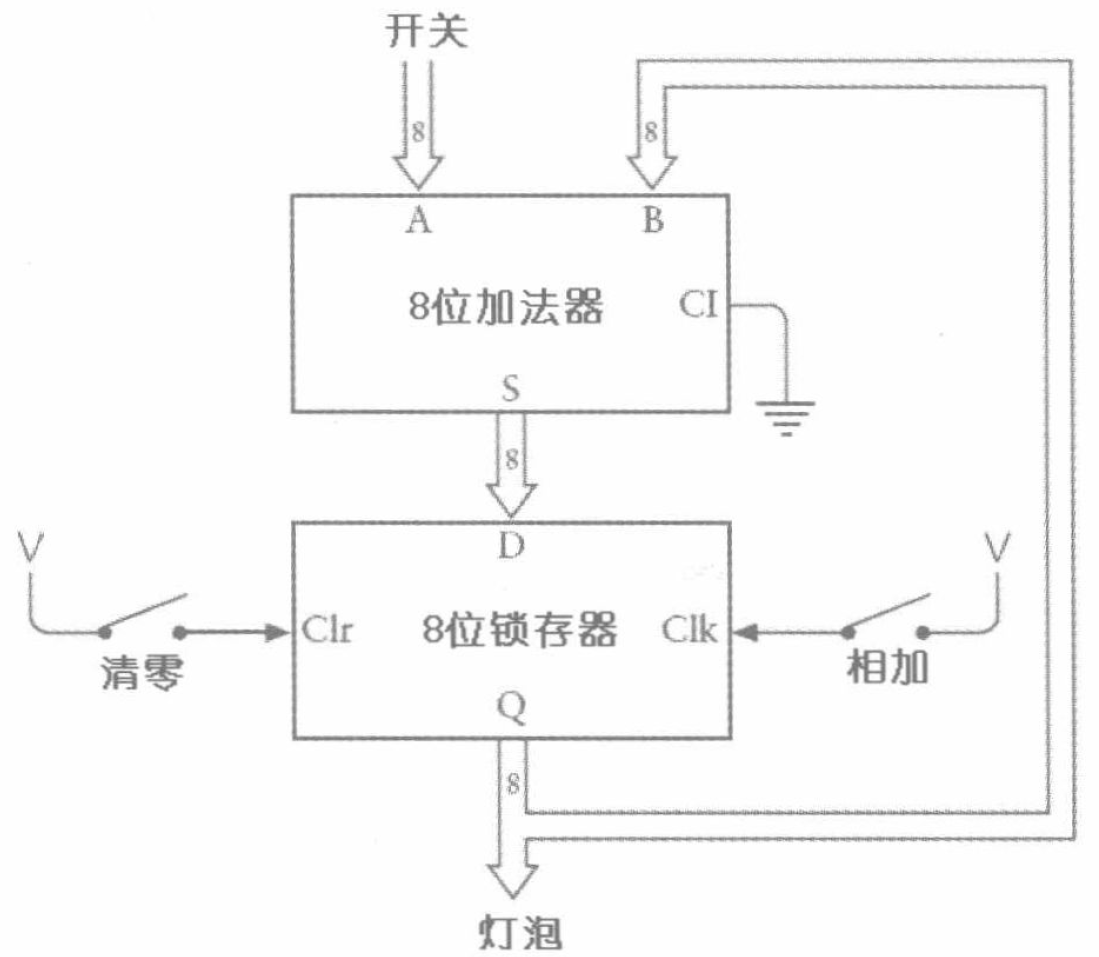

改造后的8位加法器如下:

标记位Save保存的开关是锁存器的时钟输入,当闭合的时候会存放加法的计算结果。第一次计算的时候,2-1选择器的开关是断开的,此时两个数据来自于开关,当选择器的开关闭合,就表示其中一个数据来自锁存器。

其中选择器的电路和真值表如下:

利用锁存器可以完成多次加法的实现,我们需要在原来的触发器基础上加上一个清零开关:

清零信号输入1的时候,无论其他输入是什么,最后的Q都变为0,改进后的加法器如下:

首先按下清零开关,让锁存器的输出变为0,使用开关输入一组数组,然后闭合相加开关,将第一个数字保存并输出。然后输入第二个数字,继续相加,反复操作可以连续进行许多次加法运算。

边沿触发器

边沿触发时钟输入和电平触发不同,电平触发是当时钟输入为1时,数据才会开始影响电路,边沿触发是只有时钟输入从0变到1的瞬间,数据端输入才会影响电路。

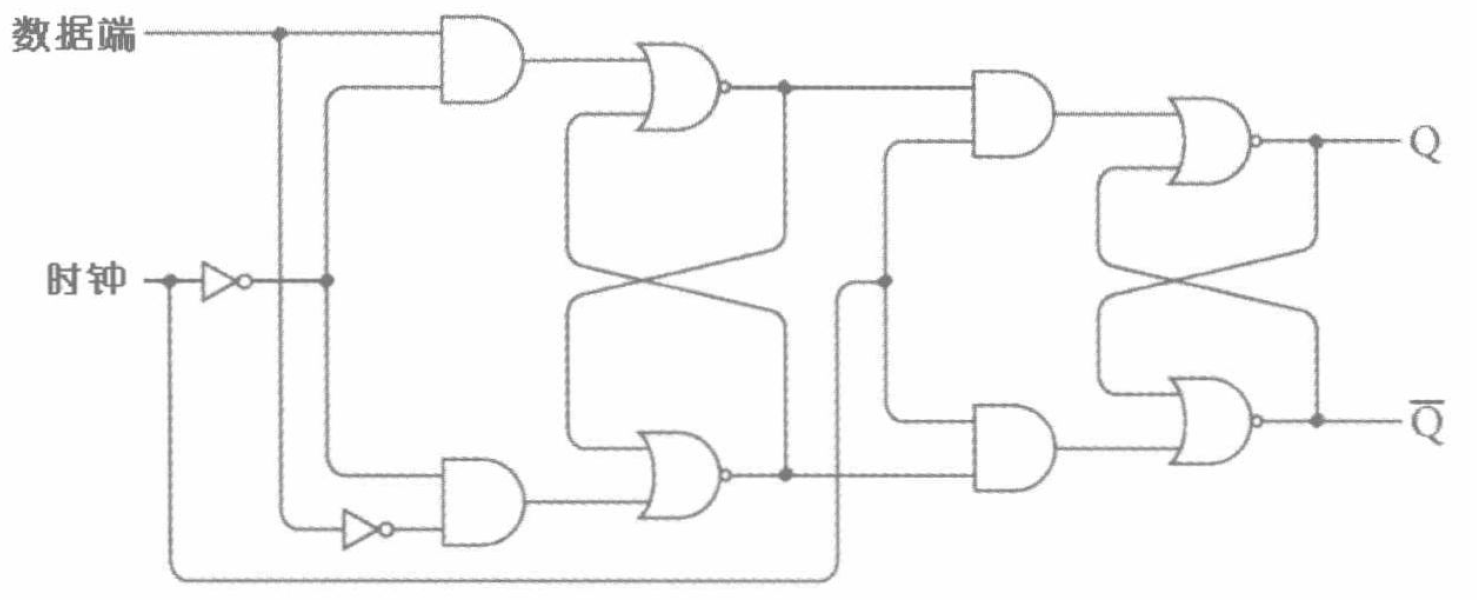

边沿触发的D型触发器是由两级R-S触发器连接而成的:

这里的时钟端输入控制着两个R-S触发器,值得注意的是在控制第一个的时候进行了取反操作,这意味着信号为0时保存数据。同时第二个触发器的输入是第一个的输出,当时钟信号为1时,第二个触发器的数据才能被保存。总之,只有从0变到1的瞬间,数据端输入才能保存下来。

该电路的真值表:

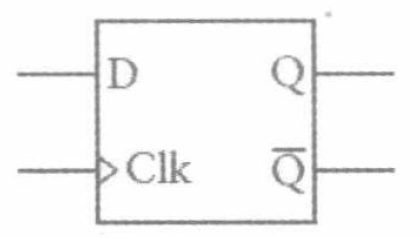

上箭头代表正跳变,相当于时钟端从0变为1.这个电路也可以用下列符号表示:

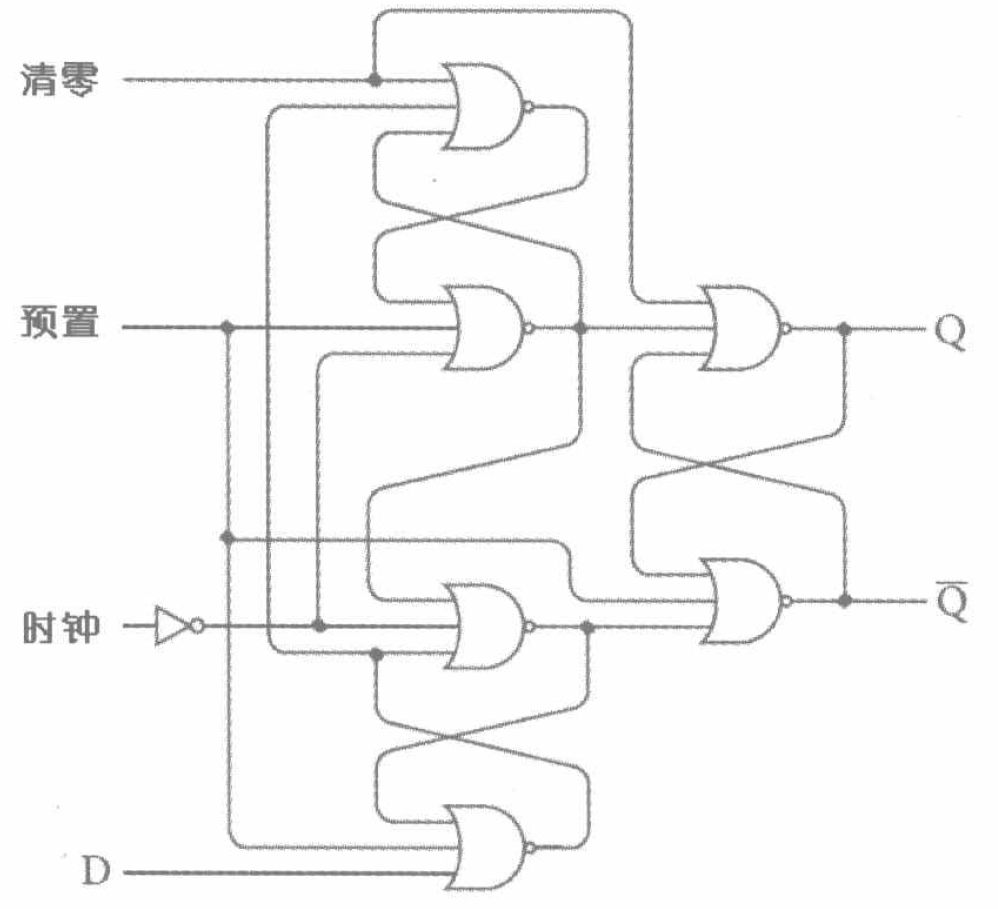

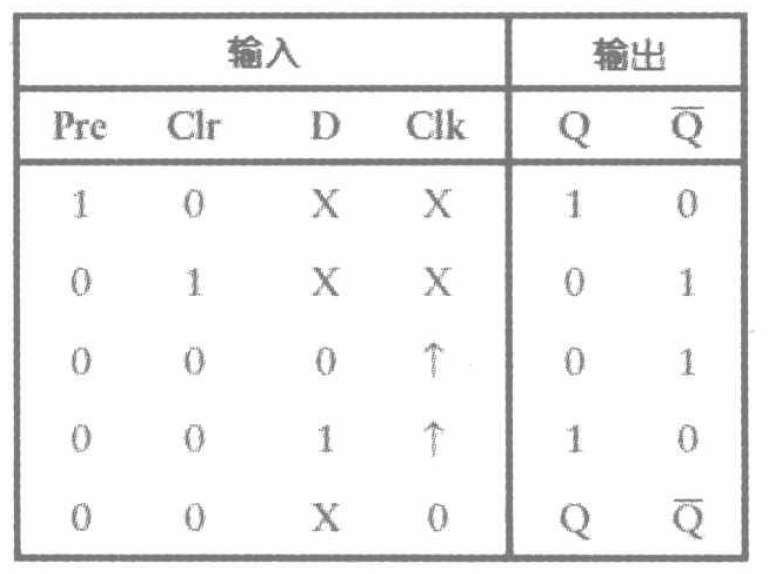

带预置和清零的边沿型D触发器

如下图:

当预置信号为1时,Q变为1;当清零信号为1,Q变为0,预置信号和清零信号不能同时为1,该触发器的原理和普通边沿触发器是一样的。

真值表如下:

可以用下列符号代表这种电路:

分频器和计数器

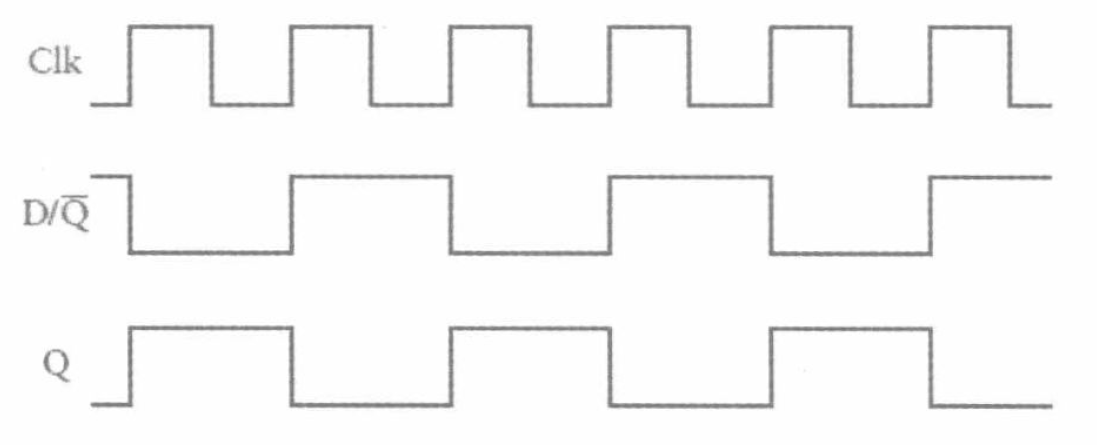

将振荡器和边沿触发的D型触发器连接起来:

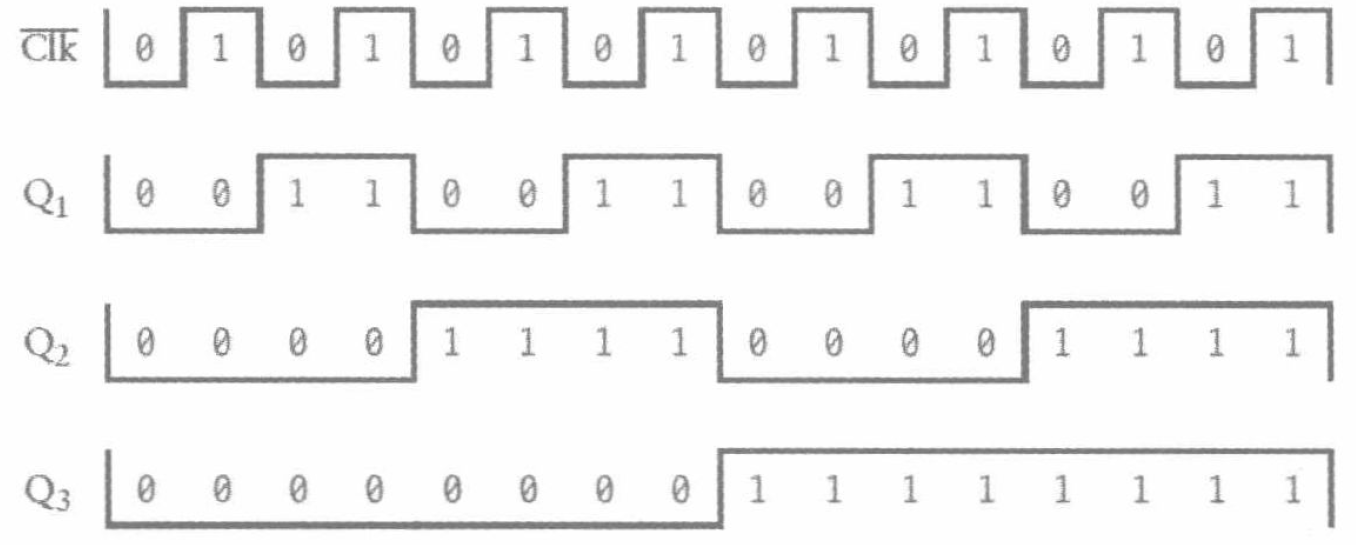

几个输出端的变化如下:

当时钟的值不断跳动,输出端的值也不断改变。如果这个振荡器的频率是20Hz,那么Q的输出频率就是10Hz,因此该电路被称为分频器。

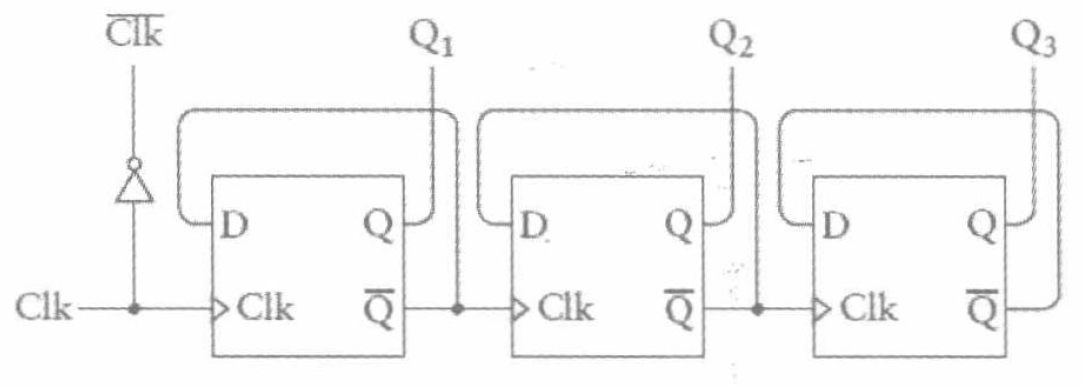

分频器的输出可以作为另一个分频器的时钟输入,再一次进行分频,如三个分频器连接在一起:

当把信号变化规律加上0和1后:

也就是根据时钟输入,不同的时间可以输出不同的Q,这些Q和Clk组成了四位的二进制数字。可以发现,第一个数字是0000,然后是0001、0010等。连接在一起的分频器越多,可以表达的二进制数字也就越多。

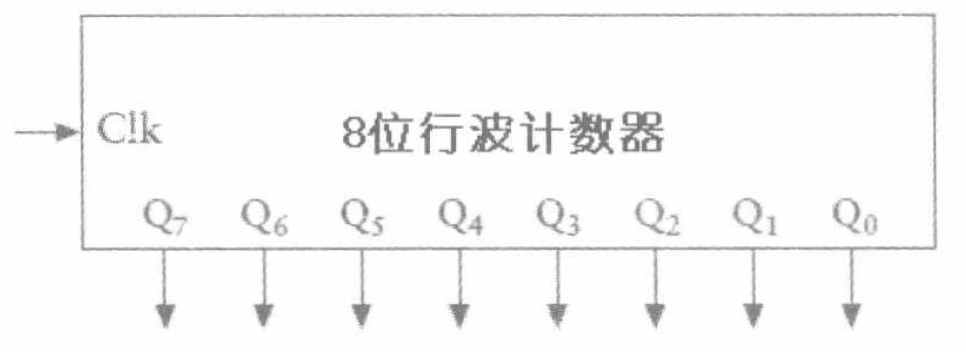

将8个分频器连接在一起,构成了一个8位计数器:

之所以称为行波计数器,是因为每一个触发器的输出都是下一个触发器的时钟输入,变化在触发器中一级一级传递,最后一级触发器的变化肯定有一些延迟,更先进的计数器是同步并行计数器,这种计数器中所有的输出都是在同一时刻改变的。

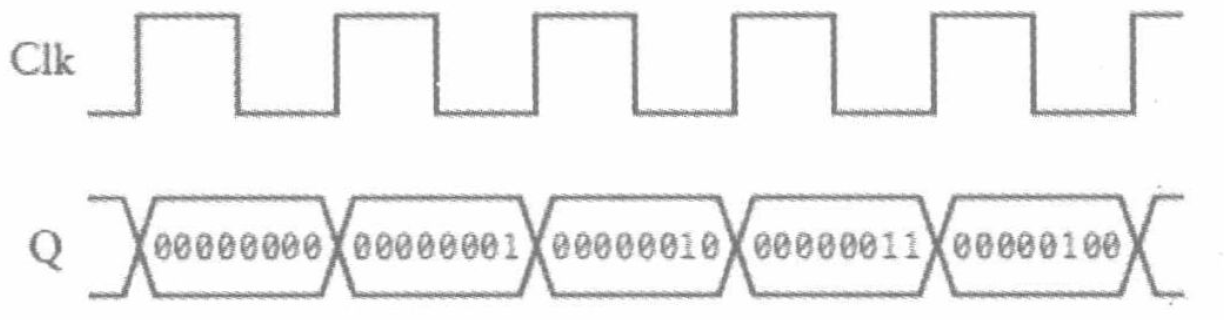

这样一个计数器的时序图可以用8个输出分别表示出来,也可以将它们作为一个整体表示出来:

当时钟信号发送一个正跳变,输出的二进制数字就加1。这里可以根据输出数字的变化规律反推振荡器的频率。