在看 《深入理解计算机系统》(CSAPP)第6章存储器层次结构 的时候突然想到在java并发编程 中的 可见性的问题,在这里简单记录一下,也不一定正确 ^_^

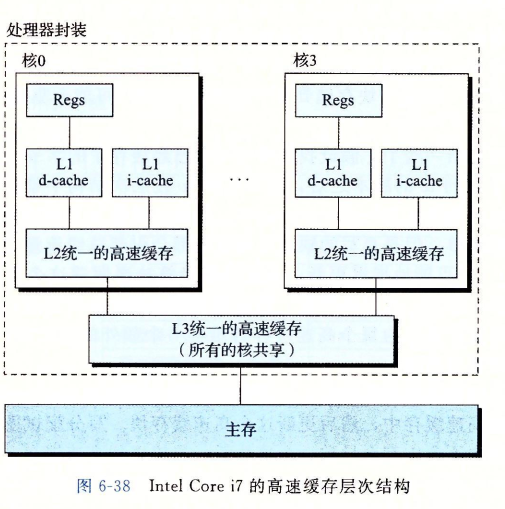

我们从上面的图中可以看到Intel Core i7 中有4核,每一个核心中都有独立的L1 L2 高速缓存, 四个核心共享L3高速缓存。

假设L1 L2高速缓存在数据写的时候采用的是写回的策略,简单来说就是仅仅更新高速缓存中的数据,这有在根据替换策略这条数据将要被新数据替换的时候才写回到更低层次的存储器中。

那么现在有这样的场景: 每一核中都运行着一个线程,而这些线程共享同一变量a,如果线程0(运行在核0)对变量a执行写操作,那么从图中我们可以看到仅仅会更改核0中的L1高速缓存,另外三个核上运行的线程在写回操作(准确的说是 核0需要至少写回到L3,而另外三个核重新从L3读)前是不会看到这次写操作的,这就是并发编程中的写可见性问题。

以上这是暂时的理解,留作记录以后补充。