1.实现了预定功能!整个工程,没有使用例程的25MHZ,全部统一使用50MHZ。

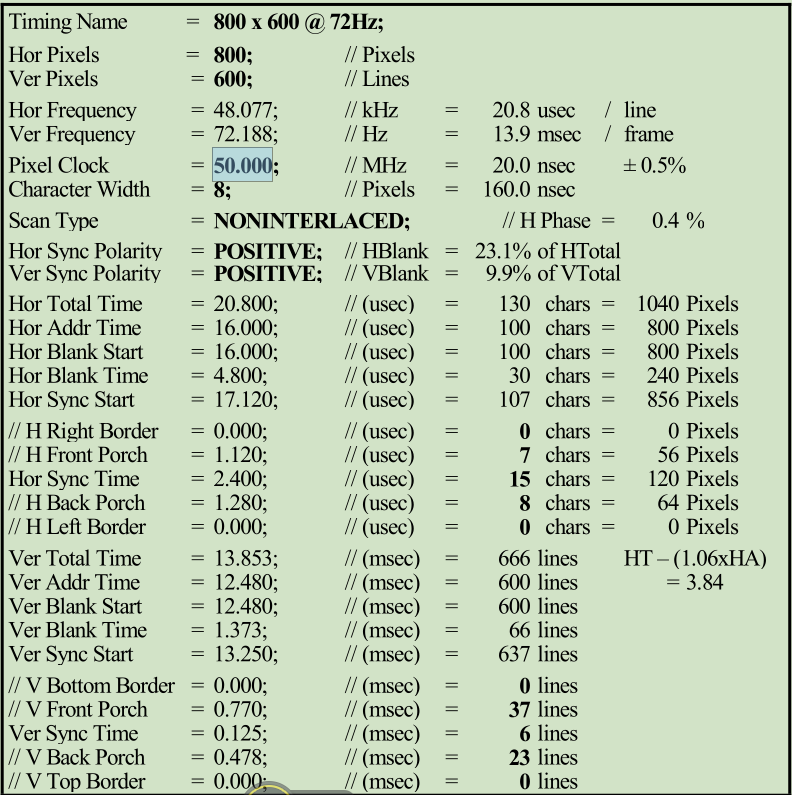

2.分辨率使用了800*600@72HZ。

3.实现了只显示白色部分,黑色部分RGB == 0,要显示背景色。

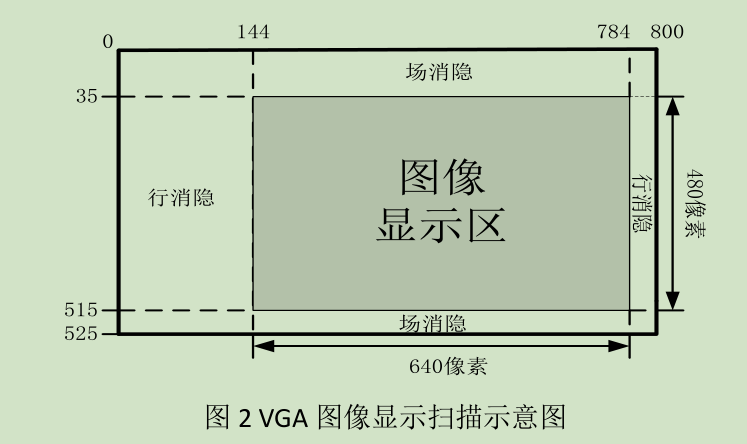

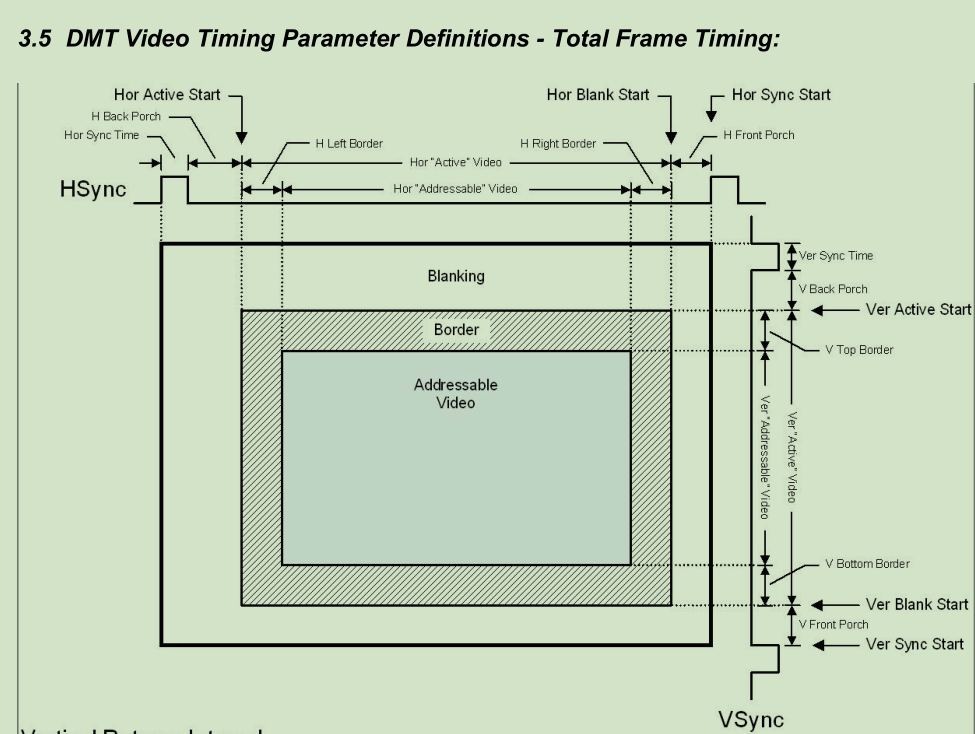

VGA图形基础知识,关键参数:

建立工程步骤

ISE打开

建立PLL IP核。

tool---->core Generator---->左下角输入 clock----》菜单栏新建工程----》clock wizard---->输入50MHZ,输出25MZH----》返回工程 add source--->添加**.xco,以及**.v。

添加约束:

工程右键 new source--->Implentation constrains file---->点击菜单栏右侧灯泡----》ucf---->FPGA---->io---->SINGLE ended---->spantan 6-->input attribbute---->copy到ucf文件

编辑ucf文件

看原理图,查看IO引进号,写上电压等级

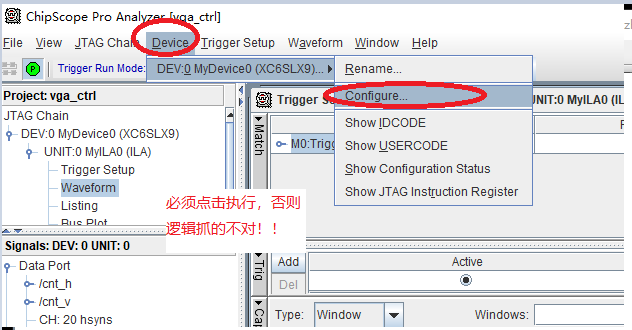

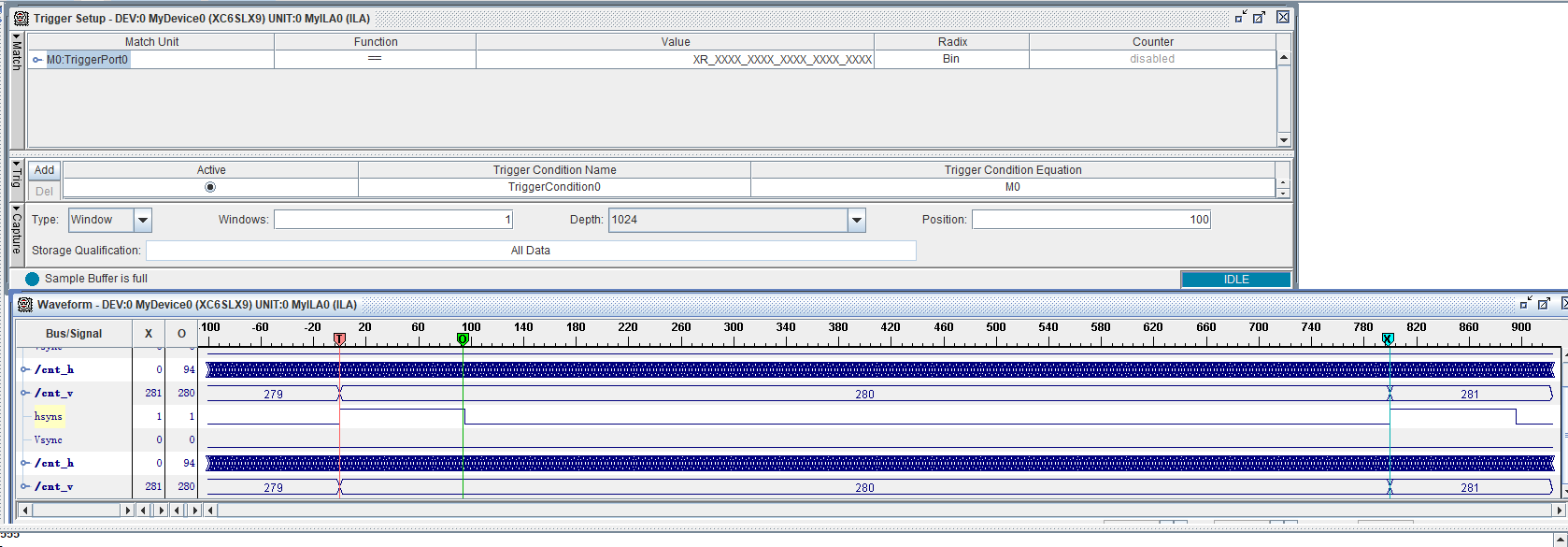

添加chipscope示波器,工程右键 new source---省略。创建后可以在工程下面看到*.cdc文件,双击设置下逻辑分析仪的参数。

注意:

下图里面菜单必须点击,否则执行时序不对,作用是将bit文件down进板子!

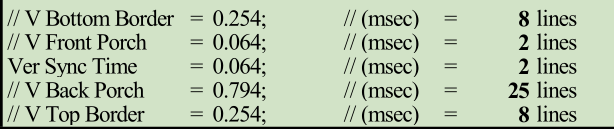

本人显示器不支持例程分辨率,改为800*600@72HZ。参数如下:

从上图看出,行列扫码总像素是1040*666pixel。

VGA动态移动图形

关键在于思路,只要做好移动变量x,y的增加,减少,以及这两个方向的flag,就可以完美控制方框的移动了!

最终实现了图形移动显示。