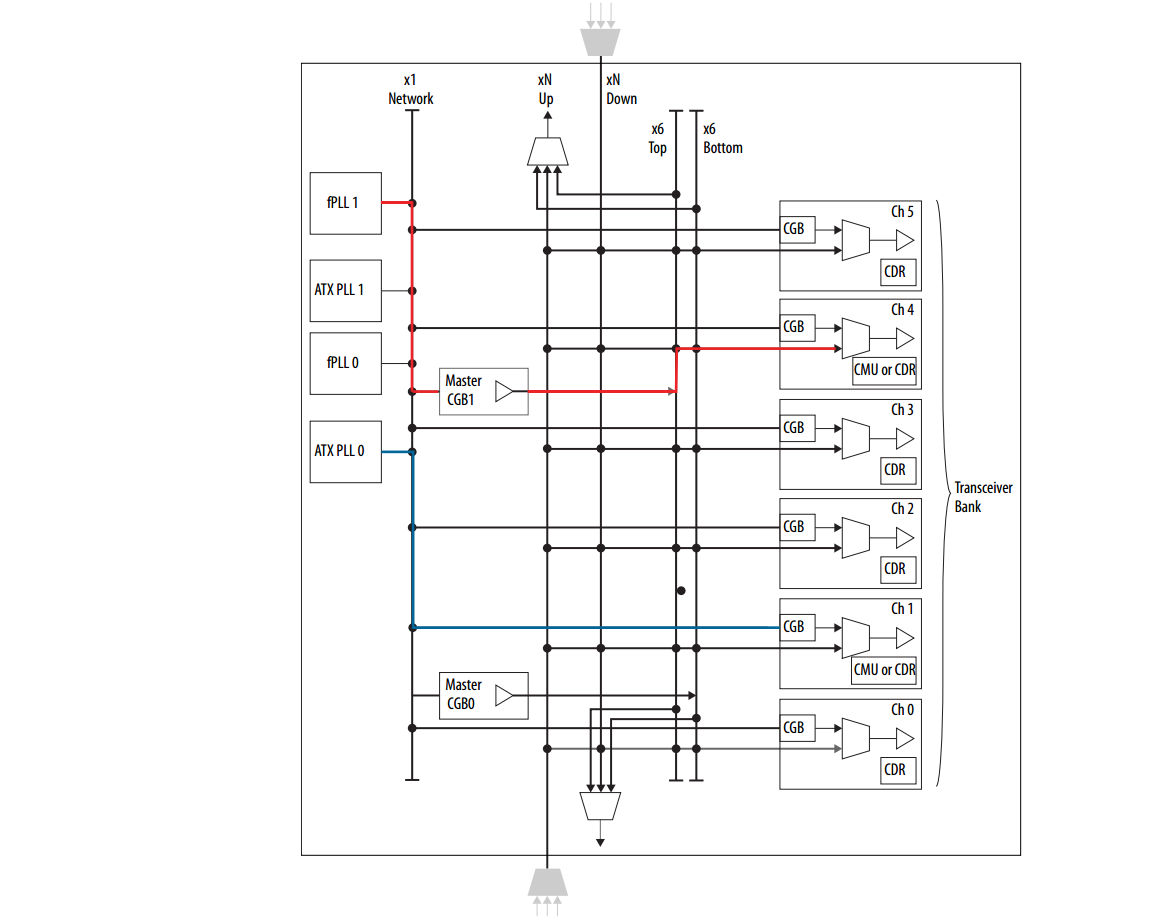

发送器时钟网络由发送器PLL到发送器通道,它为发送器提供两种时钟

高速串行时钟——串化器的高速时钟

低速并行时钟——串化器和PCS的低速时钟

在绑定通道模式,串行和并行时钟都是由发送器的PLL提供给发送器通道的。在未绑定通道模式,只有串行时钟到发送器通道,并行时钟由通道内部生成。

4种类型的发送器时钟网络:

x1时钟线

x6时钟线

xN时钟线

GT时钟线

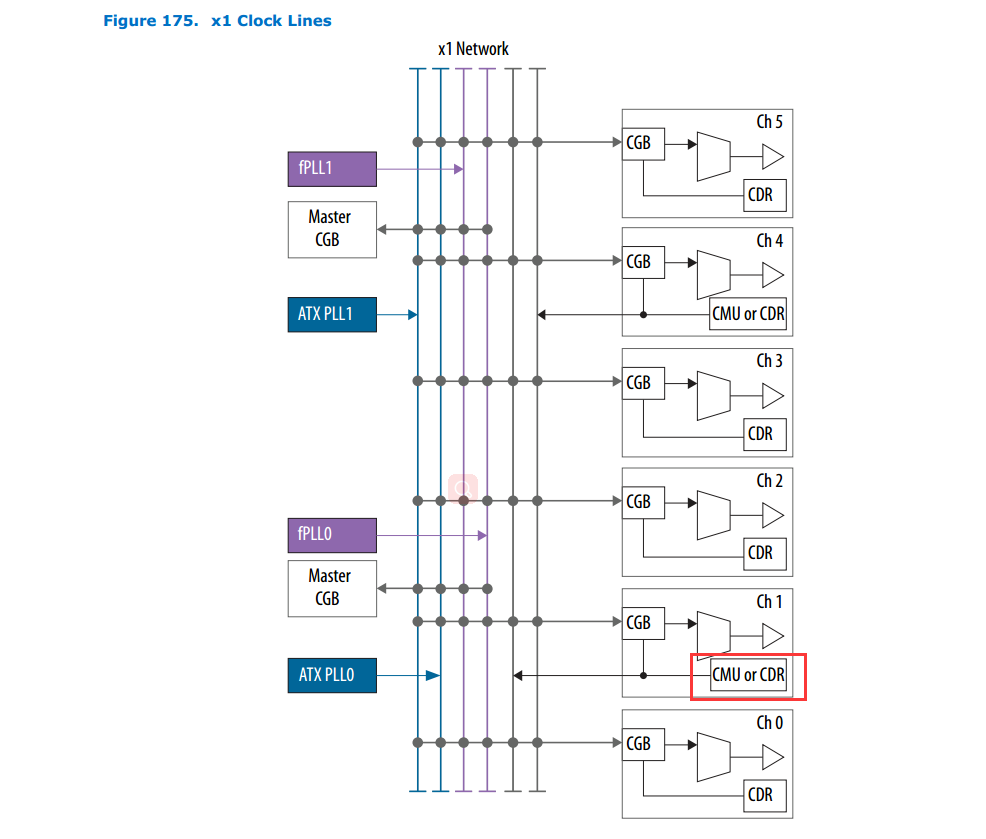

x1时钟线

x1时钟线将一个PLL的高速串行时钟输出路由到任何信道在一个收发器Bank,x1时钟线可以由收发器Bank中的ATX PLL,fPLL或者任意一个通道PLL(通道1和4用于CMU PLL)来驱动。

从上图可以看到fPLL ATX PLL和CMU可以流向x1时钟线,而CGB(包括MCGB和LCGB)则由x1时钟线流入。

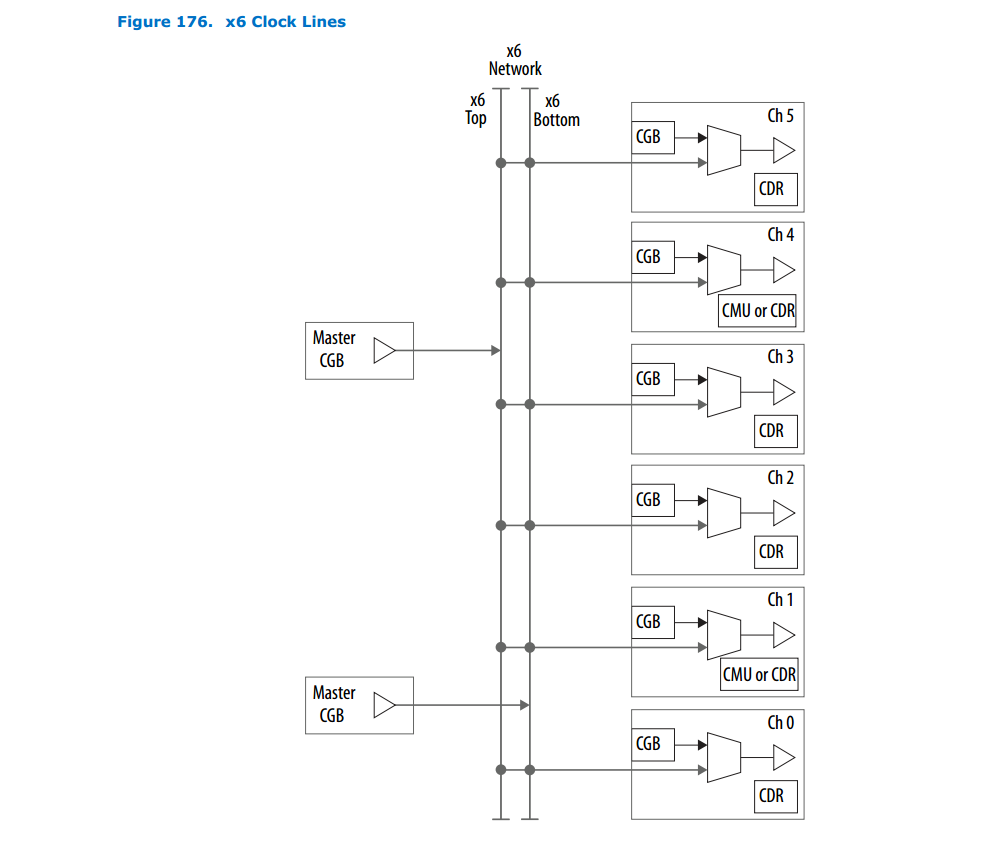

x6时钟线

x6时钟线分部在收发器Bank内,x6时钟线由CGB驱动,MCGB只能由ATX PLL或者fPLL驱动。CMU PLL则不可以。每个收发器Bank有两个x6时钟线,每根线对应一个MCGB,任何一个通道可以由x6时钟线驱动。x6时钟线还驱动xN时钟线,xN时钟线可以连接到相邻的Bank中去。

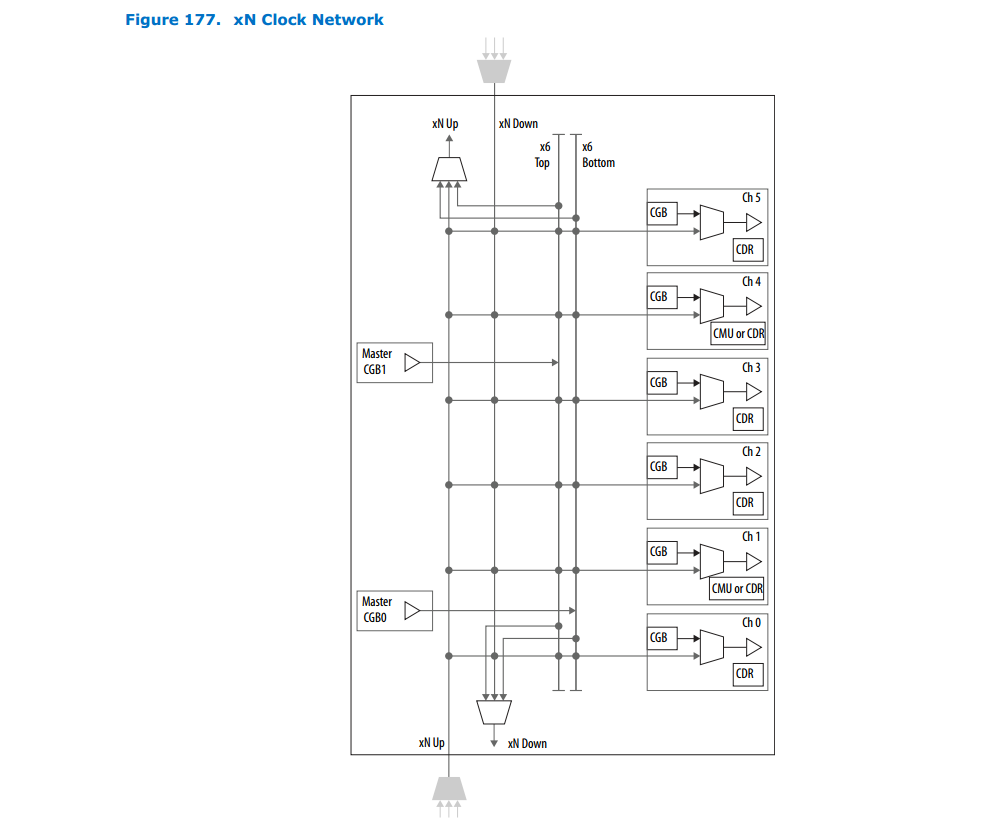

xN时钟线

xN时钟线把收发器时钟连接到多个收发器Bank上去

MCGB驱动x6时钟线,x6时钟线可以驱动xN时钟线。有两xN时钟线,xN上和xN下,xN上时钟线连接到MCGB上面的收发器Bank,xN下连接到MCGB下面的收发器Bank。xN线可以用于绑定和未绑定模。式。xN时钟线的最大跨度是相邻的上面两个和下面两个MCGB。在单个绑定组和一个非绑定xN组,最大是30通道。

无论是在绑定还是未绑定模式,xN时钟线支持的最大数据速率由收发器提供的电压决定。

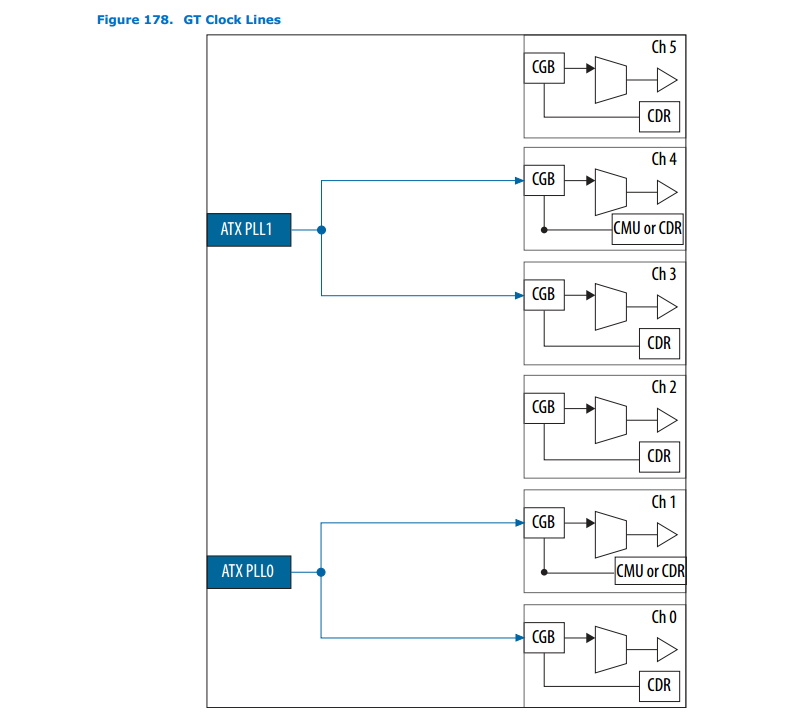

GT时钟线

GT时钟线只在Arria10 GT器中。GT时钟线旁路掉其余的时钟网络,可以提供更高的性能,这些通道只用于非绑定配置。每个ATX PLL有两个专用的GT时钟线,由PLL直连到收发器通道。顶部的PLL驱动通道3和4,底部的PLL驱动0和1

时钟生成块

LCGB

MCGB

每个通道都有一个LCGB,在未绑定模式,PLL提供串行时钟驱动LCGB,LCGB生成并行时钟用于串化器和PCS。

在每个发送器Bank有两个独立的MCGB,MCGB与LCGB提供相同的功能。MCGB的输出可以通过x6时钟线连接到同一个Bank内别的通道,也可以通道xN时钟线连接到别的收发器Bank,每个发送器通道有一个复用器来选择时钟源是来于local CGB还是master CGB。