综合之后,发现没有错误,下面开始进行仿真

因为比较简单,因此这里直接用波形文件去进行仿真,以后再用TB文件去仿真

1.新建波形文件

NEW --

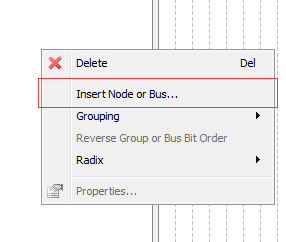

点击ok,在出来的对话框左边空白处右击,选择Insert Node of Bus

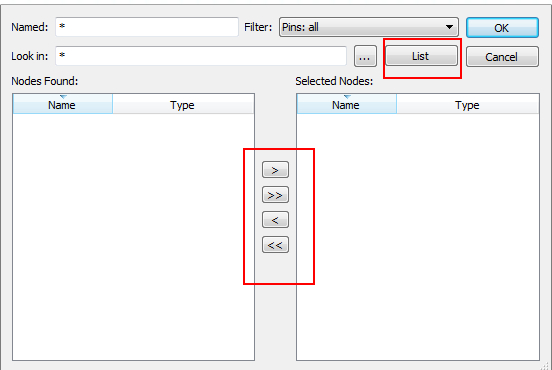

显示如下:

选择,node finder

选择List,然后把需要添加的,添加到仿真中,如下图:

点击ok

2.下面添加仿真激励

选中CLK这一行,然后选择上面时钟按钮

周期选择50MHz

RST_n引脚设置如下:

保存设置

重新综合一下代码

点击上方的功能仿真按钮

发现没有波形

通过查看设置结束时间发现:只能是10-100us。因此还是要用TB文件去进行仿真。

3.生成TB文件

选择processing -- start -- start testbench template writer

然后自己在工程目录下找到并打开(simulation文件夹下面的.vt文件)

然后修改代码如下:

首先,精度要改为1ns

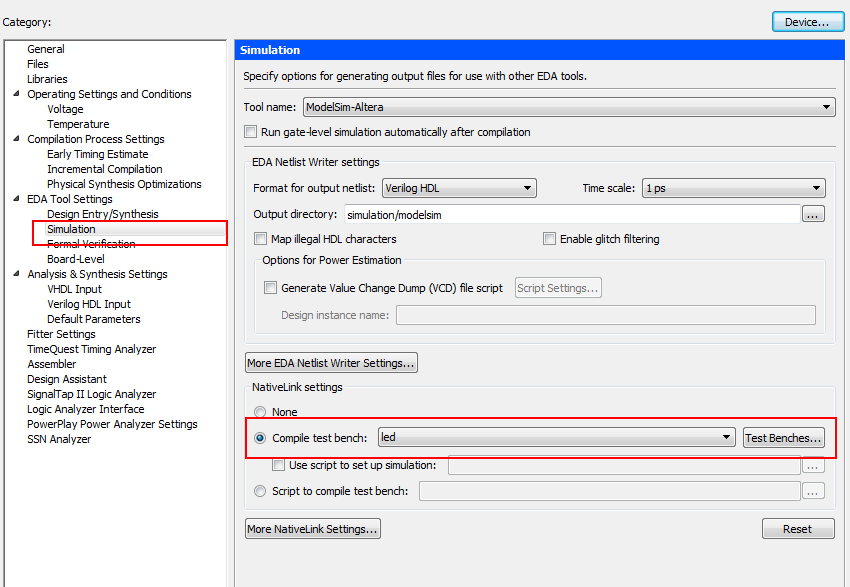

4.然后对仿真进行设置

打开工具栏里的settings按钮

点击test benches

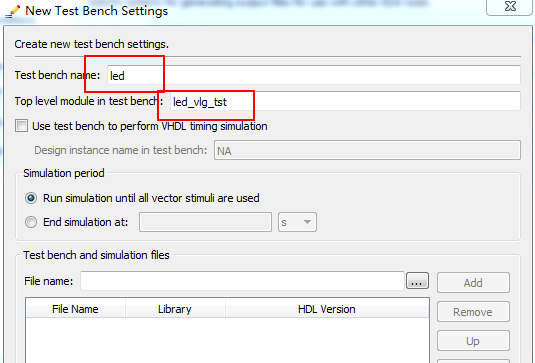

选择 new

用记事本打开.vt文件

填入到上面的两个框里,并选择对应文件添加,完成后显示如下:

点击ok

然后重新编译一下工程

点击工具栏里面的功能仿真按钮,启动仿真

仿真结果发现输出一直没变化,怀疑是因为计数值太大了,因此改小一点(只验证逻辑功能)

再重新编译,启动仿真

终于可以看到变化~~~