异步fifo,解决跨时钟域的数据传输问题。

由binary,gray两种counter组成,在读写domain之间,只传输gray code。

主要的设计难点在empty和full的产生中。

empty信号在read domain中产生,full信号在write domain中产生。

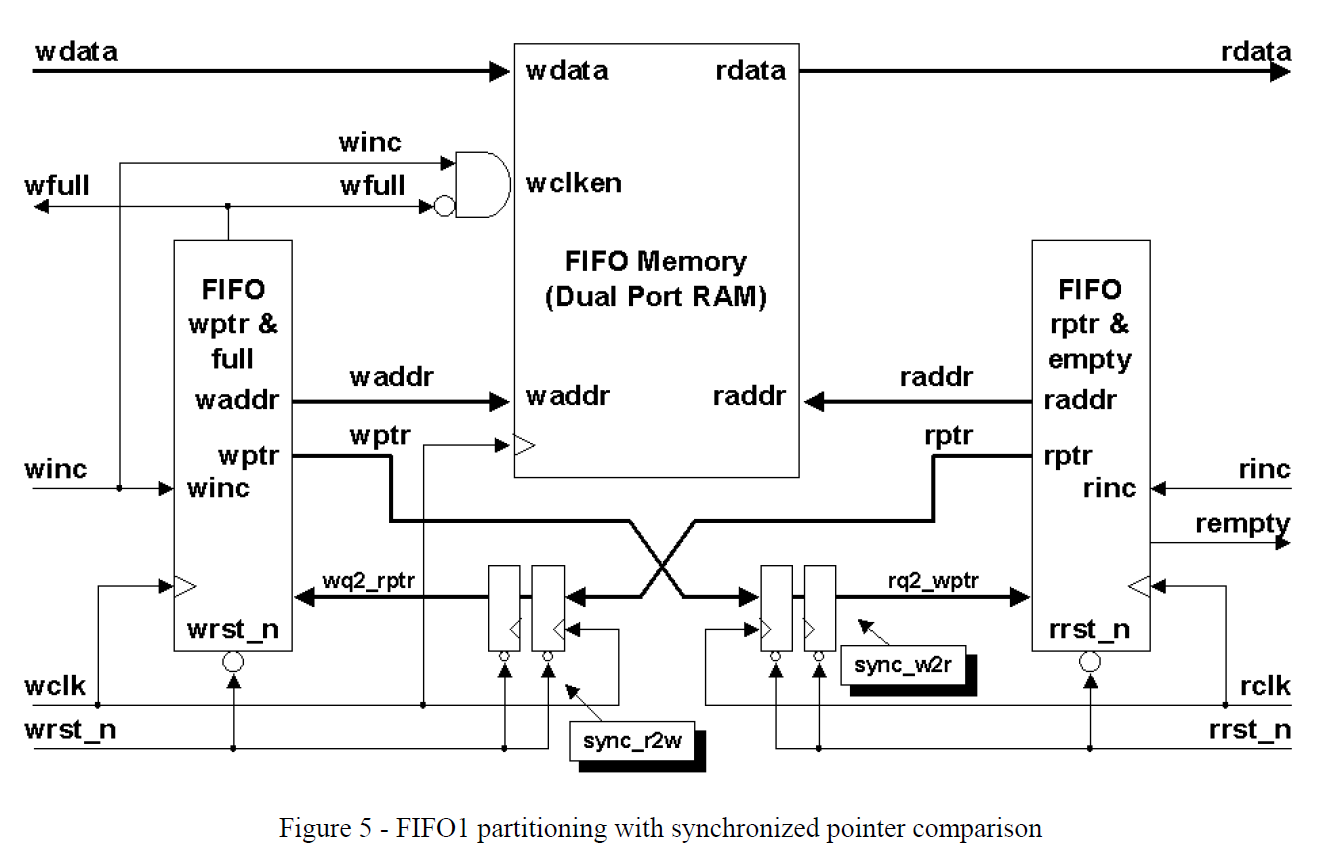

fifo设计框图:

ptr表示读写的gray编码地址,ptr之间的cdc,完成empty和full信号的有效生成。

中间的双口ram,接收读写addr/data。

Binary counter会出现多位变化,所以多使用gray counter。尽管gray counter只能应用在2^n深度中。

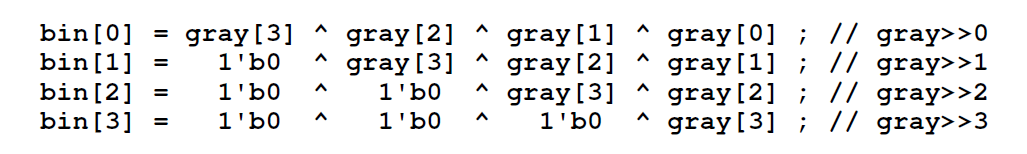

Gray-binary的conversion

binary-gray的conversion

异步FIFO中的两种结构:

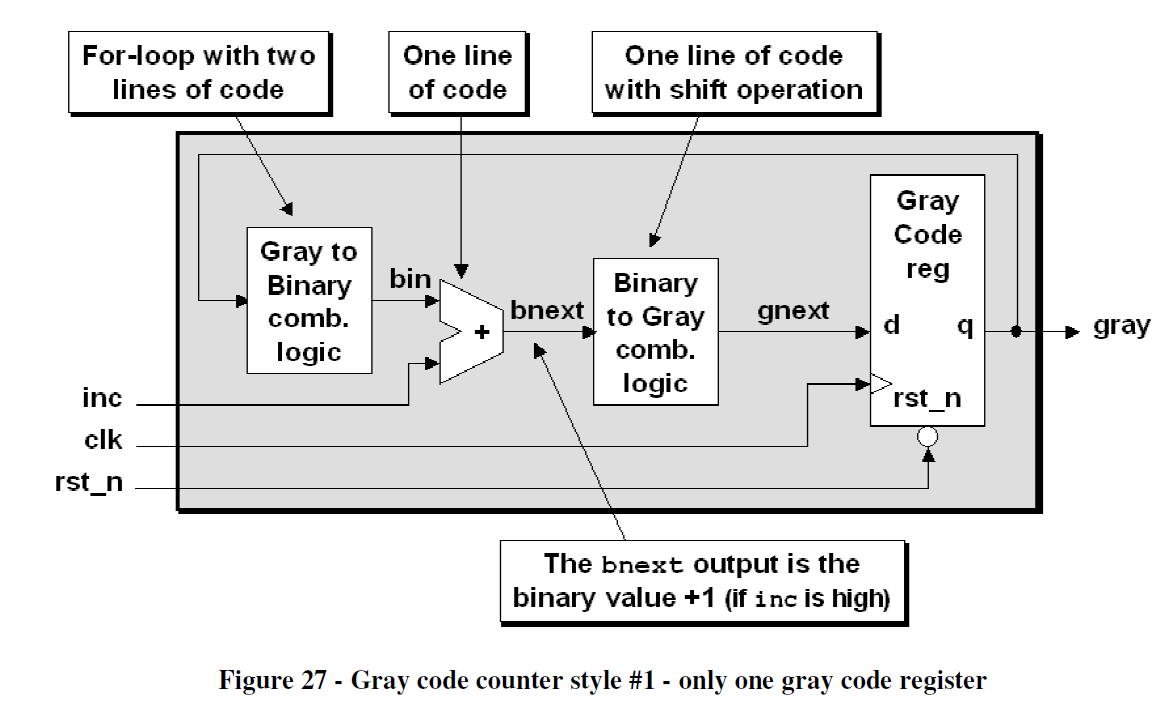

1)只含一个寄存器

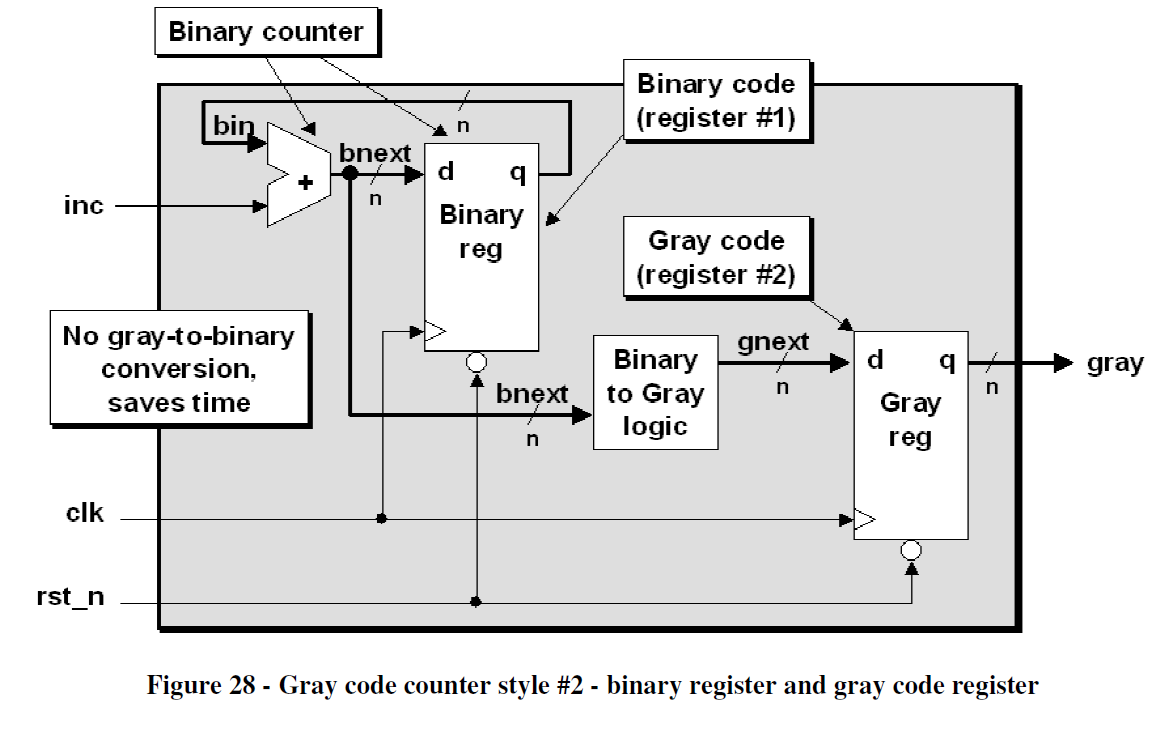

2)含有两个寄存器,但是少一个conversion的逻辑

gray到binary的转换主要是为了进行自加运算。

在empty和full信号的产生过程中,需要增加一比特来进行判断。如4bit的ptr,只有下三位用于计数,

最高位用于循环,在wptr[2:0]=rptr[2:0]时,根据wptr[4]和rptr[4]的值来判断full和empty。

但是当fifo中使用gray code来判断full/empty时,就无法用这个方法。

所以实际中,可以维护两个gray counter,一个Nbit,一个N-1bit。

N-ibit来进行判断低位的数据地址,高位N-1判断empty和full。

由于gray编码的如下特性:

可以将这两个gray counter合并,dual-nbit counter。

在7--->8和15--->0的转变中,会有两位的bit变换,不是标准的gray counter。

在实现中,可以通过case建模的binary到gray转换来实现。

当异步fifo两侧是faster--->slow,可能会出现sync gray code增加了两次才被slow clock采样到,

但这并不会出现multi-bit cdc 的错误。

因为本质上,sync gray code还是一位的变化,只是上一次未被采样而已,并不会造成各个信号

在clock沿附近,出现不同glitch的情况。

同样的当异步fifo两侧,faster--->slow,不会因为full-state的不及时,出现overflow,也不会因为

empty-state的不及时,出现underflow。

因为full状态在write domain产生,在faster--->slow的情况中,wptr的更新是及时的,

同样的empty状态在read domain,在faster---slow的情况中,不会出现empty情况,

如果是在slow---faster的情况下,rptr的更新也是及时的。

但是empty和full的deassert可能会由于同步通信,产生滞后,导致fifo效率降低,这是不能避免的。