所遇问题:通信接收机收端实例化一路无误码,实例化与之相同且独立的另一路时则两路输出都有误码。

问题定位:通过ila核分别抓取同步、均衡、译码的输出数据,发现直至均衡输出数据都正确,LDPC译码输出不正确。

解决思路:可通过配置综合和实现的优化目标来改善系统性能,并手动给高扇出的信号增加一级pipeline。

具体操作:系统鲁棒性的提高是以FPGA的空间资源和时间资源来换取的(即LUT的增加和时序裕量的减少),笔者所接手的项目这两项宝贵资源都不是很充裕,给系统调优提出了很多限制条件,常常是捉襟见肘。考虑到问题出在LDPC译码模块,且该模块占据了一半的系统LUT资源,为此想到通过时分复用的方式使得两路收端共用一路LDPC译码器,可大大降低系统资源。而将两路并行译码改为单路串行使用,收端的总处理时延势必会增加,这可通过提高译码器的处理时钟来解决。

本项目综合、实现和仿真优化的文字及图片说明如下:

Synthesis

(1)Strategy:Flow_AreaOptmized_high

(2)-flatten_hierarchy:none

(3)-fanout_limit:1000

(4)-directive:AreaOptimized_high

(5)-keep_equivalent_registers:打钩选中

(6)-no_lc:打钩选中

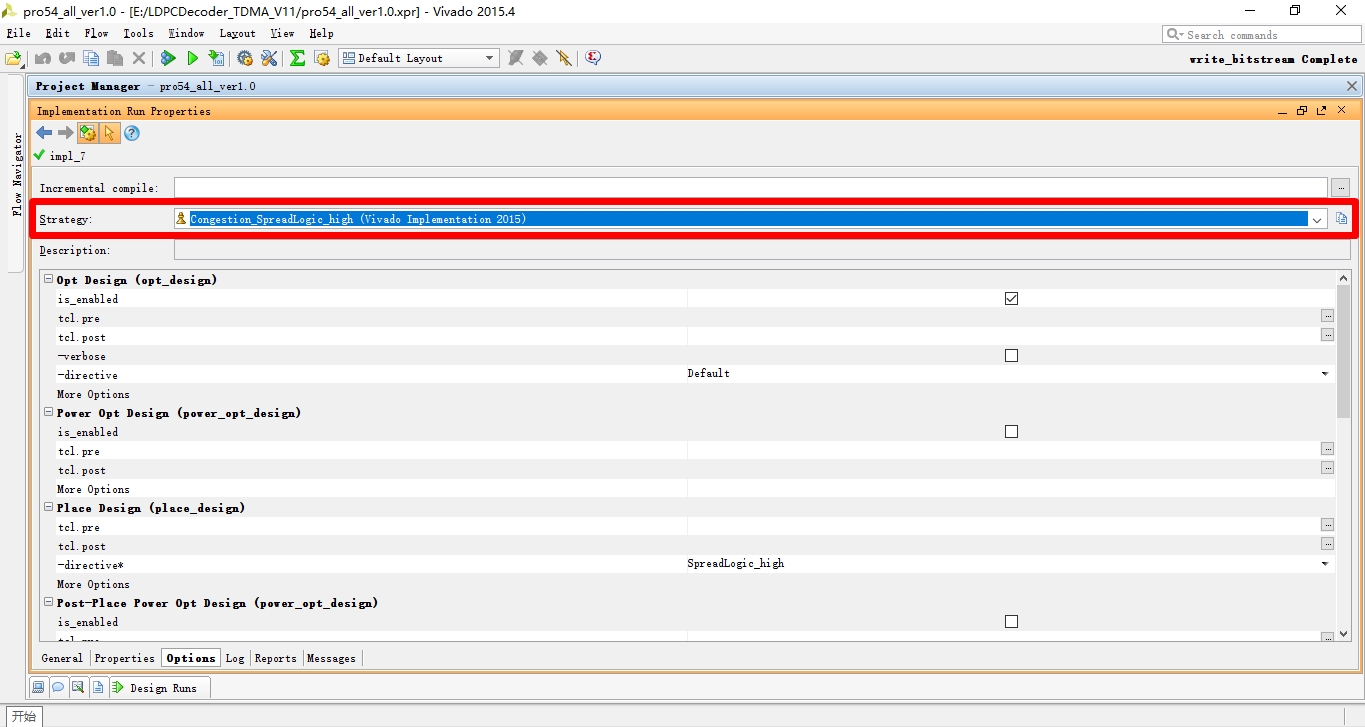

Implementation

Strategty:Congestion_SpreadLogic_high

Simulation

参考连接: