伪差分电平

所谓伪差分电平,就是信号在接收端是一个差分的接收器,但其中一端固定接参考电压,而另一端接单端信号线。输入信号电压与参考电压之间进行比较,作为判断输入信号高低的标准。

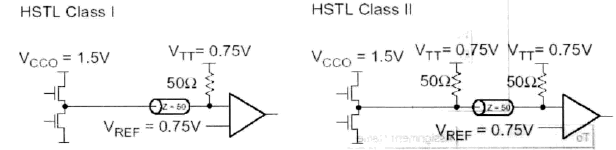

常用的伪差分电平标准有SSTL、HSTL等。如下图所示为HSTL信号电平连接关系图,其中分为CLASSI和CLASS II 。

伪差分标准的输出驱动器也是推挽式的结构(push-pull),而输入是差分的接收器,其中有一端接到固定的参考电平(Vref)上。

另外,伪差分电平的信号输出的摆幅较小,瞬态的电流较小,保持信号完整性要相对容易些。因此,这种电平主要应用在高速的存储器接口中,如DDR/DDR2 SDRAM、QDRSRAM、RLDRAM等,数据速率可以达到1067Mbit/s以上。

这种结构的好处是,其输入信号只需要在VREF上下小幅度摆动即可被输入驱动器正确接收。这样信号的噪声余量就很大,信号能否被正确接收下来,VREF将起到关键作用,因此,设计时需要保证VREF较高的精度。

当然,除了单端的HSTL和SSTL外,也有差分的HSTL和SSTL标准,如下图。

片上终端电阻

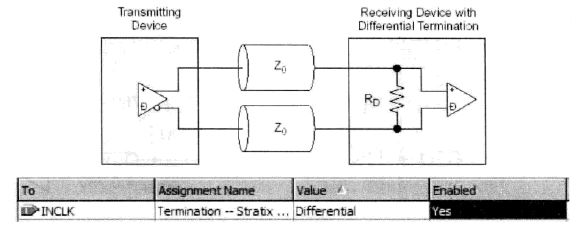

作为可编程的逻辑器件,ALTERA的FPGA支持多数业界主流的信号电平。在stratix IV系列的FPGA中,IO管脚带有片上终端电阻(OCT,on-chip termination),可以减少PCB上过多的分离电阻,影响PCB布线。所支持的OCT有两种,一种是输出端的源端串阻,可以用作SSTL电平的源端串阻或者是LVTTL/LVCMOS的源端阻抗匹配电阻;另一种是差分匹配电阻可以作为LVDS、HyperTransport的标准的接收端匹配电阻,如下图:

具体使用时,只需要在quartus ii工具的assignment editor中增加管脚匹配方式的约束即可。上图显示了具体的设置方法。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间