一、概念

建立时间和保持时间都是针对触发器的特性说的。

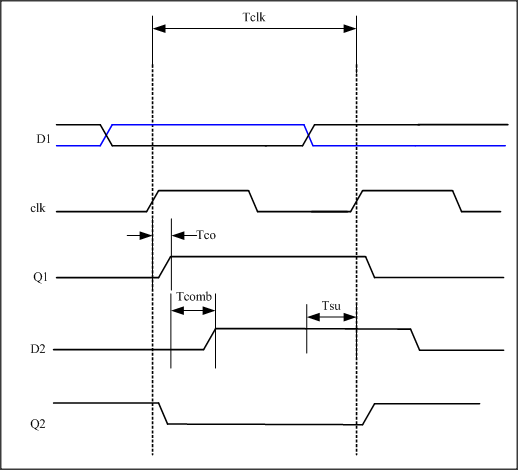

时序图如下:

建立时间(Tsu:set up time)

是指在触发器的时钟信号上升沿到来以前,数据稳定不变的时间,如果建立时间不够,数据将不能在这个时钟上升沿被稳定的打入触发器,Tsu就是指这个最小的稳定时间。

保持时间(Th:hold time)

是指在触发器的时钟信号上升沿到来以后,数据稳定不变的时间,如果保持时间不够,数据同样不能被稳定的打入触发器,Th就是指这个最小的保持时间。

输出相应时间(Tco)

触发器输出的响应时间,也就是触发器的输出在clk时钟上升沿到来之后多长的时间内发生变化,也即触发器的输出延时。

二、数字系统设计常见与之有关的问题

1、问题提出

数字系统设计常见的电路图,这里需要保证数据能够正确的在这两个触发器上进行传输,由此确定中间组合逻辑电路的传输延时的范围。

Tcomb: 组合逻辑电路的传输延时

2、第二个触发器要满足建立时间的约束条件

时序图如下,假设D1的输入为图中的蓝线所示

时序解释:

在第一个时钟上升沿,前边的触发器采集D1信号,将高电平打入触发器,经过Tco的触发器输出延时到达组合逻辑电路。又经过组合逻辑电路的延时Tcomb(我们假定组合逻辑电路此时没有改变信号的高低,可以把它假定为一个缓冲器)送到了D2接口上。在第二个时钟上升沿到来之前,D2数据线上的信号要满足稳定时间>触发器的建立时间Tsu。

Tclk - Tco - Tcomb > Tsu

考虑最坏的情况:触发器的输出延时最大,组合逻辑电路的延时也最大,可得:

Tclk - Tco-max - Tcomb-max > Tsu

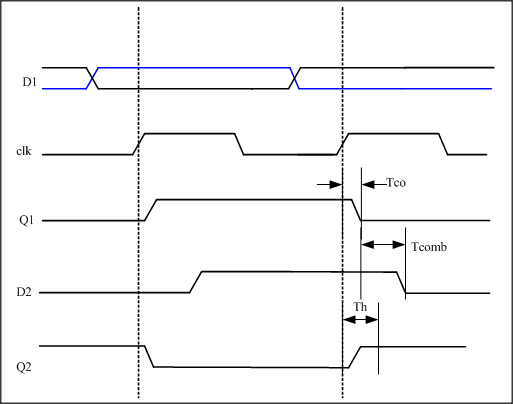

3、第二个触发器要满足保持时间的约束条件

时序图如下,假设D1的输入为图中的蓝线所示

时序解释:

接着之前的时序图继续,在第二个时钟上升沿前边触发器采集到D1上的低电平,经过Tco的延时在Q1上得到表达。这个低电平在经过组合电路延时Tcomb到达D2。现在的问题是经过这么Tco+Tcomb的延时,D2上原本的高电平在第二个时钟上升沿到来之后的稳定时间 > 第二个触发器的保持时间。满足了这个条件,后边的触发器才能稳定的接收到最初由D1传过来的高电平。

Tco + Tcomb > Th

考虑到最坏的情况:触发器的输出延时最小,组合逻辑电路的延时也最小

Tco-min + Tcomb-min > Th

4、问题的答案

我们得到中间组合逻辑电路的输出延时范围为:

(Tclk - Tco-max - Tsu) > Tcomb > (Th - Tco-min)

参考资料:

附visio时序图: