实验室板子soc-de1自带的7928芯片,下面记录一下它的参数

吞吐速率 : 1MSPS

吞吐速率 : 是指ADC器件单位时间内能处理的任务数或输出结果的数量。单位:SPS(Samples per second)

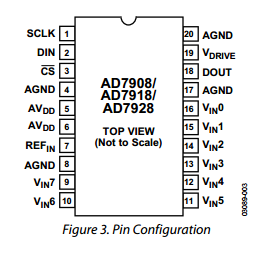

通信协议·:SPI协议 四根线 SCLK DIN SOUT CS_N

引脚配置和功能描述:

SCLK 串行时钟

DIN 数据输入,在SCLK的下降沿写入寄存器

CS_n 片选控制,在低电平时,数据有效

REFin AD7928的基准电压输入。

Vin0至Vin7 模拟输入0到模拟输入7.通过控制ADD2到ADD0来选择通道,输入电压范围0~REFin 或者 0~2REFin

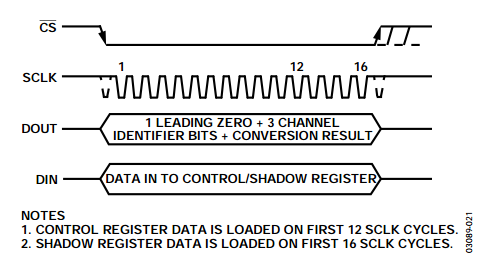

DOUT 数据输出。AD7928的转换结果在SCLK的下降沿逐个输出。输出的数据流包含一个前置的0和3个地址位

然后是12个转换数据位(MSB优先)。输出的数据可以是二进制或者二进制的补码。

控制寄存器

每次数据传输需要16个串行时钟,只有在前12个SCLK的下降沿,提供的信息才会写入被控制的寄存器。MSB在前

WRITE : 1 后续的11位写入寄存器 0 则不写入

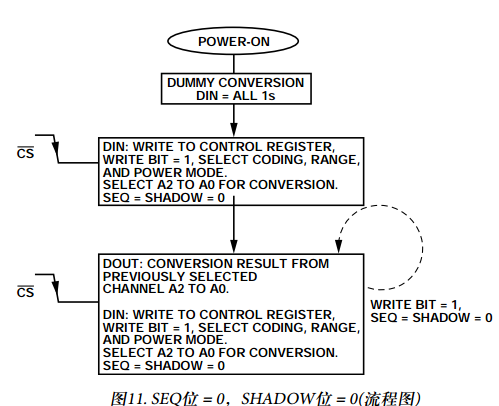

SEQ,SHADOW : 0 0 的话,序列功能未被使用,每次转换的通道由上一次的通道地址ADD2 ~ ADD0决定。

PM1,PM0 : 1 1 正常工作

RANGE : 0 则模拟输入的范围为 0 ~ 2XREFin 1则0~REFin

CODING : 0为二进制的补码方式,1则标准的二进制

下面给AD9854的时序控制图

驱动程序

/*----------------------------------------------------------------------- Date : 2017-08-01 Description : Design for AD7928. -----------------------------------------------------------------------*/ module ad7928 ( //global clock input clk, //system clock input rst_n, //sync reset //ad7928 interface output reg sclk_ad, output reg din, //逻辑输入 input dout, //逻辑输出 output reg cs_n, //片选使能端 //user interface output reg [7:0] ad_data // ); //-------------------------------- //Funtion : 10M 分频 parameter CLK_10M = 3'd5; reg [2:0] cnt_clk; always @(posedge clk or negedge rst_n) begin if(!rst_n) cnt_clk <= 3'd0; else if(cnt_clk >= CLK_10M - 1'b1) cnt_clk <= 3'd0; else cnt_clk <= cnt_clk + 1'b1; end wire clk_10m_value = (cnt_clk >= CLK_10M - 1'b1) ? 1'b1 : 1'b0; //-------------------------------- //Funtion : ad7928 参数定义 parameter SPI_DATA = 16'b100_000_11_0001_0000; parameter ONE_S = 32'd10;//_000_000; //-------------------------------- //Funtion : spi state reg [5:0] spi_state; reg [31:0] cnt_wait; reg [7:0] ad_ser_data; always @(posedge clk or negedge rst_n) begin if(!rst_n) begin spi_state <= 6'd0; ad_ser_data <= 8'd0; cnt_wait <= 32'd0; sclk_ad <= 1'd0; din <= 1'd0; cs_n <= 1'd0; end else if(clk_10m_value) begin case(spi_state) //上电等待 6'd0 : begin if(cnt_wait >= ONE_S - 1'b1) spi_state <= 6'd1; else cnt_wait <= cnt_wait + 1'b1; end 6'd1 : begin sclk_ad <= 1'b1; cs_n <= 1'b1; spi_state <= 6'd2; ad_ser_data <= 8'd0; end 6'd2 : begin cs_n <= 1'b0; spi_state <= 6'd3; end //1 6'd3 : begin din <= SPI_DATA[15]; spi_state <= 6'd4; end 6'd4 : begin sclk_ad <= 1'b0; spi_state <= 6'd5; end //2 6'd5 : begin sclk_ad <= 1'b1; din <= SPI_DATA[14]; spi_state <= 6'd6; end 6'd6 : begin sclk_ad <= 1'b0; spi_state <= 6'd7; end //3 6'd7 : begin sclk_ad <= 1'b1; din <= SPI_DATA[13]; spi_state <= 6'd8; end 6'd8 : begin sclk_ad <= 1'b0; spi_state <= 6'd9; end //4 6'd9 : begin sclk_ad <= 1'b1; din <= SPI_DATA[12]; spi_state <= 6'd10; end 6'd10 : begin sclk_ad <= 1'b0; spi_state <= 6'd11; end //5 6'd11 : begin sclk_ad <= 1'b1; din <= SPI_DATA[11]; spi_state <= 6'd12; end 6'd12 : begin sclk_ad <= 1'b0; spi_state <= 6'd13; end //6 6'd13 : begin sclk_ad <= 1'b1; din <= SPI_DATA[10]; spi_state <= 6'd14; ad_ser_data <= dout; //[7] end 6'd14 : begin sclk_ad <= 1'b0; spi_state <= 6'd15; ad_ser_data <= ad_ser_data << 1'b1; end //7 6'd15 : begin sclk_ad <= 1'b1; ad_ser_data <= ad_ser_data + dout; //[6] din <= SPI_DATA[9]; spi_state <= 6'd16; end 6'd16 : begin sclk_ad <= 1'b0; spi_state <= 6'd17; ad_ser_data <= ad_ser_data << 1'b1; end //8 6'd17 : begin sclk_ad <= 1'b1; din <= SPI_DATA[8]; spi_state <= 6'd18; ad_ser_data <= ad_ser_data + dout; //[5] end 6'd18 : begin sclk_ad <= 1'b0; spi_state <= 6'd19; ad_ser_data <= ad_ser_data << 1'b1; end //9 6'd19 : begin sclk_ad <= 1'b1; din <= SPI_DATA[7]; spi_state <= 6'd20; ad_ser_data <= ad_ser_data + dout; //[4] end 6'd20 : begin sclk_ad <= 1'b0; spi_state <= 6'd21; ad_ser_data <= ad_ser_data << 1'b1; end //10 6'd21 : begin sclk_ad <= 1'b1; din <= SPI_DATA[6]; spi_state <= 6'd22; ad_ser_data <= ad_ser_data + dout; //[3] end 6'd22 : begin sclk_ad <= 1'b0; spi_state <= 6'd23; ad_ser_data <= ad_ser_data << 1'b1; end //11 6'd23 : begin sclk_ad <= 1'b1; din <= SPI_DATA[5]; spi_state <= 6'd24; ad_ser_data <= ad_ser_data + dout; //[2] end 6'd24 : begin sclk_ad <= 1'b0; spi_state <= 6'd25; ad_ser_data <= ad_ser_data << 1'b1; end //12 6'd25 : begin sclk_ad <= 1'b1; din <= SPI_DATA[4]; spi_state <= 6'd26; ad_ser_data <= ad_ser_data + dout;//[1] end 6'd26 : begin sclk_ad <= 1'b0; spi_state <= 6'd27; ad_ser_data <= ad_ser_data << 1'b1; end //13 6'd27 : begin sclk_ad <= 1'b1; din <= SPI_DATA[3]; spi_state <= 6'd28; ad_ser_data <= ad_ser_data + dout;//[0] end 6'd28 : begin sclk_ad <= 1'b0; spi_state <= 6'd29; end //14 6'd29 : begin sclk_ad <= 1'b1; din <= SPI_DATA[2]; spi_state <= 6'd30; end 6'd30 : begin sclk_ad <= 1'b0; spi_state <= 6'd31; end //15 6'd31 : begin sclk_ad <= 1'b1; din <= SPI_DATA[1]; spi_state <= 6'd32; end 6'd32 : begin sclk_ad <= 1'b0; spi_state <= 6'd33; end //16 6'd33 : begin sclk_ad <= 1'b1; din <= SPI_DATA[0]; spi_state <= 6'd34; end 6'd34 : begin sclk_ad <= 1'b0; spi_state <= 1'd1; end default : ; endcase end end //-------------------------------- //Funtion : ad_data //reg [7:0] ad_data; always @(posedge clk or negedge rst_n) begin if(!rst_n) ad_data <= 8'd0; else if(spi_state == 6'd34) ad_data <= ad_ser_data; end endmodule