概述

特性:

(1)数字 I/O 端口

高速 GPIO 功能:

- GPIO 寄存器位于外设 AHB 总线,以实现高速的 I/O 时序;

- 屏蔽寄存器允许将某些端口位作为一组进行操作,而其它位不变;

- 所有 GPIO 寄存器都可以字节、半字和字寻址;

- 整个端口值可用一条指令写入;

- GPIO 寄存器可由 GPDMA 进行访问;

位电平置位和清零寄存器允许单指令置位清零一个端口的任意位;

所有 GPIO 寄存器支持 Cortex-M3 位带操作;

GPIO 寄存器可由 GPDMA 控制器进行访问,允许对 GPIO 进行 DMA 数据操作,使之与 DMA 请求同步;

单个 I/O 口的方向可控制;

所有 I/O 口在复位后默认为上拉输入。

(2)可产生中断的数字端口

PORT0 和 PORT2 端口的每个引脚都可以提供中断功能;

每个端口上的中断可被编程为上升沿、下降沿或边沿产生中断;

边沿检测是异步的,因此可以在没有时钟的情况下(例如掉电模式)操作。使用这种特性,就无需电平触发中断;

每个使能的中断产生一个唤醒信号,将器件从掉电模式中唤醒;

寄存器为软件提供挂起的上升沿中断、挂起的下降沿中断和整个挂起的 GPIO 中断;

GPIO 中断功能不要求将管脚配置为 GPIO 功能,这允许将 GPIO 中断管脚用于操作外设接口。

引脚描述

寄存器描述

数字 I/O 端口

LPC178x/177x 系列 Cortex-M3 具有多达 6 组的 32 位通用 I/O 端口,分别为 P0、P1、P2、P3、P4 和 P5(P5 只引出 P[4:0]),全部为高速 GPIO,其中 P0 和 P2 端口的每个引脚都可以提供中断功能。表 5.2 中寄存器反映了所有 GPIO 的特性。这些寄存器位于 AHB 总线上,以便于

进行高速的读写时序。它们也可作为字节、半字和字长的数据进行访问。屏蔽寄存器允许访问一个 GPIO 端口的一组位,而不影响其它位。

GPIO 或者用于输出控制,或者用于引脚电平状态的读取,LPC178x/177x 系列 Cortex-M3设计了一组寄存器用于 GPIO 的控制,可以很方便的实现 GPIO 的各种应用。

使用 4 个寄存器即可操作一个 GPIO,分别为控制方向的 FIOxDIR、控制输出电平状态的FIOxSET(控制输出高电平) 和 FIOxCLR(控制输出低电平)、以及反映引脚电平状态的 FIOxPIN。

可以设置 GPIO 引脚的模式为上拉、下拉、高阻、开漏或者中继模式

由于 LPC178x/177x 系列 Cortex-M3 具有 6 个端口,所以它们具有 6 组控制寄存器。这些寄存器均为 32 位宽度,每一位都对应着一个不同的 I/O 口。一个 GPIO 引脚在某一时刻,只受四个位的控制,这四个位分布在该 GPIO 引脚所属端口的四个控制寄存器中。

例:P0.2 引脚属于端口 0,那么它受到端口 0 控制寄存器组中 FIO0PIN[2]、FIO0SET[2]、FIO0DIR[2]和 FIO0CLR[2]这四个位的控制

注: GPIO 引脚 P0.29 和 P0.30 与 USB D+/- 管脚共用,并且具有相同的方向。如果位 29 或位 30 在 FIO0DIR寄存器中被配置为零,则 P0.29 和 P0.30 都为输入。如果 FP0DIR 位 29 和位 30 被配置为 1 ,则 P0.29 和 P0.30

都为输出。

GPIO 端口输出置位寄存器 FIOxSET(FIO0SETFIO5SET - 0x2009 80180x2009 80B8)

当引脚在输出模式中被配置为 GPIO 时,该寄存器控制在端口引脚产生高电平输出。向该寄存器的某些位写入“1”时,对应的引脚将输出高电平。写入“0”无效,如果需要引脚输出低电平,不能通过向 FIOSET 写入 0 来实现,而要使用 FIOCLR 来完成。

GPIO 端口输出清零寄存器 FIOxCLR(FIO0CLRFIO5CLR - 0x2009 801C0x200980BC)

当引脚在输出模式中被配置为 GPIO 时,该寄存器在端口引脚产生低电平输出。向某些位写入“1”会使相应的引脚产生低电平,同时清零 FIOxSET 寄存器的相应位。写入“0”无效。

如果引脚被配置为输入或其它功能,那么写 FIOxCLR 对引脚没有影响。

GPIO 端口引脚值寄存器 FIOxPIN(FIO0PINFIO5PIN – 0x2009 80140x2009 80B4)

该寄存器提供了端口引脚的值(配置为 ADC 功能的引脚除外),该寄存器将给出引脚的当前值,而不管引脚是否配置为输入或输出,或作为 GPIO 或可选的数字功能。无论该引脚配置成何种功能,都可以从相应的 FIOxPIN 寄存器中读出其当前的逻辑状态。

如果引脚配置为模拟功能(如 ADC 输入),在这种情况下,从 FIOxPIN 寄存器中读出的引脚值无效。

写 FIOxPIN 寄存器时,FIOPIN 寄存器的值会保存到输出寄存器中,而输出寄存器控制着引脚的输出电平状态,即,通过修改 FIOPIN 寄存器可以改变引脚的电平输出状态。由于这种特性影响整个端口,因此在应用中使用时要小心注意。

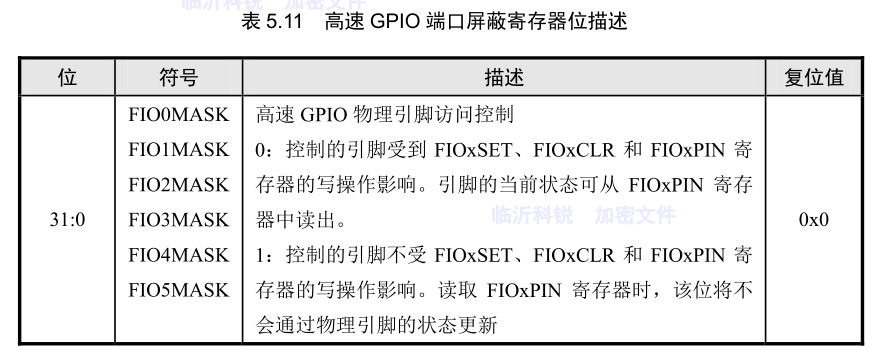

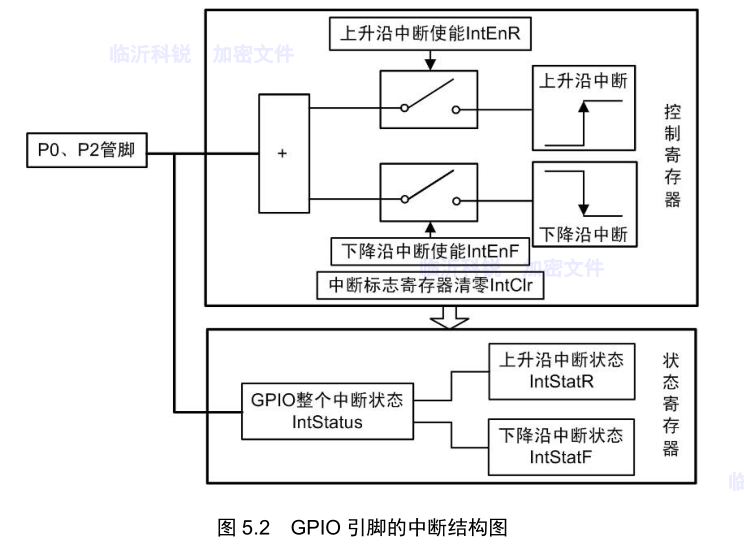

高速 GPIO 端口屏蔽寄存器 FIOxMASK(FIO0MASKFIO5MASK – 0x2009

80100x2009 80B0)

该寄存器用来屏蔽某些端口引脚,被屏蔽的引脚将无法通过 FIOxPIN、FIOxSET 或FIOxCLR 寄存器访问。

向屏蔽寄存器中的某些位写入“1”时,屏蔽对应的引脚,此时不能通过 FIOPIN、FIOSET和 FIOCLR 寄存器操作该引脚;

写入“0”时,对应引脚正常,未被屏蔽,此时可以通过 FIOPIN、FIOSET 和 FIOCLR寄存器操作该引脚。

通过读或写访问,该寄存器中为“0”的位使能相应物理引脚的访问。如果该寄存器中的位

为“1”,则相应位将不会通过写访问改变,并且读操作时将不会在 FIOxPIN 寄存器中反映出来。

GPIO 中断寄存器

LPC178x/177x 系列 Cortex-M3 的 GPIO 引脚还具有一个功能—中断。端口 PORT0 和 PORT2的每一个引脚都可以配置为上升沿中断或者下降沿中断,也可以设置为边沿产生中断。端口PORT0 和 PORT2 的中断通道相同,都是通道 54。端口 PORT0 和 PORT2 的中断功能可以唤醒处于掉电模式下的 CPU。

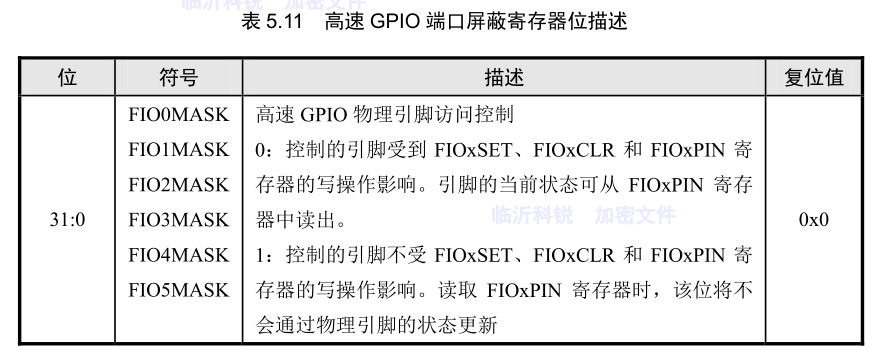

GPIO 引脚的中断寄存器可以分为两组:控制寄存器和状态寄存器。其中控制寄存器决定引脚中断的触发方式,状态寄存器则反映 I/O 中断的当前状态。图 5.2 所示为 I/O 中断的内部结构,表 5.13 所列为 GPIO 的中断寄存器汇总。

GPIO 使用注意事项

1. 连续访问 FIOSET 和 FIOCLR 影响相同的 GPIO 引脚/位

配置为输出的 GPIO 引脚的状态通过写引脚的 FIOSET 和 FIOCLR 寄存器决定。对FIOSET/FIOCLR 寄存器的最后访问将决定引脚的最终输出,如程序清单 5.1 所示。

2. 写 FIOSET/FIOCLR & FIOPIN

方法1,标准切换引脚输出状态,存在切换延迟

从一组 I/O 口线上输出变量 Data 中保存的值需完成四步工作,首先

是设置引脚连接模块和引脚方向。输出数据时先清零所有输出 I/O 口线,再把 Data 变量的值写入到 FIOxSET 寄存器中,那么该变量中为 1 的位将在相应的 I/O 口线上反映出来,而变量中为0 的位将不影响相应引脚的输出电平状态,仍然保持低电平。

方法2,直接切换引脚输出状态

写 FIOPIN 寄存器是直接对相应端口的所有 GPIO 引脚生效的,也就是说写入值中为 1 的位所对应的 GPIO 引脚将输出高电平,为 0 的位所对应的 GPIO 引脚将输出低电平。高低电平的输出是同时发生的

3. GPIO 端口上 0 和 1 的瞬时输出

先写 FIOSET 再写 FIOCLR 寄存器可使引脚先输出 1 再输出 0。

某些应用要求一个 GPIO 口的一组引脚同时输出一个二进制数(0 和 1 混合),这可通过写端口的 FIOPIN 寄存器来实现

4. I 2 C 接口引脚

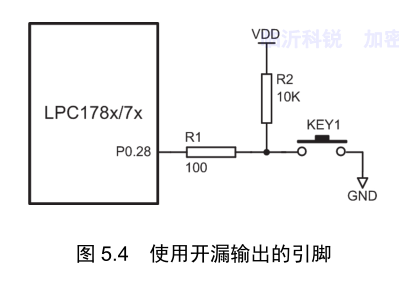

LPC178x/177x 系列 Cortex-M3 大部分的 I/O 引脚为推挽方式输出,但是具有 I 2 C 总线功能的 I/O 引脚为开漏输出(P0.27、P0.28 和 P5.2、P5.3)。使用这些开漏输出的引脚作为 GPIO 功能,并用于高电平输出或者引脚状态输入时,要接上拉电阻才能正常使用。

5. GPIO 引脚驱动能力

推挽输出的 I/O 引脚正常拉出/灌入电流均为 4mA,短时间极限值为 40mA。

6. P0.29、P0.30

P0.29 与 P0.30 在作为 GPIO 使用时,只能同时设置为输入模式或者同时设置为输出模式,不能设置为不同的模式。例如,只有 FIO0DIR[29] = FIO0DIR[30] = “1”时,P0.29 和 P0.30才是输出模式,否则全是输入模式。即,只要 FIO0DIR[29]和 FIO0DIR[30]中任意一位为 0,则P0.29 和 P0.30 便是输入模式。