最近完善了下USB3.0的视频开发测试,主要优化了FPGA程序和固件,及其同步方式。对带宽和图像效果进行了仔细的测试

开发板架构(2CMOS+FPGA+2DDR2+USB3.0)

评估板底板配合2个MT9M001摄像头安装效果

准备工作

1、下载安装isensor app kit 软件 链接:http://pan.baidu.com/s/1pKodddL 密码:248s

2、更新usb固件程序 通过官方软件

3、下载fpga程序

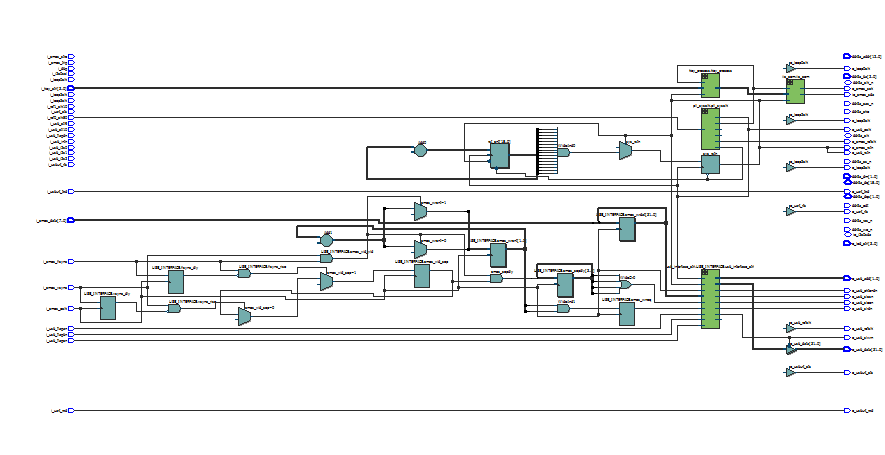

fpga顶层结构

顶层代码

module fpga_usb_slfifo_top(

input wire i_ref0_clk50 , // T1, 50MHz

input wire i_ref1_clk10 , // L22, 10MHz, from mother board OCXO

output wire o_loop0clk , // H2

//output wire o_loop1clk , //

output wire o_loop2clk , // H21

output wire o_loop3clk , // C10

input wire i_loop0clk , // G2

//input wire i_loop1clk , //

input wire i_loop2clk , // G21

input wire i_loop3clk , // B11

output wire [3:0] o_led_ctrl , // ctrl0 = G8,H7,J7,J6

input wire [3:0] i_key_ctrl , // ctrl0 = N22,N21,M21,M22

// UART FPGA --> RX232

output wire o_uart_rts , // G16

input wire i_uart_cts , // F16

input wire i_uart_rxd , // C17

output wire o_uart_txd , // D17

// UART USB --> FPGA

input wire i_usburt_rts , // B6

output wire o_usburt_cts , // D6

output wire o_usburt_rxd , // A6

input wire i_usburt_txd , // F7

// I2C USB --> FPGA

input wire i_i2c0scl , // B5

inout wire io_i2c0sda , // A5

///////////////////////////////////////////////////////////

// mother board ctrl

/*

output wire o_ref1_clk10 , // M2

output wire o_ref0_clk5 , // C4

// ADC common

output wire o_adc_dith , // J17

output wire o_adc_shdn , // K21

output wire o_adc_rand , // L21

// ADC input

output wire o_adc0_rfgc , // J4

input wire i_adc0_pclk , // H6

input wire i_adc0_ovrf , // G4

input wire [15:0] i_adc0_data , // data0 = B1,B2,C1,C2,F2,E1,H1,F1

// data8 = H5,E6,C6,D2,E5,E3,E4,G3

output wire o_adc1_rfgc , // J3

input wire i_adc1_pclk , // AA1

input wire i_adc1_ovrf , // J2

input wire [15:0] i_adc1_data , // data0 = U2,U1,V1,V2,W2,W1,Y2,Y1

// data8 = AA2,N2,N1,P2,P1,L8,K8,J1

// AD9518(PLL) ctrl

output wire o_pll_resetn , // A4

output wire o_pll_pdn , // B4, power down

output wire o_pll_csn , // C3

output wire o_pll_sclk , // A3

output wire o_pll_sdout , // B3

*/

output wire o_cmos_sck , // AA2

output wire io_cmos_sda , // AA1

output wire o_cmos_rstn , // M2

input wire i_cmos_trig , // J2

input wire i_cmos_stro , // J1

output wire o_cmos_refclk , // W2

input wire i_cmos_pclk , // W1

input wire i_cmos_hsync , // Y2

input wire i_cmos_vsync , // Y1

input wire [7:0] i_cmos_data , // data0 = N2,N1,P2,P1,U2,U1,V1,V2

///////////////////////////////////////////////////////////

// USB signals

output wire o_usb_refclk , // B16, output 19.2MHz for USB3014

output wire o_usb_rstn , // A15

input wire i_usb_intn , // A18

output wire o_usb_pclk , // H11

output wire [31:0] o_usb_data , // data0 = A20,F15,D19,E15,G14,G15,C15,B14

// data8 = D15,E16,B19,B18,A19,A14,B15,H15

// data16 = A17,E11,B10,A10,G13,B9 ,G10,F11

// data24 = E10,H10,F10,G9 ,F9 ,B8 ,E7 ,C8

output wire [1:0] o_usb_add , // add0 = C13,G11. same as CTL12, CTL11

output wire o_usb_slcsn , // A16, same as CTL0

output wire o_usb_slwrn , // B17, same as CTL1

output wire o_usb_sloen , // E14, same as CTL2

output wire o_usb_slrdn , // D13, same as CTL3

output wire o_usb_pktendn , // F14, same as CTL7

input wire i_usb_flagan , // C19, same as CTL4

input wire i_usb_flagbn , // C7 , same as CTL5

input wire i_usb_flagcn , // F13, same as CTL6

input wire i_usb_flagdn , // D10, same as CTL8

input wire i_usb_ctl9 , // B13, CTL9

input wire i_usb_ctl10 , // E12, CTL10

input wire i_usb_i2s0 , // A8

input wire i_usb_i2s1 , // B7

input wire i_usb_i2s2 , // A7

//ddr2-0

output wire[12: 0] ddr2a_addr , //A0-7 :N16,AA4,T16,AA3,R15,T8,T11,Y6

//A8-13:U14,T9,AB3,T10,V6

output wire[ 2: 0] ddr2a_ba , //B0 :U13,AB10,V7

output wire ddr2a_cas_n , //T12

output wire ddr2a_cke , //AB5

inout wire ddr2a_clk , //U7

inout wire ddr2a_clk_n , //U8

output wire ddr2a_cs_n , //P15

output wire[ 1: 0] ddr2a_dm , //dm0-3 :V5,AA7

inout wire[15: 0] ddr2a_dq , //q0-7 :W8,Y3,W7,Y7,W6,U9,AA5,V8

//q8-15 :W10,AB8,AA9,Y8,AA8,V11,AB7,U10

inout wire[ 1: 0] ddr2a_dqs , //dqs0-3:V10,AB9

output wire ddr2a_odt , //P16

output wire ddr2a_ras_n , //R14

output wire ddr2a_we_n , //Y10

/*

//ddr2-1

output wire[12: 0] ddr2b_addr , //A0-7 :W22,U20,W21,R16,V22,AA21,V21,U15,U22

//A8-13:AA22,P17,R22,T14

output wire[ 2: 0] ddr2b_ba , //B0 :W20,R20,Y17

output wire ddr2b_cas_n , //Y21

output wire ddr2b_cke , //U19

inout wire ddr2b_clk , //AA17

inout wire ddr2b_clk_n , //AB17

output wire ddr2b_cs_n , //R21

output wire[ 1: 0] ddr2b_dm , //dm0-3 :AA16,AA10

inout wire[15: 0] ddr2b_dq , //q0-7 :W17,W15,V15,AB16,V14,AB20,T15,AB18

//q8-15 :AA14,U12,AB14,W13,AB13,AB15,AA13,AA15

inout wire[ 1: 0] ddr2b_dqs , //dqs0-3:V13,Y13

output wire ddr2b_odt , //Y22

output wire ddr2b_ras_n , //U21

output wire ddr2b_we_n //R19

*/

input wire i_dbg

);

测试效果及其带宽计算

单MT9M001 48M xclk输入,全像素输出130万像素(1280*1024) 帧率为30fps,带宽39Mbyte per sec

单MT9P031 80M xclk输入,全像素输出500万像素(2592*1944) 帧率为12fps,带宽60Mbyte per sec

单MT9P031 96M xclk输入,全像素输出500万像素(2592*1944) 帧率为14fps,带宽70Mbyte per sec

极限测试(FPGA控制 80M时钟,32bit总线模拟视频输出演示)

使用模拟1080p视频(1920*1080) 每帧图像2.1Mbyte 帧率 150fps

带宽合计 300M byte per sec 无数据丢失

模拟1080p灰度图像,逐步渐变过程

联合博客技术交流(您可以通过以下方式了解,关注我们的博客和交流)

http://blog.chinaaet.com/shenyae86

http://www.openedv.com/posts/list/58978.htm

http://www.cnblogs.com/ccjt/

http://blog.sina.com.cn/u/5625282126

http://xinanhejishu.blog.163.com/

QQ交流群:层层惊涛 26210916

辐射防护交流群 224673609

百度云盘资料下载

http://yun.baidu.com/s/1kThKzaf

http://yun.baidu.com/s/1c0SKEC4

http://yun.baidu.com/s/1mgVml3i