最近使用Vivado仿真, 有点慢, 听说Modelsim仿真会快一些,这就试试!

经过测试,同样的仿真长度,Vivado内置xsim用了36min,Modelsim用了约13min.

原文地址 https://www.cnblogs.com/hqz68/p/10491509.html

工具地址 https://www.cnblogs.com/charleechan/protected/p/12983756.html

我用的是目前最新版本的软件,vivado2018.3与modelsim10.6d。废话不多说,直接上操作

1.modelsim编译vivado库

1)双击启动vivado软件,如下图操作

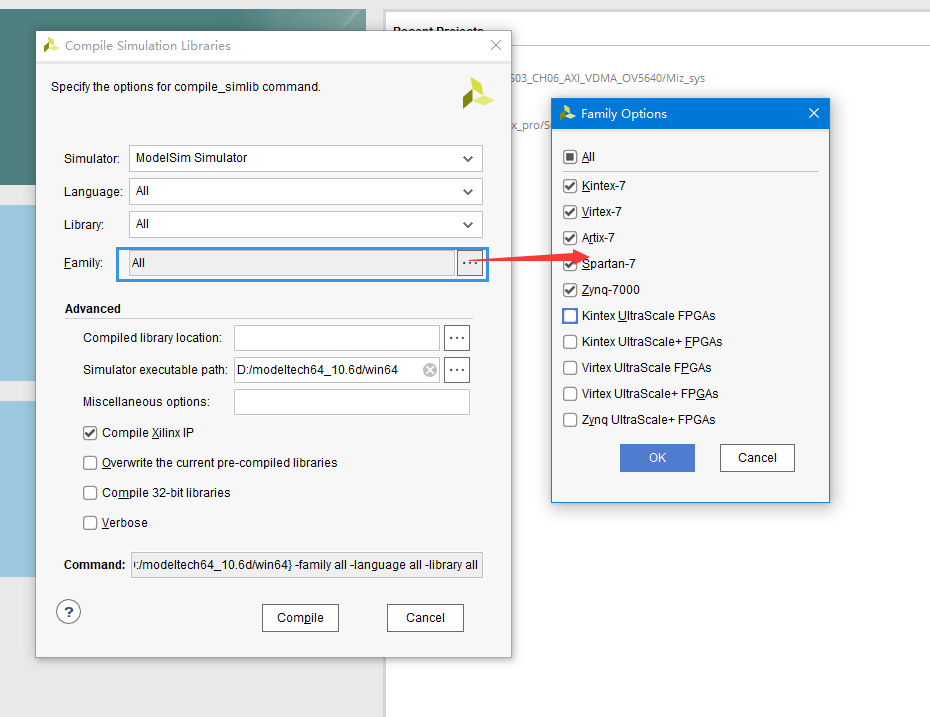

2)Simulator:选对应的、

Language:都选all,

Verilog与vhdl都用可能用到,

Library:unisim 功能仿真,simprim 时序仿真,选择all,

Famliy:如下图看你用那些,全勾选的话编译时间会很长而且会很大,所以按需要勾选

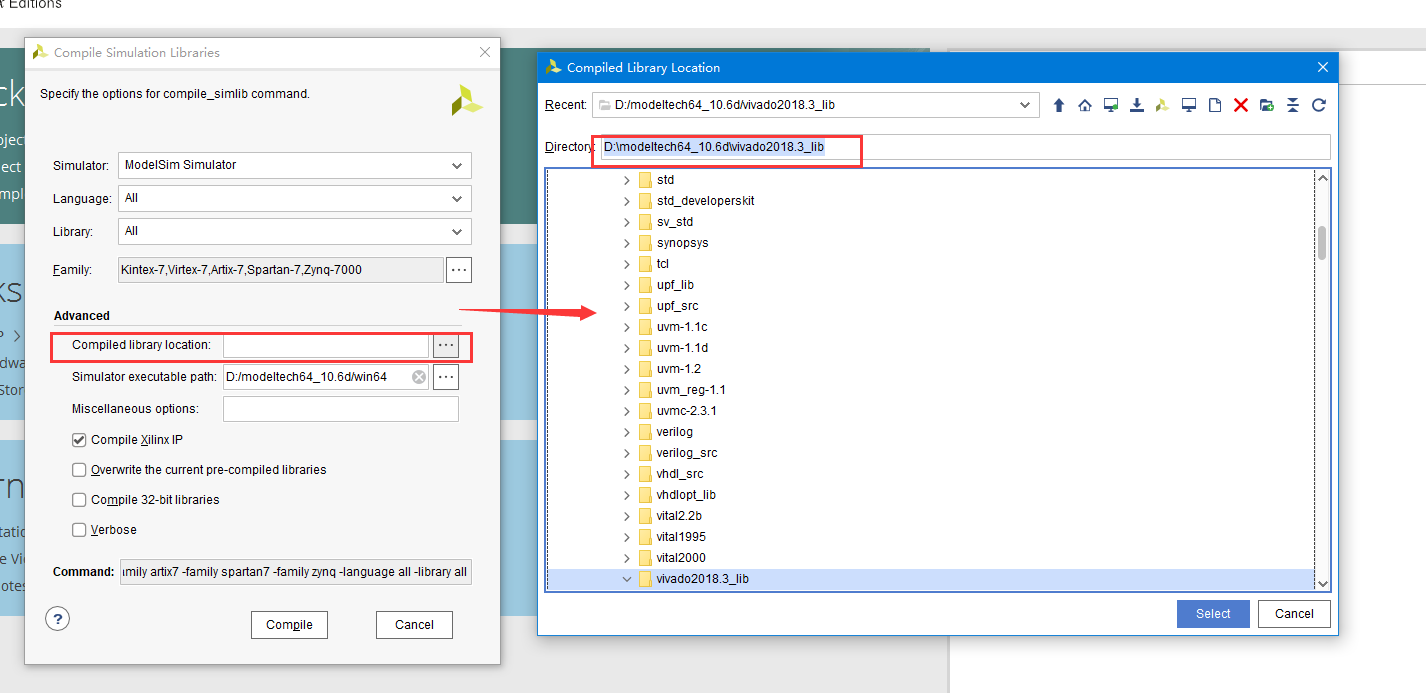

3)编译库存放位置,一般都是放置到modelsim目录下面,需要自己新建文件夹并命名,如图所示

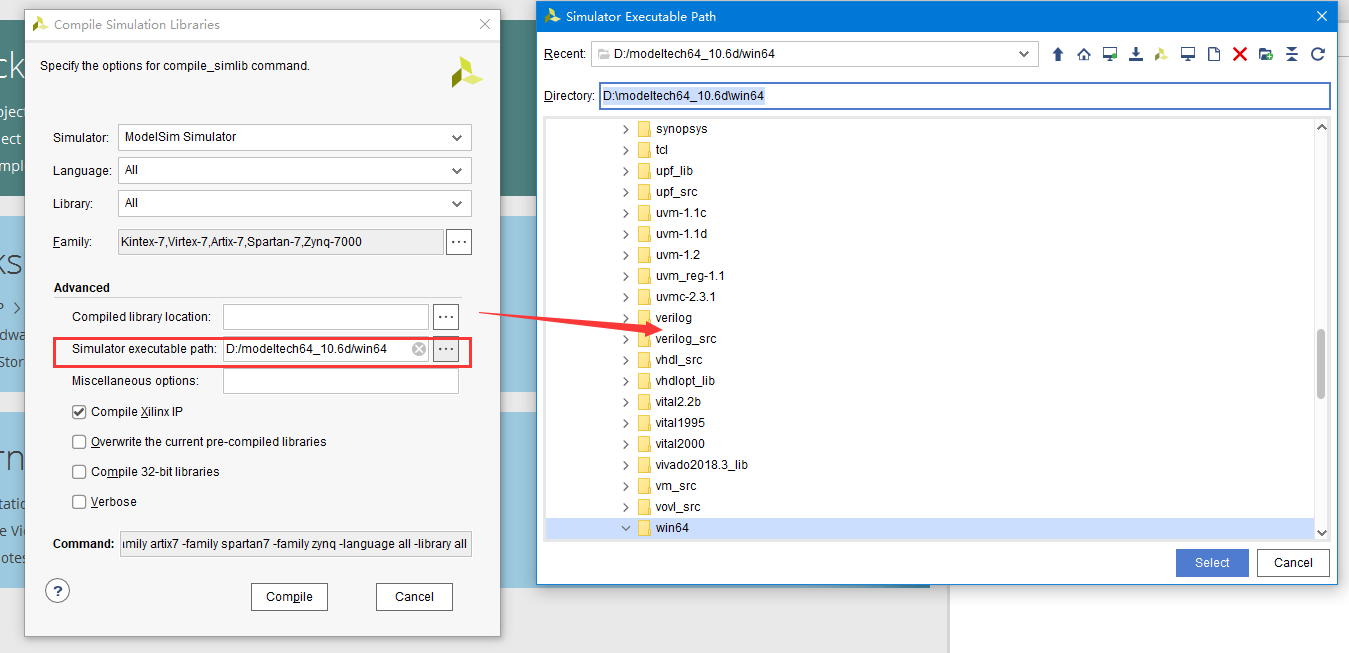

4)编译器路径,vivado会自动识别出路径,没有的话自己手动添加,选到win64文件夹就行了

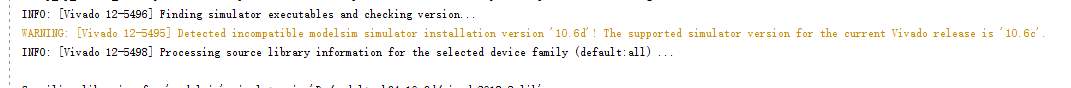

5)配置完成,点击Complie就进行编译后面有下图警告,可以不用在意,这警告的意思是vivado2018.3适合modelsim10.6c版本,要求不高可以忽略

**我只选择了Artix-7,用了28分钟(i7-6700HQ).**

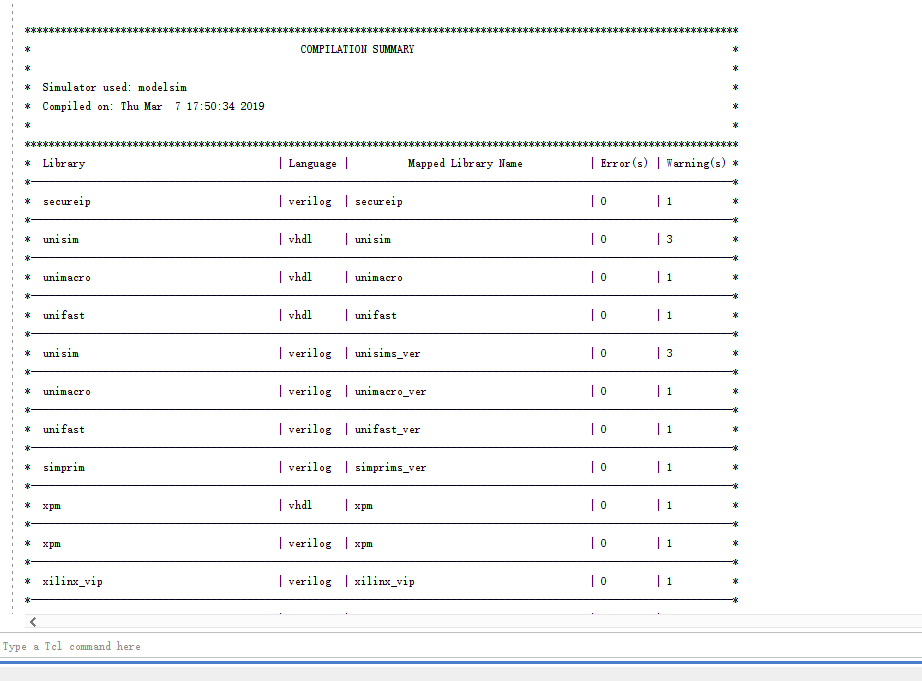

最后出现下图信息列表,没有错误最好,警告可以忽略

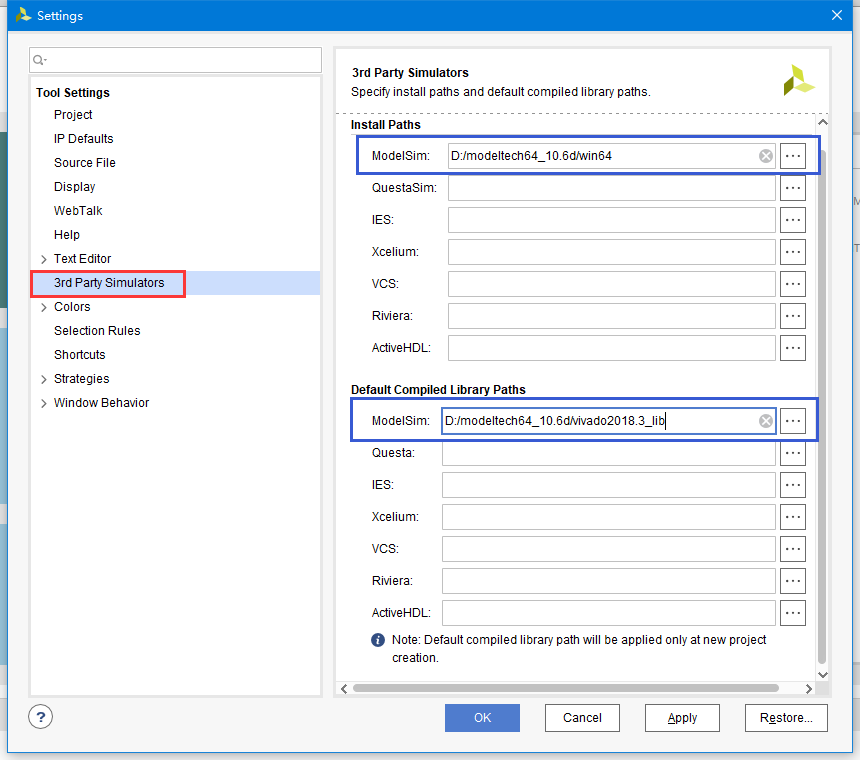

2.制定modelsim安装路径和编译库

启动vivado 进入Tools —> setting,按下图操作,对应你用的仿真器,最后点击Apply,OK退出

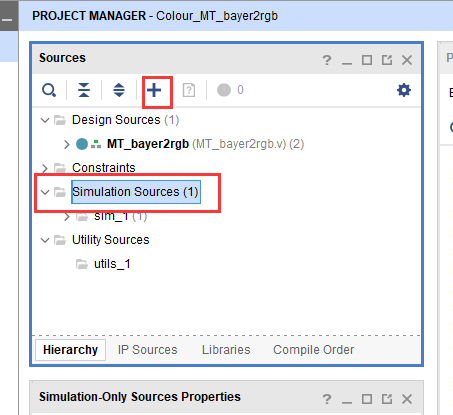

3.仿真需要添加仿真激励文件,和添加工程源文件一样,可以添加现有的激励,也可以新建

1)如图操作,选中simulation再点+号。

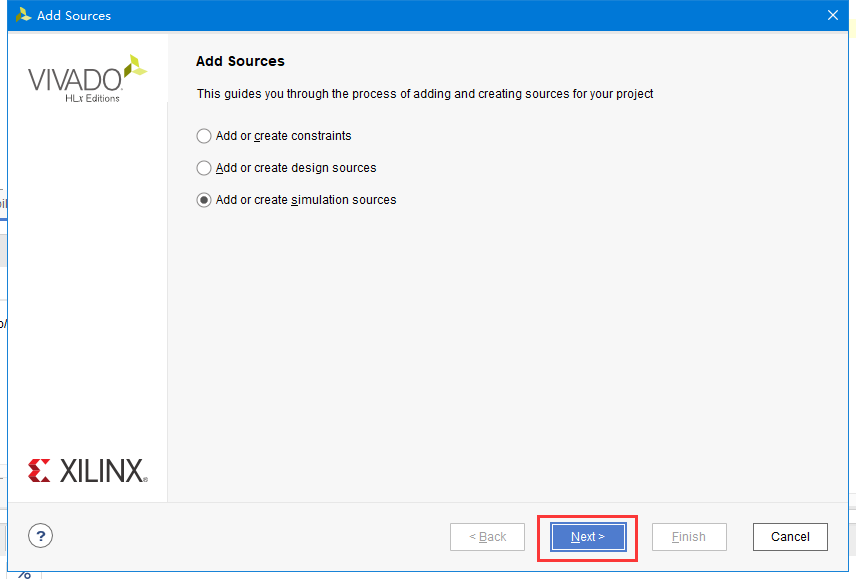

2)点击next

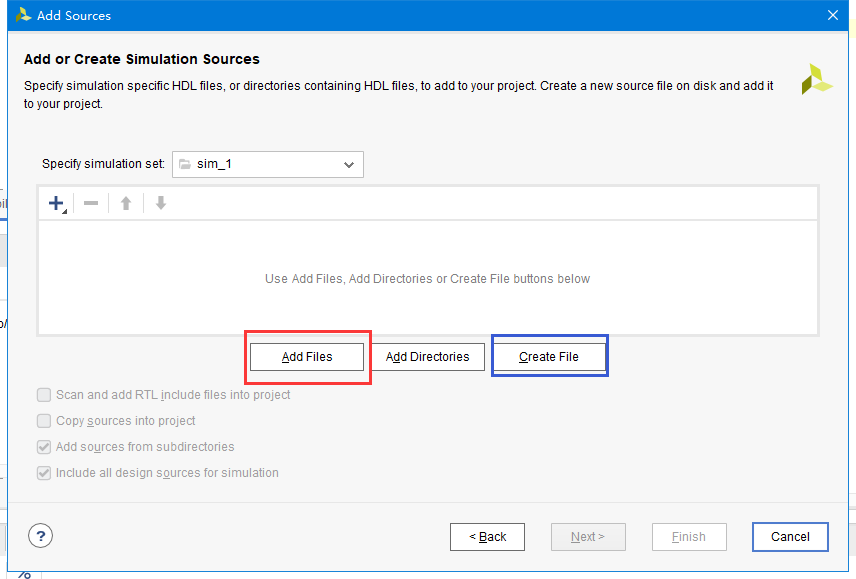

3)红框是添加已有的激励文件,蓝框是新建新的激励文件。

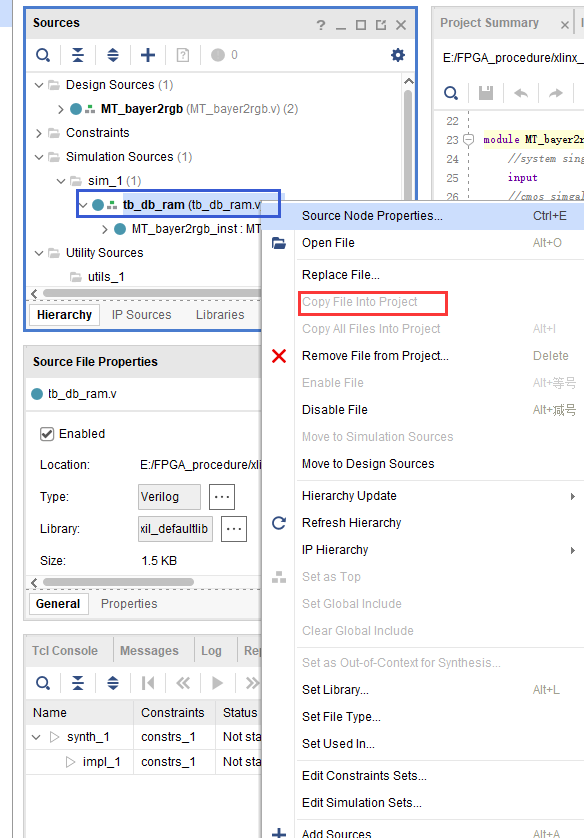

4)如果我们是添加现有的激励文件,vivado不会将文件添加到工程目录中,文件还在其他之前路径下,这样的很容易丢失。vivado可以手动将文件拷贝到工程目录下,如图所示,蓝框是我添加的激励文件,选中右键选择红框的copy file into project 。我添加完了,所以显示灰色。

4.对已有工程仿真前进行设置修改

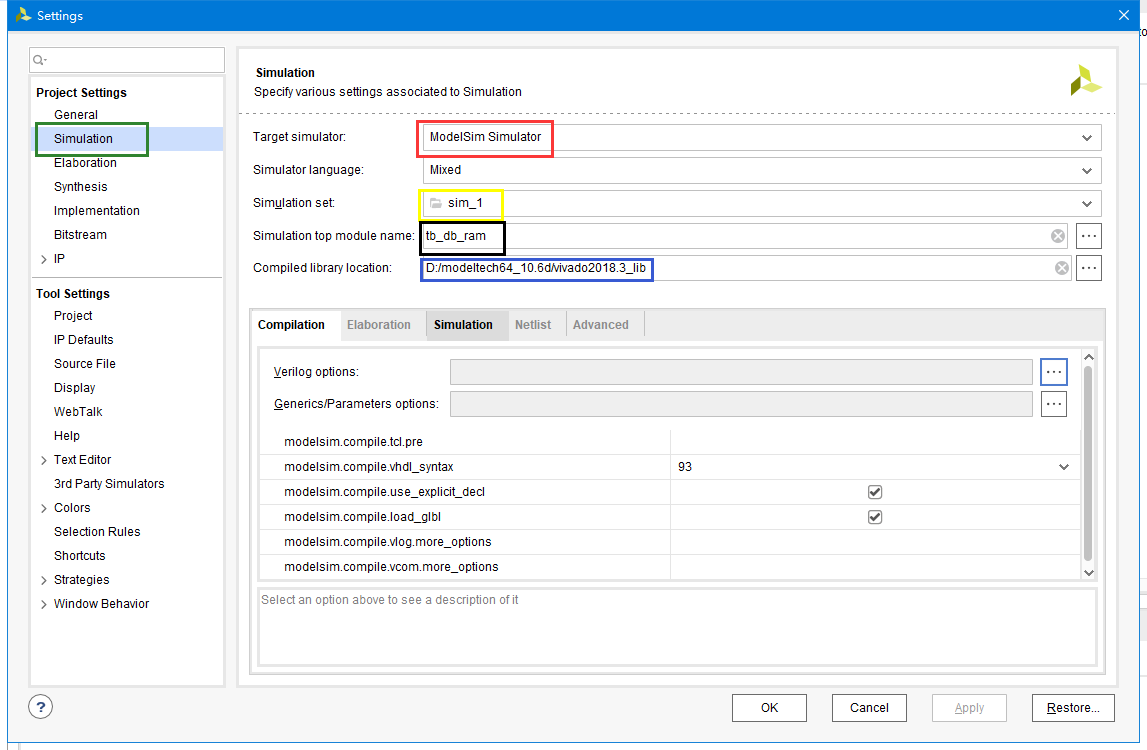

1)Tools -> Setting -> Simulation,进入绿框选项,进行仿真设置。红框选择仿真器,选用modelsim。黄框是仿真工程文件夹名,可以自己定义。黑框是激励文件。蓝框是之前编译的vivado库路径。

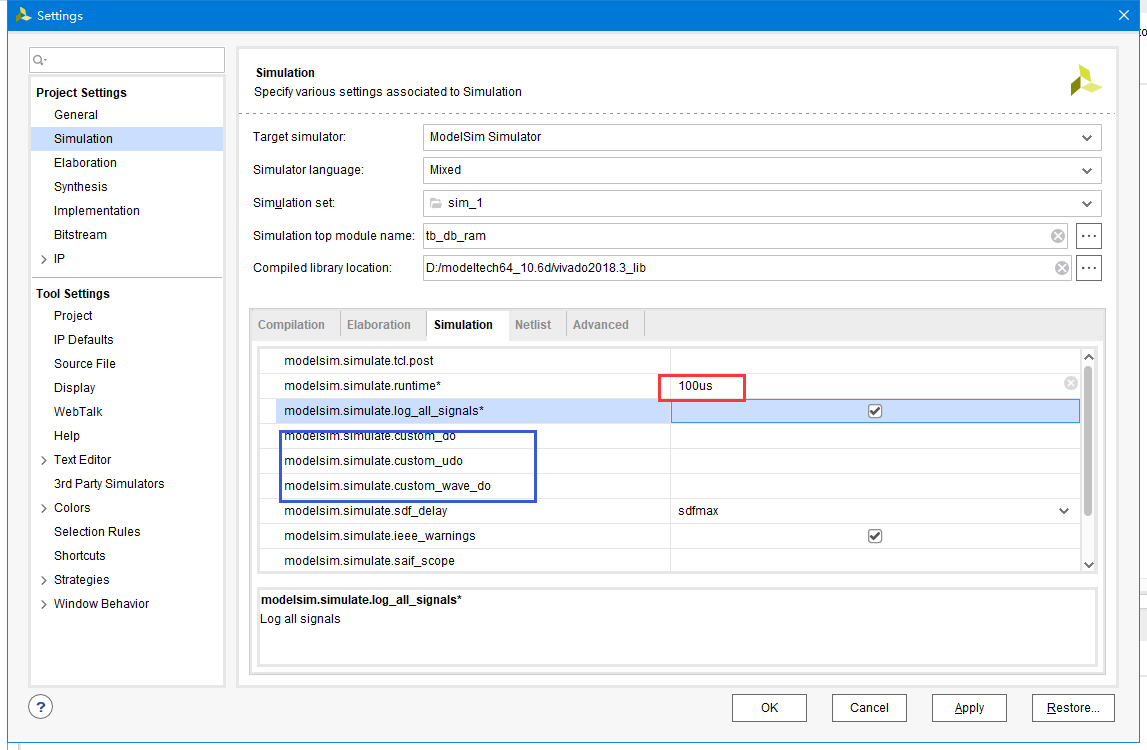

2)进行自定义仿真设置,可以修改仿真时间,勾选仿真所有信号。点击Apply、OK就可以启动仿真了。

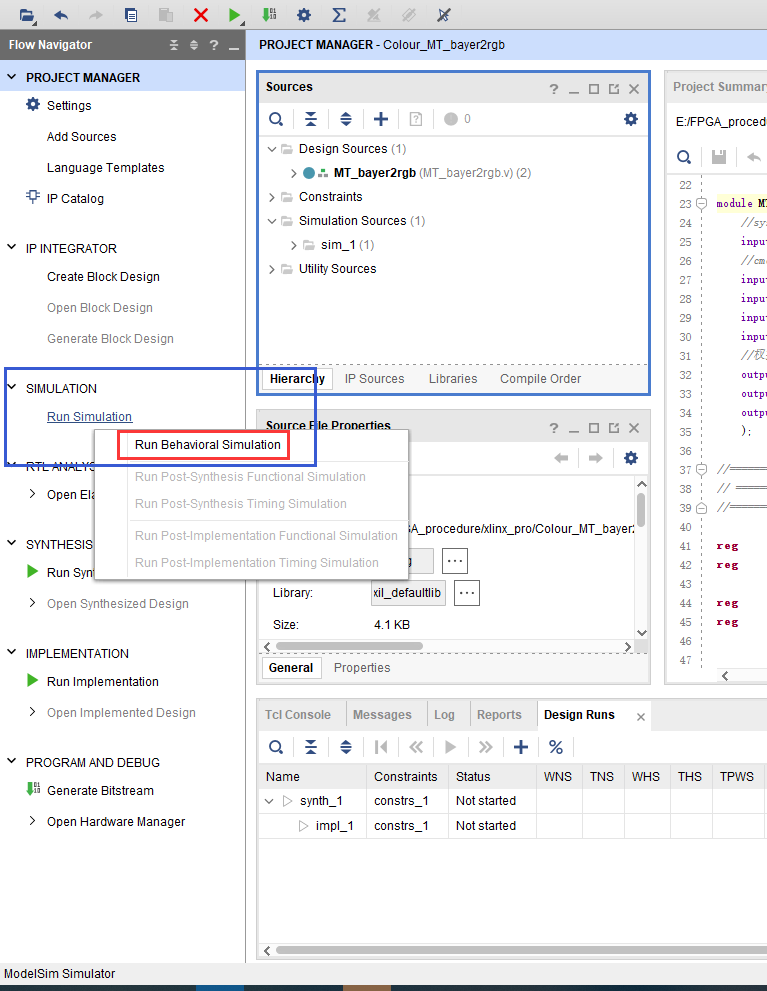

3)启动仿真,可以直接进行行为仿真,其他显示灰色需要编译综合就可以选择

- ModelSim 仿真结果的保存与加载

- 在wave界面,将仿真波形保存为 .do文件(添加信号到波形图窗口的命令)。或者按快捷键Ctrl+S保存波形图窗口;

- 切换左边导航窗口的“sim”,,点击保存,给将要保存的 .wlf文件(仿真数据文件)命名为自己想要的名字,默认为vsim.wlf。(wlf文件为modelsim的wave log file文件格式)

或者在菜单栏File->Dataset-> SaveAs.

- 保存,OK,关闭modelsim(注意,必须关闭modelsim,否则打开wlf文件的时候,会提示未正常关闭,无法打开)。

- 重启modelsim,open 之前保存的 .wlf文件,然后 load 对应的 .do文件,将添加信号列表到波形图窗口。

也可以使用命令行的格式打开此波形文件,举例如下:vsim -view wave.wlf -do run.do。