目的:

自定义一个IP核,通过AXI总线与ARM系统连接

环境:

Win7 32bit

Vivado2014.4.1

Xilinx sdk2014.4

开发板:

Zc702

第一步:

新建一个自定义的HDL模块,本实验新建一个16位加法器,保存为test.v,代码如下

module test(

input [15:0] a,

input [15:0] b,

input clk,

output reg [15:0] sum

);

always@(posedge clk)

begin

sum <= a +b ;

end

endmodule

第二步:

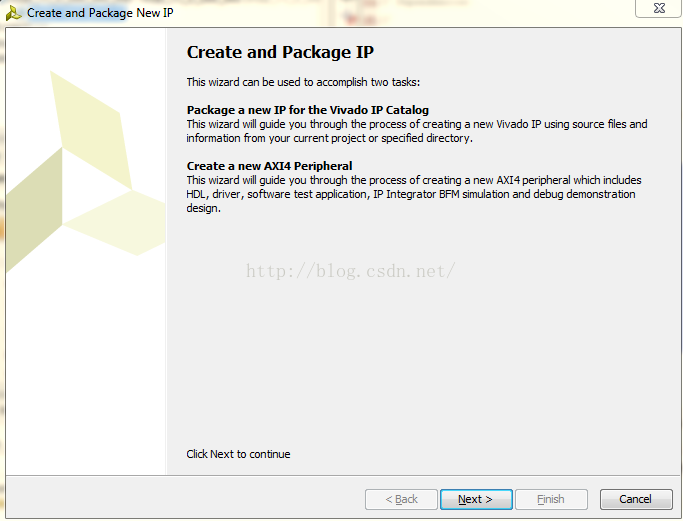

新建一个IP核,打开vivado,在tools中选中新建IP核

点击Next,

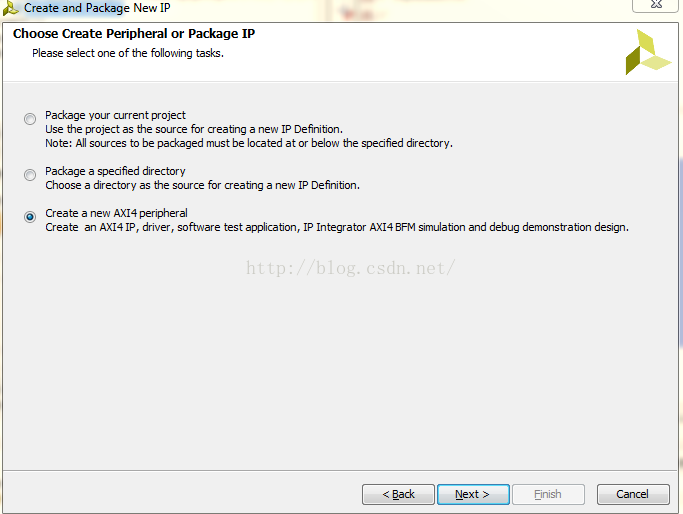

选中新建AXI外设选项,

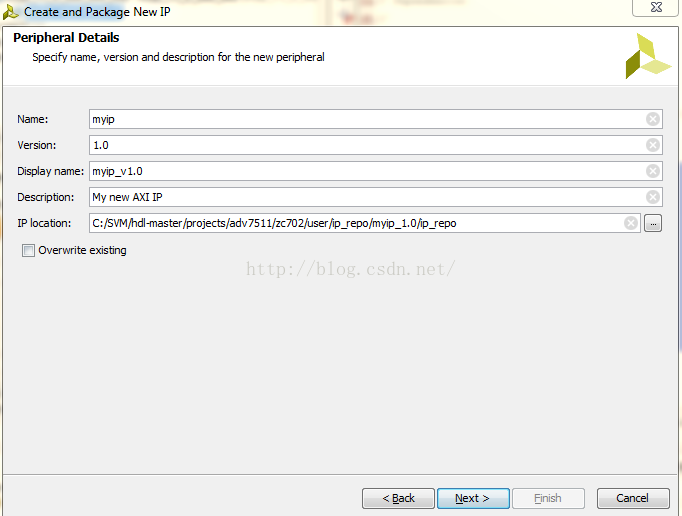

填好信息,点击next,

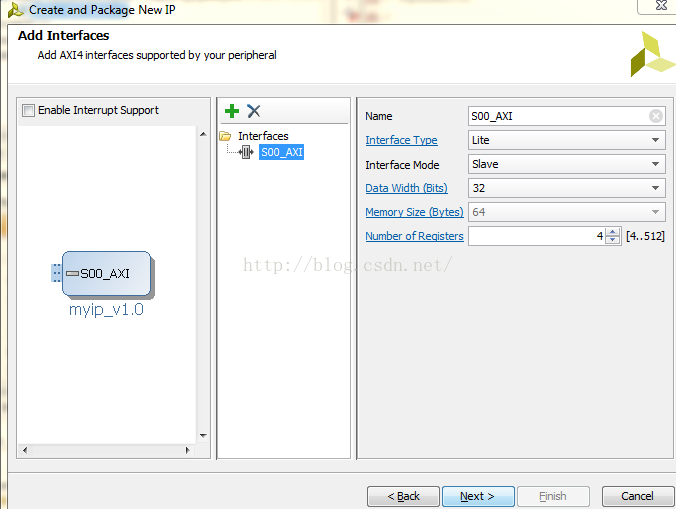

填好参数,这里就用默认的即可,

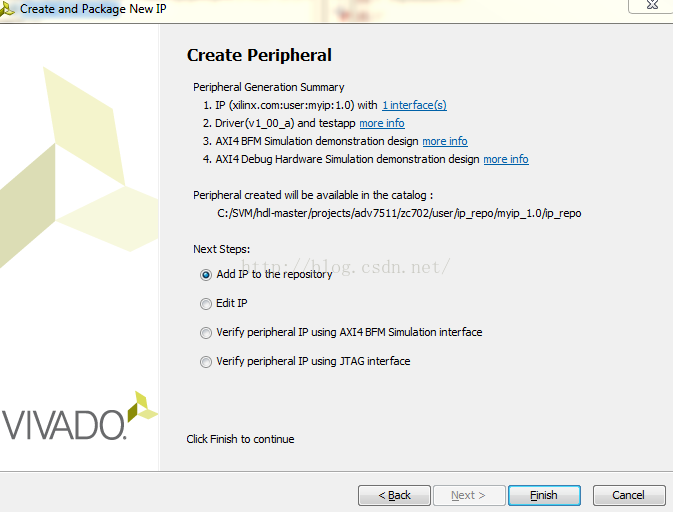

然后点击finish。

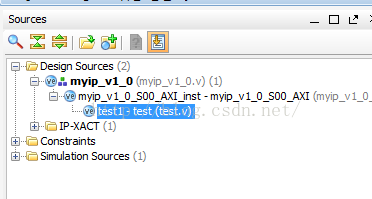

之后会打开一个这个新建的IP核工程,查看

新建的时候是没有test.v加入到工程的,双击myip_v1_0_AXI_inst-myip_v1_0_S00_AXI.v

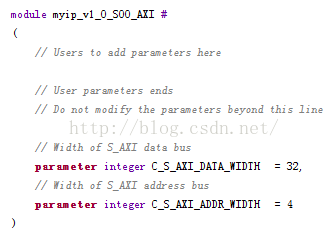

上面这段代码,主要就是定义了使用的参数,也是我们在新建IP核预先设置的参数,数据宽32位,地址宽4位;

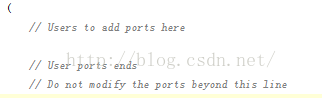

在参数设置之后,这段注释就是让用户可以添加需要的端口了,在本次实验中是不需要添加的;

看接下来的程序:

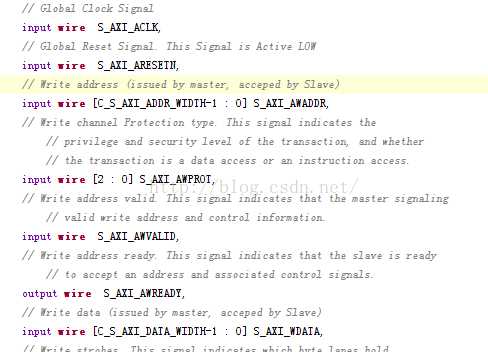

系统默认的第一个输入端口S_AXI_ACLK为时钟,然后S_AXI_ARESETN是复位;

接下来S_AXI_AWADDR是写地址,后面暂略,

从注释就可以看到是安全级别的选项,这个是AXI的标准后续再谈;

还有一个端口S_AXI_WDATA就是写入的数据;

部分端口这里就不说明了,可以直接看注释,直接看马上用到的几个端口:

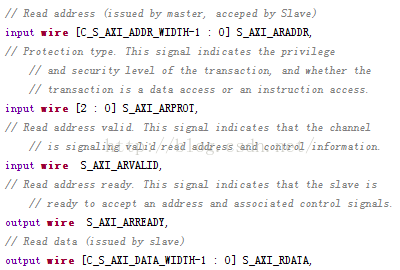

S_AXI_ARADDR是读IP核的地址,S_AXI_RDATA是被读的寄存器;

接下来看

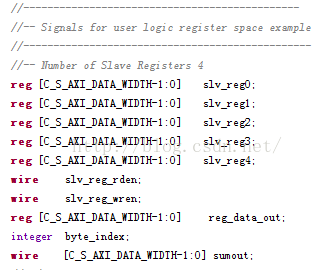

新建的时候会看到4个slv_reg寄存器,实验中又添加了一个

reg [C_S_AXI_DATA_WIDTH-1:0] slv_reg4;

又添加了一条:

wire [C_S_AXI_DATA_WIDTH-1:0] sumout;

主要是为了把test.v这个模块添加进来;

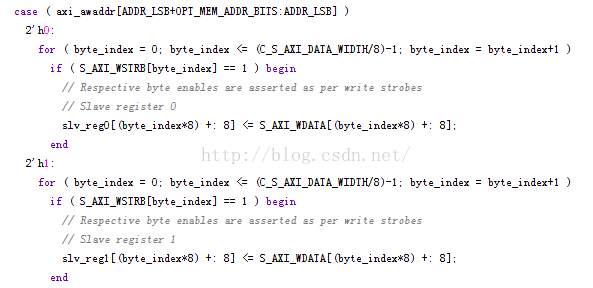

这几个寄存器在

这几条代码显示,在往自定义的IP核内写数据是会将数据写到刚才定义的几个寄存器内的,当然这些寄存器用户都是可以自己改的,这个实验就不更改了;

那么,用户是往哪一个地址写数据呢?那么看这里:

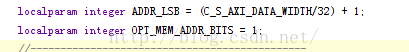

根据上面的定义,

ADDR_LSB=2,OPT_MEM_ADDR_BITS =1;

也就是往地址段axi_awaddr[3:2]部分写的话就会将数据写入这4个寄存器,同理在读数据的时候也是,具体看代码即可。

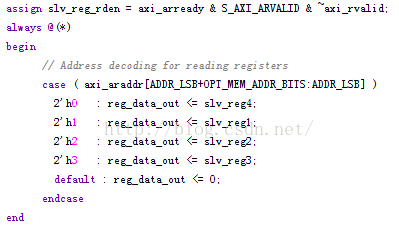

前面看到是用户写数据及其IP核接收到的数据寄存器,下面是IP核的输出数据,也就是用户在读IP核时被读的寄存器:

这里在实验中,做了一些更改,将slv_reg0,变为了slv_reg4;

最后在用户逻辑部分,添加例化的模块。

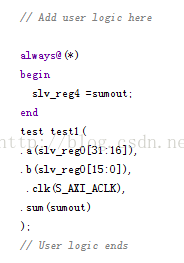

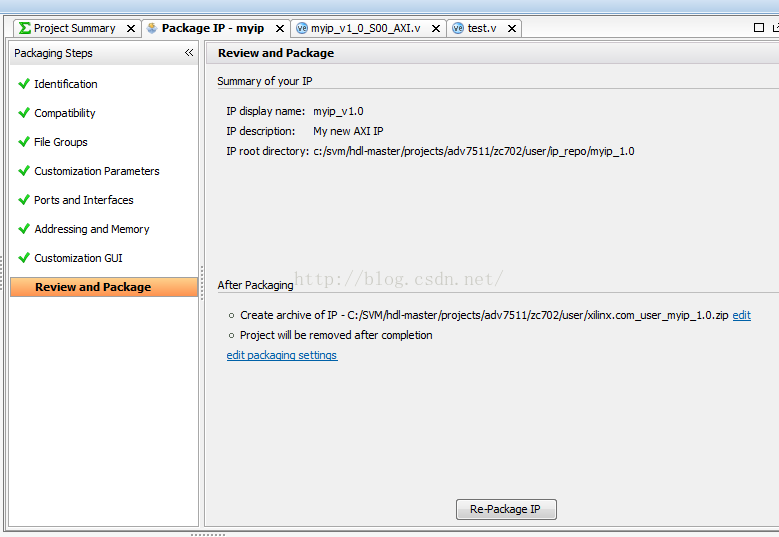

然后

到这界面之后,查看左侧的检查选项是否都已经打勾,没打勾的话选中哪一个选项做一些简单确认即可完成,最后打包IP核,保存为zip的格式。

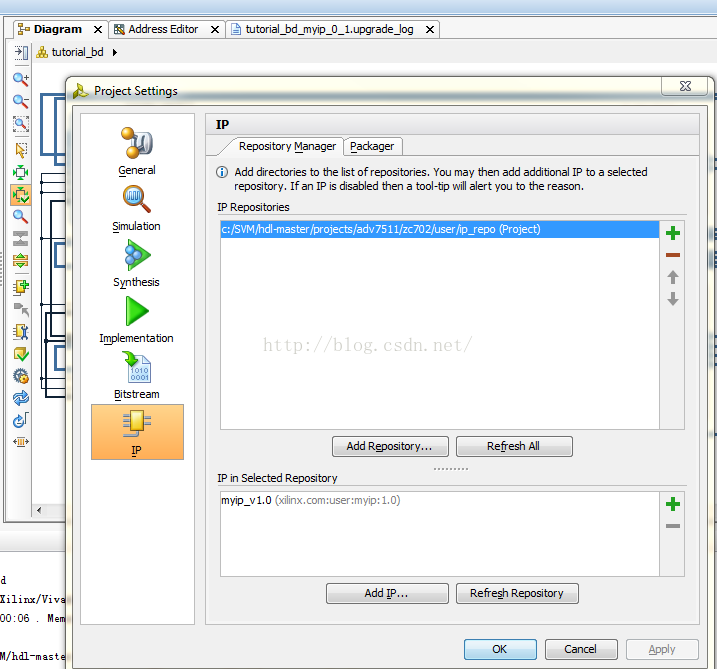

将IP核工程关闭,新建一个系统文件或者打开一个example工程,在工程内添加新建的ip核,当然需要将新建的ip核包含在工程内,如图:

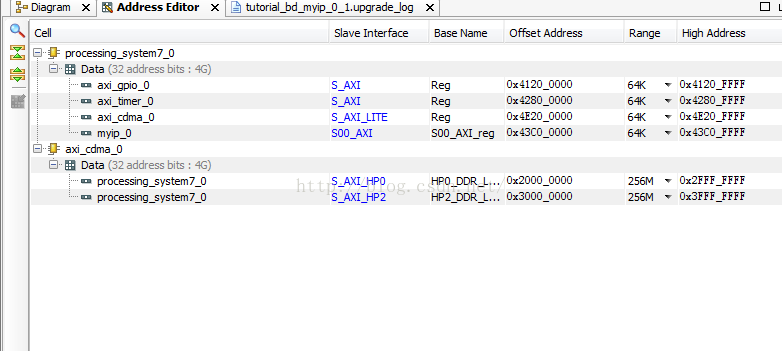

在工程内添加自己的IP之后,自动分配一下地址:

然后确认无误,,生成bitstream。

稍等片刻之后,没有报错,然后export hardware,之后再launch SDk,

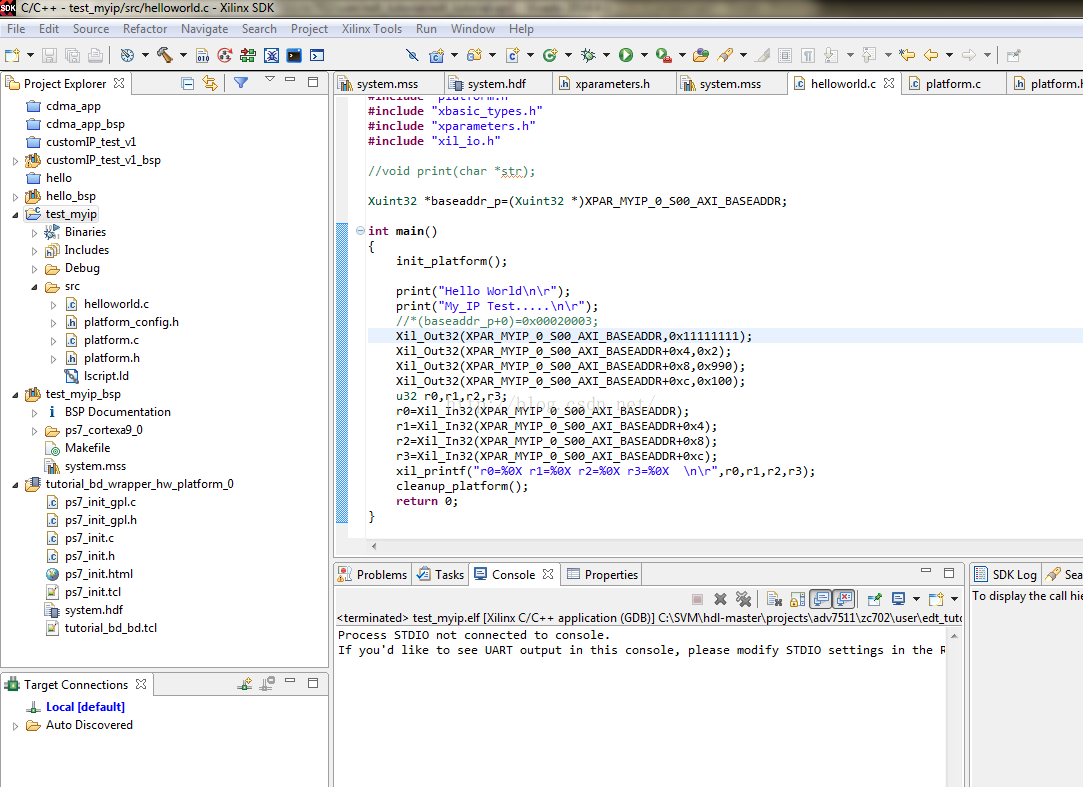

打开SDK后,需要新建一个application,

用最简单的helloworld工程样板即可,然后修改代码:

#include <stdio.h>

#include "platform.h"

#include "xbasic_types.h"

#include "xparameters.h"

#include "xil_io.h"

Xuint32*baseaddr_p=(Xuint32*)XPAR_MYIP_0_S00_AXI_BASEADDR;

int main()

{

init_platform();

print("Hello World ");

print("My_IP Test..... ");

//*(baseaddr_p+0)=0x00020003;

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR,0x11111111);

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x4,0x2);

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x8,0x990);

Xil_Out32(XPAR_MYIP_0_S00_AXI_BASEADDR+0xc,0x100);

u32r0,r1,r2,r3;

r0=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR);

r1=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x4);

r2=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR+0x8);

r3=Xil_In32(XPAR_MYIP_0_S00_AXI_BASEADDR+0xc);

xil_printf("r0=%0X r1=%0X r2=%0Xr3=%0X ",r0,r1,r2,r3);

cleanup_platform();

return0;

}

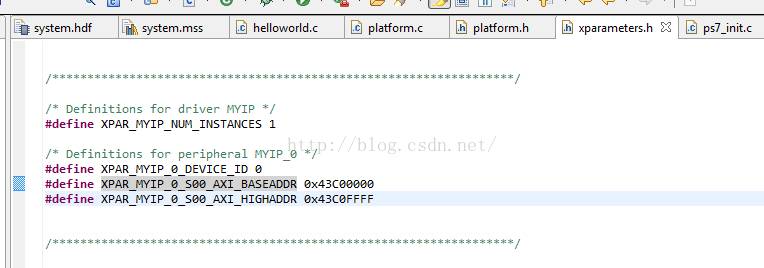

添加的xparameters.h头文件包含了自定义的IP的系统地址:

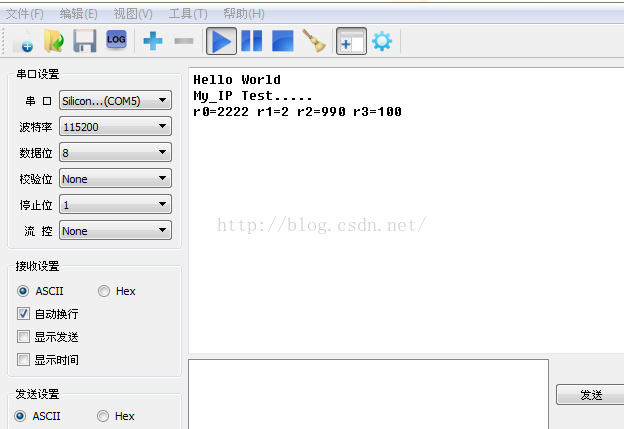

编译之后,先将bit文件下载到fpga,然后run,看到

好了,实验结束。