相比较经典的FPGA,Zynq7000系列最大的特点是将处理系统PS和可编程资源PL分离开来,固化了PS系统的存在,实现了真正意义上的SOC(System On Chip)。

1. Zynq7000系列特征概述

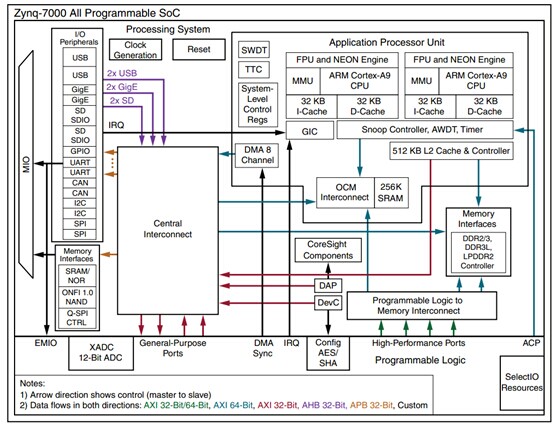

Zynq7000系列是全可编程片上系统,主要包含PS(processing system)和PL(Programmable Logic)两部分。PL采用28nm工艺;PS以2个Cortex A9的ARM核为核心,还包括片上存储器、片外存储器接口(DDR)和一系列的外设接口。Zynq7000系列将ARM CPU和外设集成在一个芯片内,使得Zynq7000系列皆具处理器和FPGA双重特性,特别适用于软硬件协同设计。

图1 Zynq-7000 All Programmable SoC Overview

1.1. PS部分特征

- 双Cortex-A9 ARM核

2.5 DMIPS/MHz per CPU

CPU frequency最高达1GHZ

单精度和双精度的向量浮点单元VFPU

3个看门狗定时器

1个全局定时器

2个 triple-timer 计数器

- Caches

每个CPU独立拥有32KB1级cache

两个CPU共享512KB的2级cache

- On-Chip Memory

片上自举ROM(boot rom)

256KB片上RAM

- External Memory Interfaces

16-bit or 32-bit DDR接口(DDR3, DDR3L, DDR2, or LPDDR2),当器件为DDR3时,最高数据速度可达1066 Mb/s。DDR 控制器有4个数据端口可用于对DDR的读写,分别命名为A、B、C、D。A专用于ARM CPU,B、C专门用于PL部分;D连接到interconnect.单元,可被interconnect上的其他主设备访问。

最高达1GB的地址空间

静态存储器接口(8-bit SRAM,Parallel NOR flash,ONFI1.0 NAND flash,1-bit SPI, 2-bit SPI, 4-bit SPI (quad-SPI), or two quad-SPI (8-bit) serial NOR flash)

- 8-Channel DMA Controller

支持Memory-to-memory, memory-to-peripheral, peripheral-to-memory, scatter-gather 交易。总线接口为64-bit AXI interface,其中有4个通道专用于与PL部分的通信。

- I/O Peripherals and Interfaces

2个 10/100/1000 tri-speed Ethernet MAC peripherals,接口为GMII, RGMII, and SGMII

2个 USB 2.0 接口

2个 CAN 2.0接口

2个SD 卡接口

2个双向SPI接口

2个高速UART接口

两个IIC接口

- GPIO

共118个,其中54个从PS直接连出去GPIO口(通过MIO),64个连接到PL的GPIO口;

最多54可复用IO(MIO)用于外设如USB、UART等的引脚分配,若使能的外设比较多,MIO个数不够时,可以将某些外设的引脚连接到PL,由PL通过通用IO口连接外部设备。如下图所示,并不是所有外设IOP都可以连接到PL,如USB就不可以连接到PL。

图2 MIO Module Block Diagram

- Interconnect

APU,、存储器单元、外设IOP、PL通过interconnect实现高速互联,interconnect支持多个主从设备的互相访问

- PS部分启动方式

PS部分采用众所周知的多阶段启动法,支持NOR, NAND, Quad-SPI, SD,or JTAG.启动。

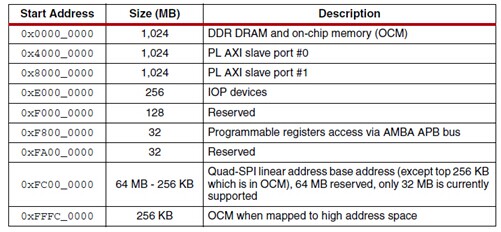

- 地址映射

图2 Zynq7000系列地址映射图

1.2. PL部分特征

该部分资源数目因器件型号不同而不同,以下所列数目皆为XQ7Z045的资源数。

- Configurable Logic Blocks (CLB)

CLB=305K/2个;

- 36 Kb Block RAM

545个

- Programmable DSP Slices

900个,主要是18X25的乘法器和48bit宽度的加法器;

- JTAG Boundary-Scan

- PCI Express Block

Gen2 Speed(5Gbps),最多8个。

- Serial Transceivers

最多16个,最高速度10.3125Gbps

- Two 12-Bit Analog-to-Digital Converters

2个12bit的数模转换器,最高转换速度1MSPS,最多支持17个外部输入。

- 时钟资源

XQ7Z045包含8个CMT,即8个MMCM+8个PLL;其输出时钟相位可为45°、90°、135°、180°、225°、275°、315°;

1.3. PS-PL 接口

PS和PL部分之间有多个接口,具体包括:

1、AXI类数据接口

2个32bit的AXI 主接口

2个32bit的AXI从接口

专用于PL访问DDR控制器的32/64bit的AXI从接口

1个64bit的访问CPU存储器的从接口

2、其他接口

DMA通道信号

PS的中断输入信号

事件信号

触发信号

EMIO

PS提供给PL的时钟信号及复位信号

XADC接口

JTAG接口