本文由知乎

赵俊军授权转载,知乎主页为https://www.zhihu.com/people/zhao-jun-jun-19

8.9 举例

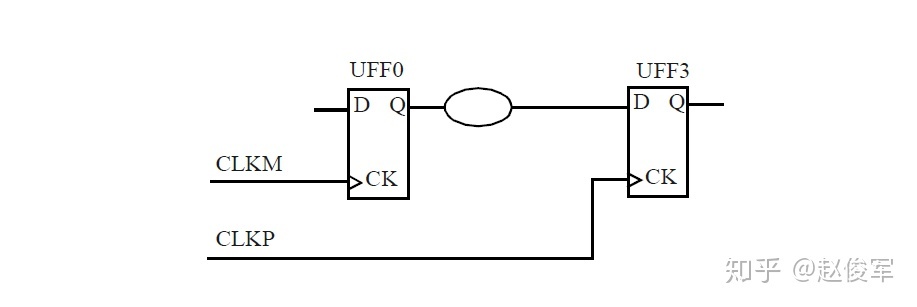

在本节中,我们将介绍发起和捕获时钟的不同情况,并分别说明如何执行建立时间和保持时间检查。图8-28为所举例子的示意图:

半周期路径——情况1

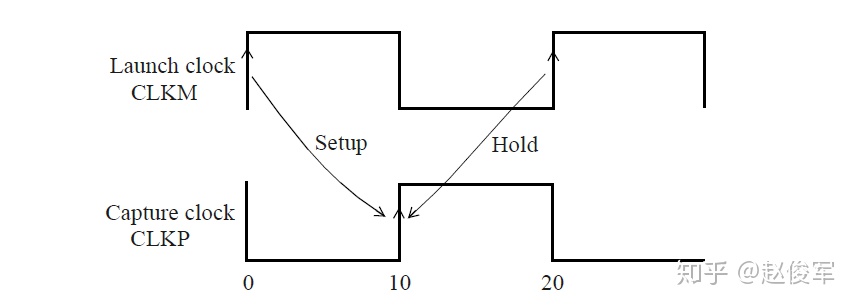

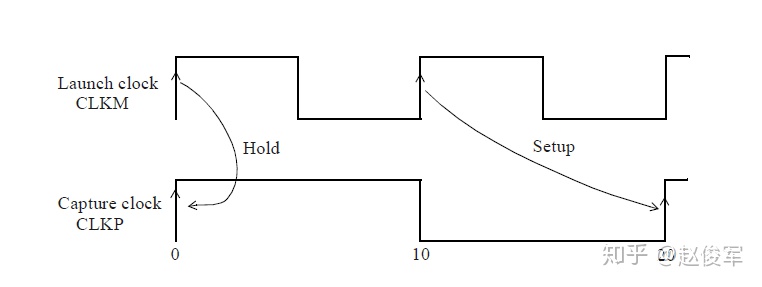

在此示例中,两个时钟具有相同的周期,但相位相反。以下是时钟定义,其波形如图8-29所示。

-

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

-

create_clock -name CLKP -period 20 -waveform {10 20} [get_ports CLKP]

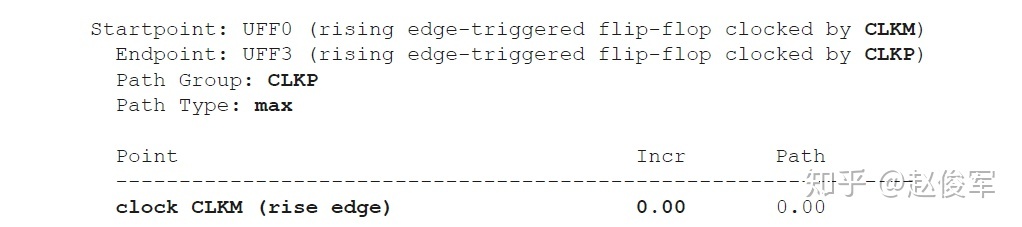

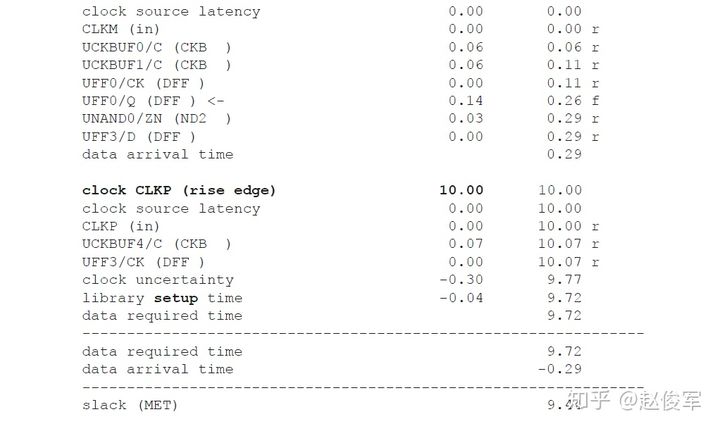

建立时间检查是从发起沿(0ns)到下一个捕获沿(10ns)的。半个时钟周期的裕量可用于保持时间检查,以验证在20ns处发起的数据是否在10ns处未被捕获沿所捕获。以下是建立时间检查的路径报告:

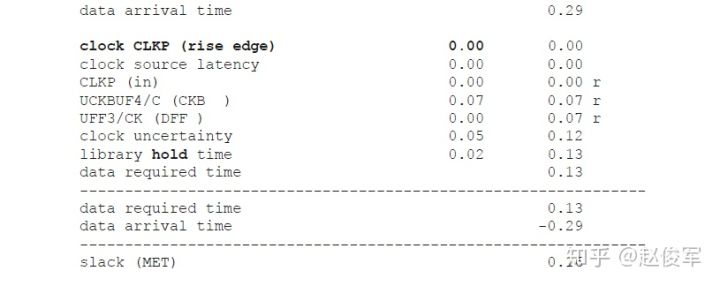

以下是保持时间检查的路径报告:

半周期路径——情况2

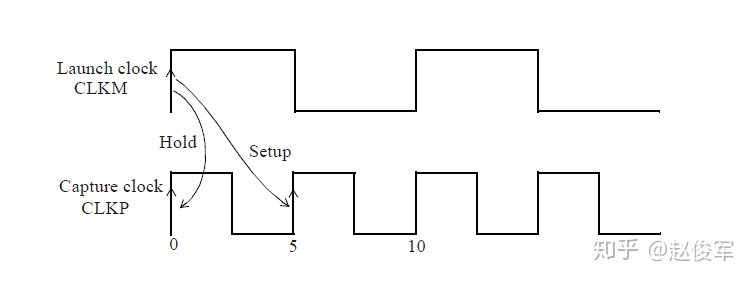

此示例与情况1类似,不过发起时钟和捕获时钟的相位相反。以下是时钟定义,其波形如图8-30所示。

-

create_clock -name CLKM -period 10 -waveform {5 10} [get_ports CLKM]

-

create_clock -name CLKP -period 10 -waveform {0 5} [get_ports CLKP]

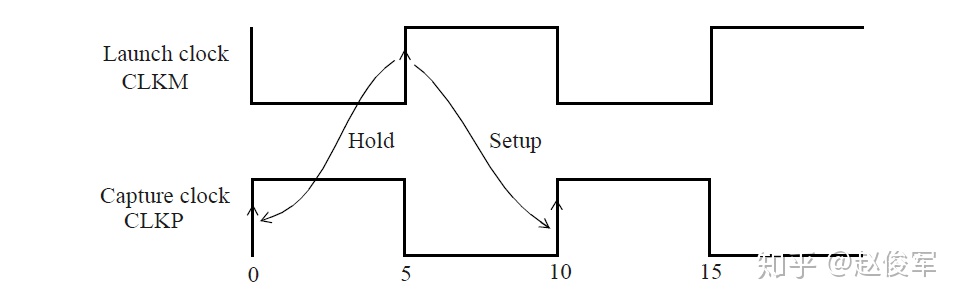

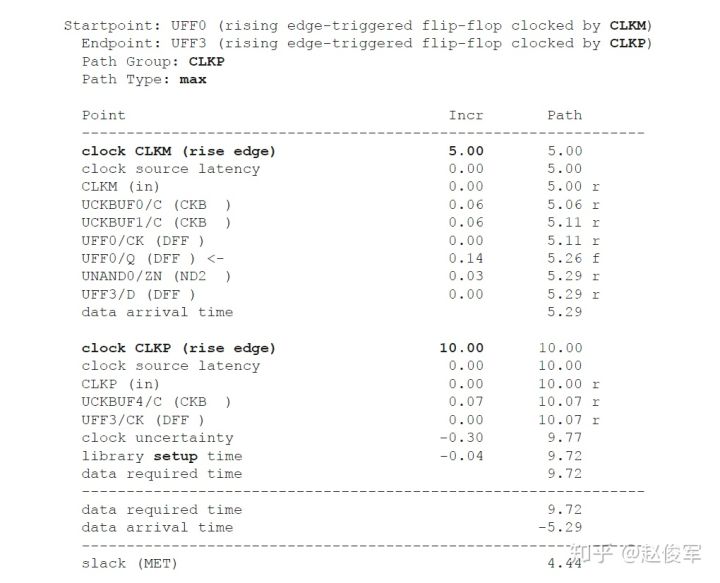

建立时间检查从5ns的发起时钟沿到10ns的下一个捕获时钟沿。保持时间检查从5ns的发起时钟沿到0ns的捕获时钟沿。以下是建立时间检查的路径报告:

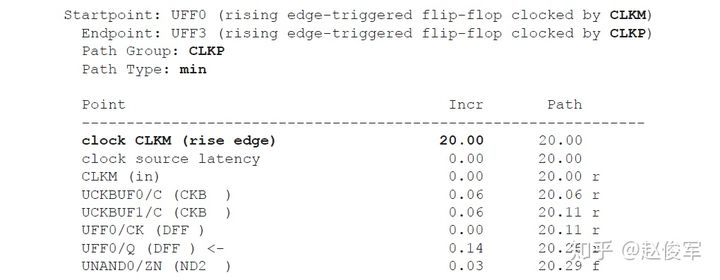

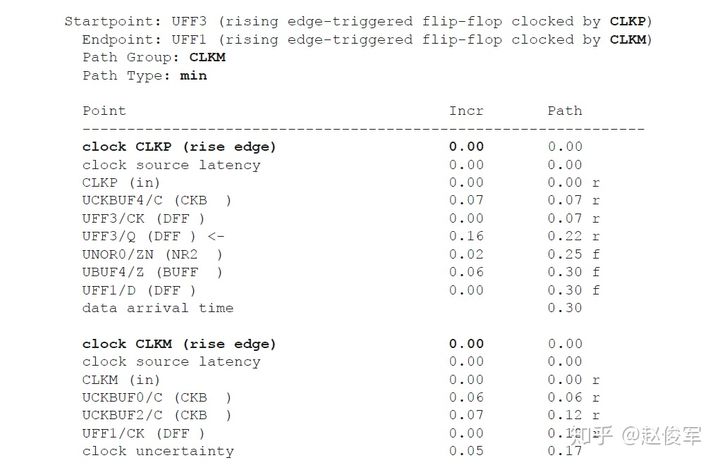

以下是保持时间检查的路径报告:

快速时钟域到慢速时钟域

在此示例中,捕获时钟是发起时钟的二分频。以下是时钟定义:

-

create_clock -name CLKM -period 10 -waveform {0 5} [get_ports CLKM]

-

create_clock -name CLKP -period 20 -waveform {0 10} [get_ports CLKP]

波形如图8-31所示。建立时间检查是从10ns的发起沿到20ns的捕获沿,保持时间检查是从0ns的发起沿到0ns的捕获沿。以下是建立时间检查的路径报告:

以下是保持时间检查的路径报告:

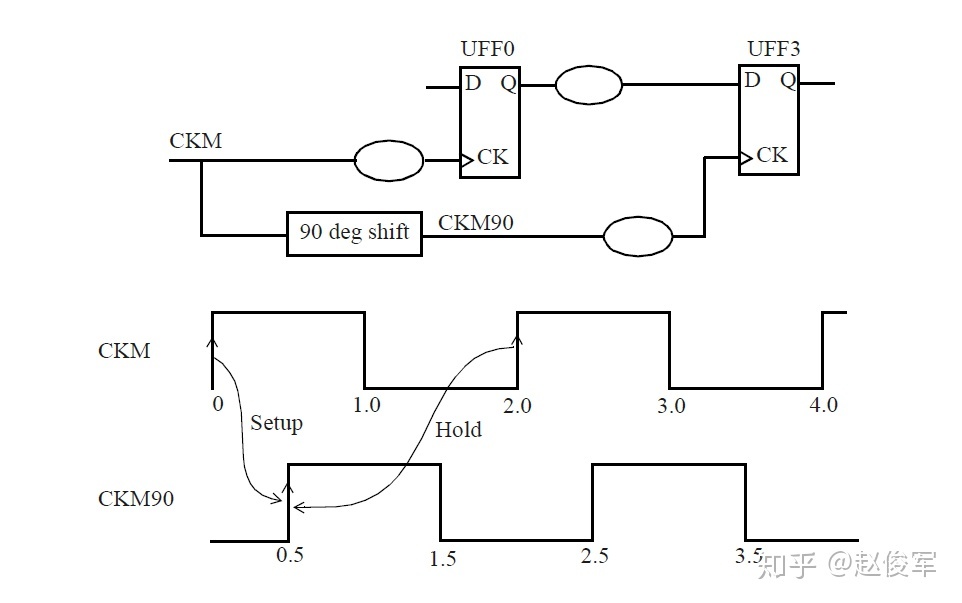

慢速时钟域到快速时钟域

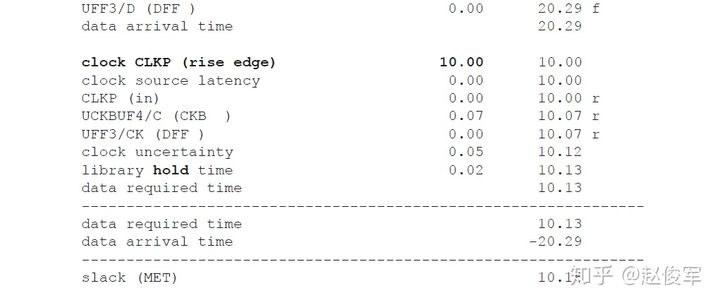

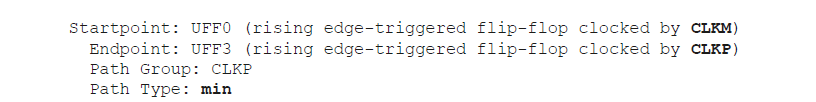

在此示例中,捕获时钟速度是发起时钟速度的2倍。图8-32中为建立时间和保持时间检查对应的时钟沿:从发起沿0ns到下一个捕获沿5ns进行建立时间检查,保持时间检查是在建立时间捕获沿前一个周期的捕获沿进行的,也就是说,发起沿和捕获沿都为0ns。

以下是建立时间检查的路径报告:

以下是保持时间检查的路径报告:

8.10 多时钟

8.10.1 整数倍

在设计中通常会定义多个时钟,这些时钟的频率是彼此的整数倍。在这种情况下,会通过计算所有相关时钟(related clocks)之间的公共基本周期来执行STA(如果两个时钟域之间具有数据路径,则两个时钟相关)。建立公共基本周期的目的是以便所有时钟都同步。

以下是3个相关时钟的示例:

-

create_clock -name CLKM -period 20 -waveform {0 10} [get_ports CLKM]

-

create_clock -name CLKQ -period 10 -waveform {0 5} [get_ports CLKQ]

-

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

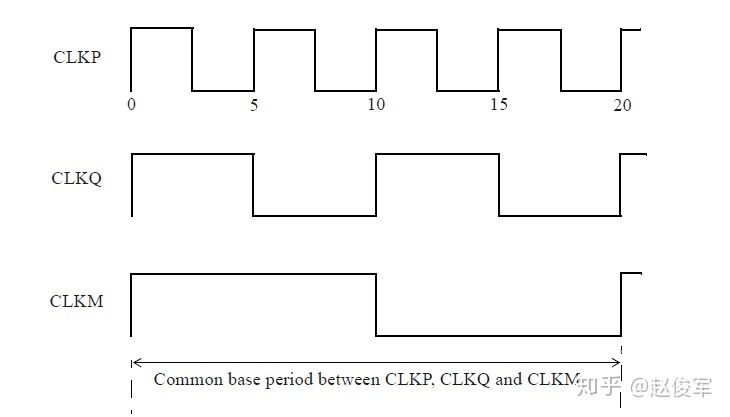

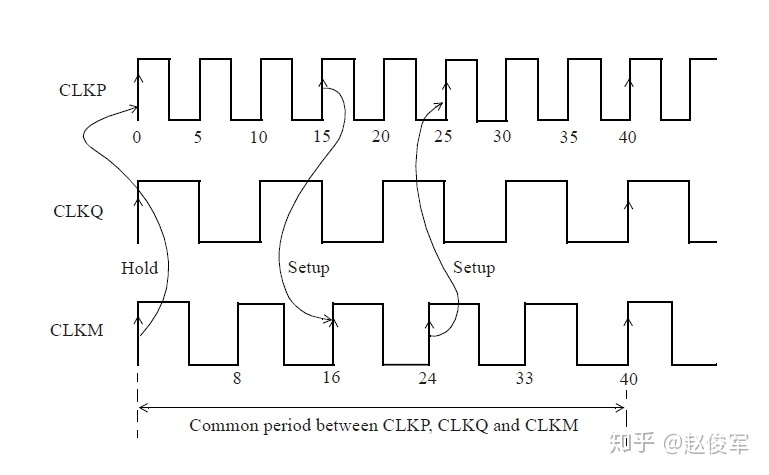

分析CLKP和CLKM时钟域之间的路径时,将使用20ns的公共基本周期,如图8-33所示。

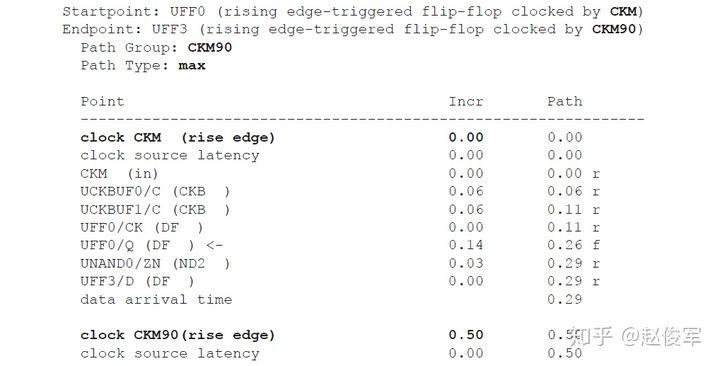

以下是建立时间检查的路径报告,用于从较快时钟CLKP到较慢时钟CLKM的路径。

相应保持时间检查的路径报告如下:

8.10.2 非整数倍

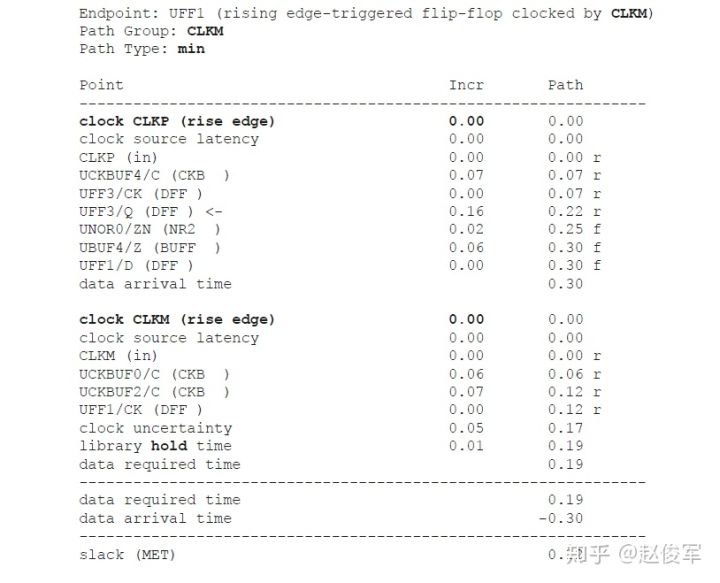

考虑当两个频率不是彼此整数倍的时钟域之间存在数据路径的的情况。例如,发起时钟是公共时钟的8分频,而捕获时钟是公共时钟的5分频,如图8-34所示。本节将介绍在这种情况下如何执行建立时间和保持时间检查。

以下是时钟定义,其波形如图8-35所示:

-

create_clock -name CLKM -period 8 -waveform {0 4} [get_ports CLKM]

-

create_clock -name CLKQ -period 10 -waveform {0 5} [get_ports CLKQ]

-

create_clock -name CLKP -period 5 -waveform {0 2.5} [get_ports CLKP]

时序分析会先计算相关时钟的公共周期,然后再将时钟扩展到该公共周期。请注意,仅针对相关时钟(即在它们之间具有时序路径的时钟)去计算公共周期。CLKQ和CLKP之间数据路径的公共周期仅扩展为10ns的公共周期,CLKM和CLKQ之间数据路径的公共周期为40ns,而CLKM和CLKP之间数据路径的公共周期也为40ns。

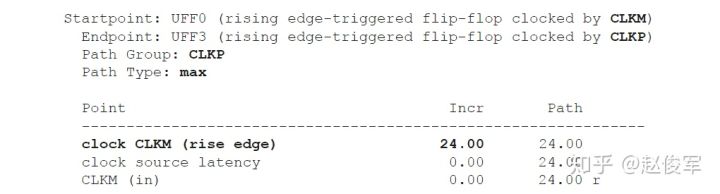

让我们考虑一条从CLKM时钟域到CLKP时钟域的数据路径,这种情况下时序分析的公共基本周期为40ns。

建立时间检查在时钟发起沿和捕获沿之间的最短时间内进行。在我们从CLKM到CLKP的示例路径中,这就是24ns处的时钟CLKM发起沿以及25ns处的时钟CLKP捕获沿。

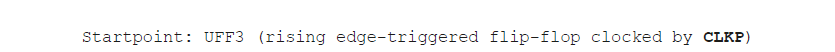

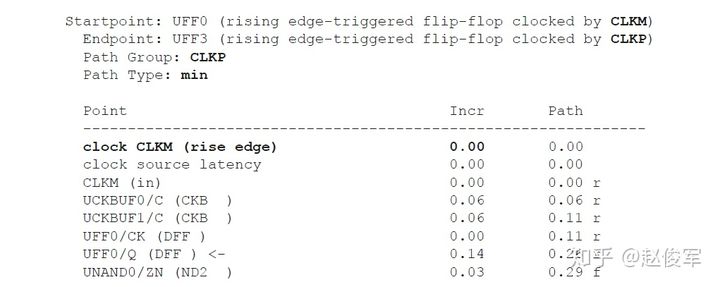

以下是保持时间检查的路径报告,最严格的保持时间检查是从0ns处的CLKM发起沿到0ns处的CLKP捕获沿。

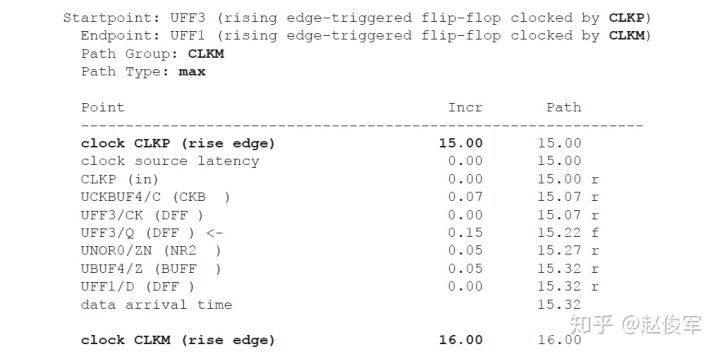

现在,我们对从CLKP时钟域到CLKM时钟域的路径的建立时间进行检查。在这种情况下,最严格的建立时间检查是从15ns处的时钟CLKP发起沿到16ns处的时钟CLKM捕获沿。

以下是保持时间检查的路径报告,同样,最严格的还是0ns处的检查。

8.10.3 移相

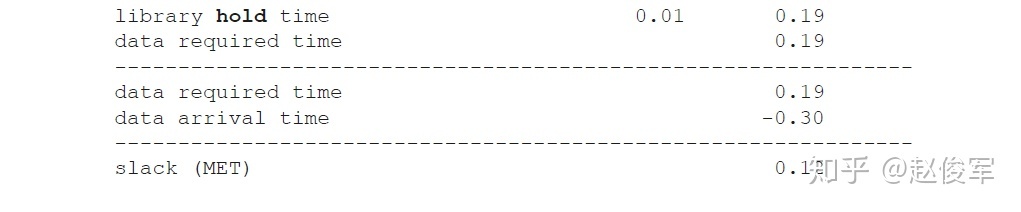

在以下示例中,两个时钟有90°的相移(phase shift):

-

create_clock -period 2.0 -waveform {0 1.0} [get_ports CKM]

-

create_clock -period 2.0 -waveform {0.5 1.5} [get_ports CKM90]

图8-36给出了使用这两个时钟的示例。建立时间检查的路径报告如下:

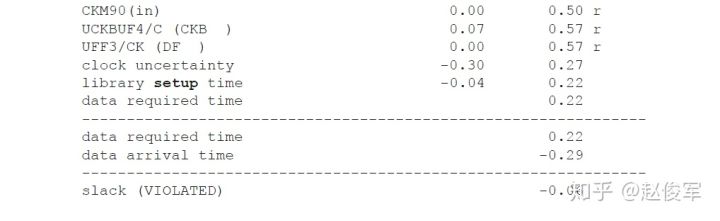

0.5ns处的CKM90第一个上升沿是捕获沿,保持时间检查是在建立时间捕获沿之前一个周期的时钟沿处。对于2ns的发起沿,建立时间捕获沿为2.5ns,因此保持时间检查沿就在0.5ns处的前一个捕获沿。保持时间检查的路径报告如下:

在第10章中还会介绍其它时序检查,例如数据到数据(data to data)检查和时钟门控(clock gating)检查。