我们做项目,进入找bug阶段时,需要用ILA捕获相关的信号。之前我做项目,每改动一次探针(debug probes),都要重新综合、实现,通常要花掉1个小时,一天下来调试不了两下就过去了,效率极其低下,因此也吐槽过vivado的编译时间问题。这两天无意从高老师的公众号中看了高效的方法,有种相见恨晚的感觉。因为从原来的1个小时,提升到了5-10分钟,感激涕零。

根据高老师的公众号的介绍,我自己手动操作一遍,记录一下相对详细的操作方法。

1. 什么是ECO

ECO 指的是Engineering Change Order ,即工程变更指令。目的是为了在设计的后期,快速灵活地做小范围修改,从而尽可能的保持已经验证的功能和时序。ECO 的叫法算是从IC 设计领域继承而来,其应用在FPGA设计上尚属首次,但这种做法其实在以往的FPGA 设计上已被广泛采用。简单来说, ECO 便相当于ISE 上的FPGA Editor 。但与FPGA Editor 不同, Vivado 中的ECO 并不是一个独立的界面或是一些特定的命令,要实现不同的ECO 功能需要使用不同的方式。

我们的操作环境就是在ECO模式下进行的。

2. 操作步骤

基于vivado 2016.4

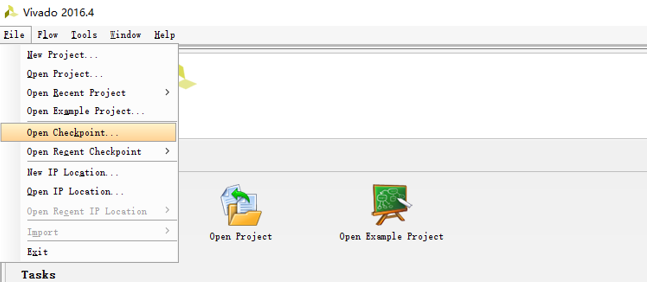

- 打开布线DCP文件

经过综合、实现后的工程,会生产几个DCP文件,其中一个是布线文件(routed dcp)。通过“open Checkpoint”打开。

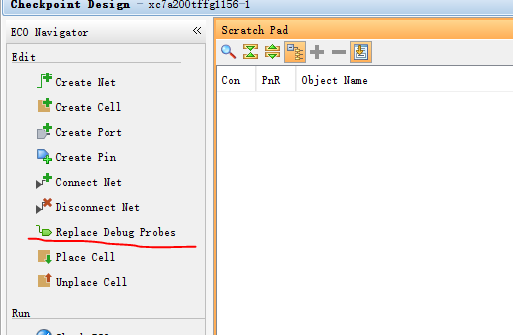

将vivado layout切换为ECO模式。

- replace debug probes

点击“ECO Navigator”栏中的“Replace Debug Probes”,会出现之前设计的ILA中的各种探针,一个探针代表一个观测信号。

选中要被替换的信号,右键点击“Edit Probes”或者点击最右侧的"铅笔"标志,会出现“Choose Nets”小窗口,查询需要用来替换的信号。

注意事项:最开始我直接搜索代码中的信号名,一直搜索不出来。结果忽视了综合、实现过程中,已将代码转换为网表,所以只能用schematic中的nets名来进行搜索。

查到nets之后,移向右侧。各种确定之后保存,这就完成了debug probes的替换工作。

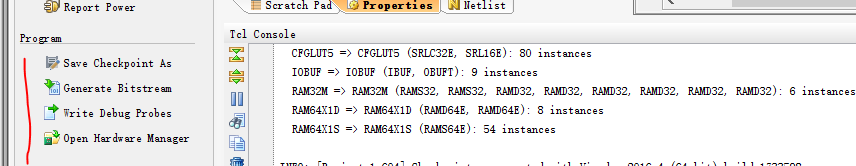

- 生成新的bit 、ltx文件

在Navigator栏最下面保存、生成bit和ltx文件。就可以进行新的测试了。

关于ECO还有更多内容,包括手动布局、布线之类的,可以参考官方文档UG904。

参考文献:

- UG904;

- 《替换Debug Probes其实很简单》——高亚军;