概念

MIO

MIO:多功能IO接口(分配在 GPIO 的 Bank0 和Bank1),属于Zynq的PS部分,在芯片外部有54个引脚。这些引脚可以用在GPIO、SPI、UART、TIMER、Ethernet、USB等功能上,每个引脚都同时具有多种功能,故叫多功能。这些 IO 与 PS 直接相连。不需要添加引脚约束,MIO 信号对 PL部分是透明的,不可见。所以对 MIO 的操作可以看作是纯 PS 的操作。

// xparameters.h

#define XPAR_PS7_GPIO_0_DEVICE_ID 0

#define XPAR_PS7_GPIO_0_BASEADDR 0xE000A000

#define XPAR_PS7_GPIO_0_HIGHADDR 0xE000AFFF

GPIO 的控制和状态寄存器基地址为:0xE000_A000,我们 SDK 下软件操作底层都是对于内存地址空间的操作。

一个GPIO端口至少需要两个寄存器,一个控制用的通用IO口控制寄存器和一个存放数据的通用IO端口数据寄存器。

GPxCON寄存器为控制寄存器,它的每一位对应一个引脚,其某位设为0,相应的引脚为输出引脚,为1时为输入引脚。

GPxDAT为数据寄存器,当引脚设为输入时,读此寄存器可以知道相应的引脚的电平状态为高还是低,当引脚设为输出时,写此寄存器可令此引脚输出为高电平或者低电平。

Bank0有32个MIO引脚,Bank1有22个MIO引脚,54个引脚直接通过MIO连接到PS上,不需硬件配置,直接使用SDK软件进行编程。

EMIO

EMIO:Extend multiuse I/O,分布在BANK2、BANK3,依然属于Zynq的PS部分,只是连接到了PL上,再从PL的引脚连到芯片外面实现数据输入输出。当我们想通过PS来访问PL又不想浪费AXI总线时,就通过EMIO接口来访问。在54个I/O中,有一些只能用于MIO,大部分可以用于MIO与EMIO,一些接口信号线只能通过EMIO访问。

下图为Vivado工程里ZYNQ CPU核配置,确保EMIO勾选,设置了多少位位宽,即为其分配了多少个管脚,再添加管脚约束文件,指向相应的PL部分管脚。

EMIO依然属于PS,只是连接到了PL,再从PL输出信号。

Q:如何理解这句话?

A:相当于说,点亮PS的对应的控制器,但是此时的外部引脚是不确定的;必须通过PL端进行管脚约束,才能知道这个控制器的外部引脚连到了哪里。

换句话说,PS控制了时序,PL端提供了引脚。

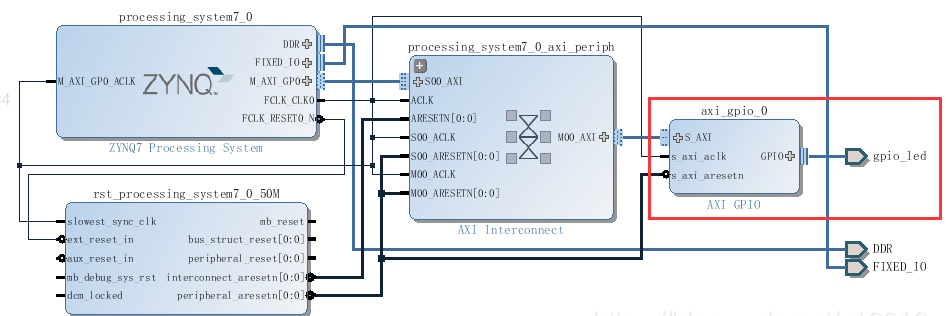

AXI_GPIO

AXI(Advanced eXtensible Interface)是一种总线。

AXI_GPIO相当于GPIO的IP核,是通过AXI总线挂在PS上的GPIO上。

EMIO的使用例程

以双串口为例:

实现功能:

① 实现数据直接从PS的MIO口接收与发送

② 通过PL口实现数据的接收与发送

③ 实现数据的双串口接收与发送(即PS可同时从两个UART口接收或发送数据)

新建工程——创建block design——添加Zynq ps IP——预设为Zedboard板

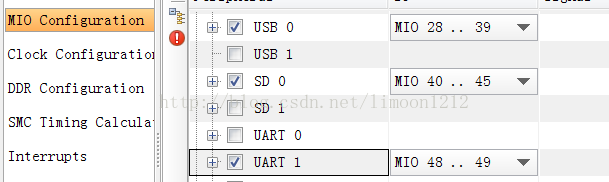

可以看到UART1 的48、49 MIO接口被选中(如下图)

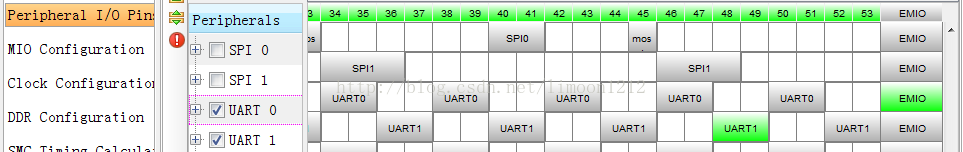

回到Peripheral I/OPins选项,勾选UART0,可以看到EMIO框框变亮

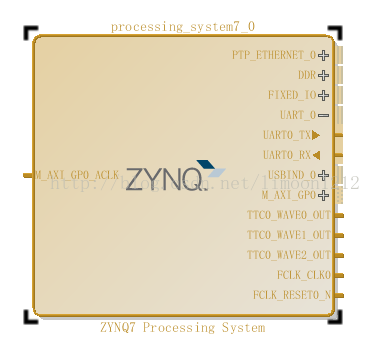

点击ok,此时的Zynq ps IP中,UART0已经添加,其中一个接收(UART0_RX),一个发送(UART0_TX)

接下来对UART0_RX、UART0_TX作约束

约束到Zedboard板的Pmod口上(本例中使用JA口进行扩展)约束文件如下:

set_propertyPACKAGE_PIN Y11 [get_ports UART0_RX]

set_propertyPACKAGE_PIN AA11 [get_ports UART0_TX]

set_propertyIOSTANDARD LVCMOS33 [get_ports UART0_TX]

set_propertyIOSTANDARD LVCMOS33 [get_ports UART0_RX]

生成比特流,进行SDK开发

此时便可从Pmod的JA1口和JA2口进行串口数据的接收与发送,实现从PL读取接收数据。

读取接收到的数据通过SDK编程实现在PS中处理数据,之后我们可以添加其它外设IP,用PS中处理后的数据控制外设IP。