阻抗匹配

阻抗:在具有电阻、电感和电容的电路里,对电路中的电流所起的阻碍作用叫做阻抗。

在设计电子电路时都需要考虑阻抗匹配,什么是阻抗匹配?为什么要进行阻抗匹配,下面列举三个典型方向说明:

一、获得最大功率。

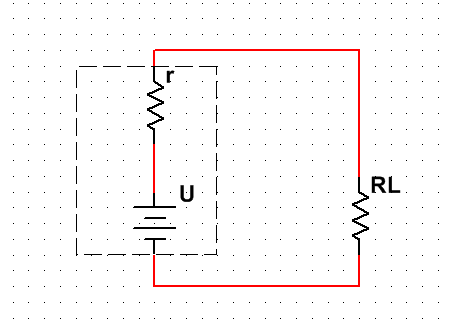

对于理想的电源,我们希望只有电压U,但实际上,每个电源都会有一个内阻,如图1-1所示,电源是由U和内阻r组成的。接入负载RL,要使负载获得最大的功率,RL取多大的值?由欧姆定律U=I*R得出

IRL=U/(RL+r)

URL=IRL*RL=U/(1+r/RL)

PRL=URL*IRL=U^2/[4*r+(RL-r)^2/r]

所以当RL=r时,(RL-r)^2/r取得最小值0,PRL值最大

图1-1

在喇叭上都会标注有4Ω、8Ω等字样,就是为了跟功放机的输出阻抗匹配,获得最大功率和更好的音质。

二、提高精度

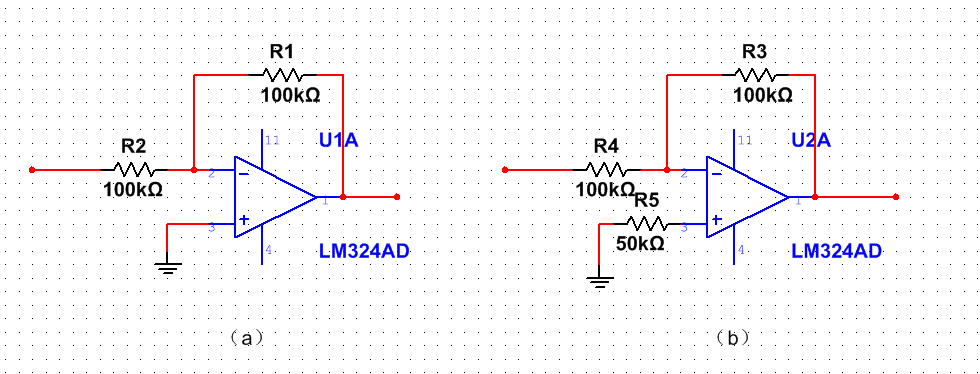

如图2-1,a图是教科书上典型的反相放大器,b图是另一种工程设计中见到的反相放大器,它们的功能是一样的,那么R5是做什么用的?我们称之为匹配电阻,那么为什么要加入这个匹配电阻呢?这时候就要看运放的规格书,如图2-2,是运放OPA369的规格参数,这里面有两个重要的参数,偏置电流IB、失调电流Ios。理想的运放是不存在这两个参数,但由于实际的制作工艺限制,也就是说,实际的运放输入,会有电流流入或流出运放的输入端的(与理想运放的虚断不太一样)。那么输入偏置电流就定义这两个电流的平均值,输入失调电流呢,就定义为两个电流的差。

问题来了,假如输入端输入电压为0V,但由于有电流流过电阻,必定会产生电压,输出得到的就不是0V,这时候匹配电阻的作用就是使正反相输入端产生的电压尽可能的相等,减小失调电压。

图2-1

图2-1 图2-2

图2-2

至于为什么R5取值50KΩ,请参考http://www.eepw.com.cn/article/284969.htm

偏置电流IB、失调电流Ios的详细讲解请参考http://www.deyisupport.com/question_answer/analog/amplifiers/f/52/t/18865.aspx

三、减小信号干扰

在高频电路中,如果走线的阻抗不匹配,在负载端就会产生反射,从而干扰到信号。首先了解为什么信号会反射?为什么是在高频电路中?

电磁波是一种波,与机械波一样都能发生折射、反射、衍射、干涉,因为所有的波都具有波动性。衍射、折射、反射、干涉都属于波动性。波在通过不同介质时,会发生衍射、折射、反射、干涉及吸收等等。详细请查询电磁学相关教材。那么由于阻抗不匹配,信号从源端到终端所经过的介质也就不一样,信号产生了反射。

频率与波长息息相关,根据麦克斯韦方程:

C(光速)=λ(波长)*f(频率) 得出:λ(波长)=C(光速)/ f(频率)

当然,信号在PCB板中是达不到光速的,电磁波在介质中的传播速度v=c(光速)/ ⊱(介电常数)

所以 λ=C/( f*⊱) 当信号的频率越高时波长越短。(详细物理知识请查阅麦克斯韦方程组的相关教材)

因此高频电路波长短,反射回来的信号很容易跟后面的信号叠加产生干扰。而低频电路的波长长,即使反射的信号来回跑了几趟达到稳态,然而低频的一个信号还没传完,所以不管你怎么反射,我一个波长很长的信号终将把你碾压。(这解释有点牵强,本人水平只到这里了,如果想再深入研究的话就请查看信号与完整性的相关教材,什么驻波啊、反射系数啊之类的,建议把高数学好再去研究)

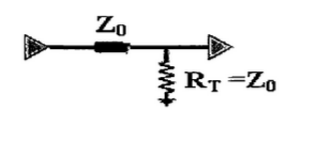

理解了电磁波的物理特性后,我们来看看图3-1

图3-1

图3-1

Vs为驱动源,Zs为等效驱动源内阻,ZL为等效负载,Zo为传输路径特性阻抗

那么当ZL=Zo时,入射电压Vinc全部到达负载不会反射(介质相同啦)

当ZL≠Zo时,入射电压Vinc一部分被反射,并在反射途中与入射电压叠加。当反射电压到达源端时,若Zs≠Zo将会产生第二次反射。

这就是反射干扰的问题,根本原因在于信号传输的延时与阻抗不匹配产生的反射,详细介绍请阅读http://www.dzsc.com/data/html/2008-10-17/71361.html

信号传输线的阻抗匹配分为以下几类:

一、源端串联端接

在通常的数字信号系统中,器件的输出阻抗通常是十几欧姆到二十几欧姆,传输线的阻抗通常会控制在50欧姆,所以匹配电阻常见为33欧姆电阻。当然要达到好的匹配效果,驱动端输出到串联电阻这一段的传输路径最好较短,短到可以忽略这一段传输线的影响。

串联电阻优缺点如下:

(1)优点

1、只需要一个电阻;

2、没有多余的直流功耗;

3、消除驱动端的二次反射;

4、不受接收端负载变化的影响;

(2)缺点

1、接收端的一次发射依然存在;

2、信号边沿会有一些变化;

3、电阻要靠近驱动端放置,不适合双向 传输信号;

4、在线上传输的电压是驱动电压的一半,不适合菊花链的多型负载结构。

二、远端并联端接

在通常的数字信号传输系统里,接收端的阻抗范围为几兆到十几兆,终端匹配电阻如果和传输线的特征阻抗相等,其和接收端阻抗并联后的阻抗大致还是在传输线的特征阻抗左右,那么终端的反射系数为0。不会产生反射,消除的是终端的一次反射。

并联电阻优缺点:

(1)优点

1、适用于多个负载

2、只需要一个电阻并且阻值容易选取

(2)缺点

1、增加了直流功耗

2、并联端接可以上拉到电源或者下拉到地,是的低电平升高或者高电平降低,减小噪声容限。

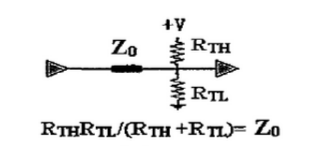

三、戴维南端接

戴维南端接同终端匹配,要达到匹配要求,终端的电阻并联值要和传输线的特征阻抗Z0相等。

优缺点描述:

(1)优点

1、适用于多个负载

2、很适用于SSTL/HSTL电平上拉或下拉输出阻抗很好平衡的情况。

(2)缺点

1、直流功耗增加

2、需要两个器件

3、端接电阻上拉到电源或下拉到地,会使得低电平升高或高电平降低

4、电阻值较难选择,电阻值取值小会使低电平升高,高电平降低更加恶劣;电阻值取大有可能造成不能完全匹配,使反射增大,可以通过仿真来确定。

四、RC端接

并联端接为消除直流功耗,可以加入电容。为达到匹配要求,端接的电阻应该和传输线的特征阻抗Z0相等。

优缺点描述如下:

(1)优点

1、适用于多个负载

2、无直流功耗增加

(2)缺点

1、电容取值十分复杂

2、增加了终端的容性负载,增加了RC电路造成的延时

3、对周期性的信号有效(如时钟),不适合于非周期信号(如数据)

传输线阻抗匹配例子:

1、485通讯中,信号两端并入一个120Ω的电阻。

2、串口通讯中,信号串入一个22Ω左右的电阻。

注:传输线匹配电阻应当慎用。