zynq-自定义IP

本教程不是商业教程,只是自己学习时,希望记录下来,可以反复查看学习,以免忘记。

此次是希望在CPU这端输出helloworld,在fpga这端点亮LED

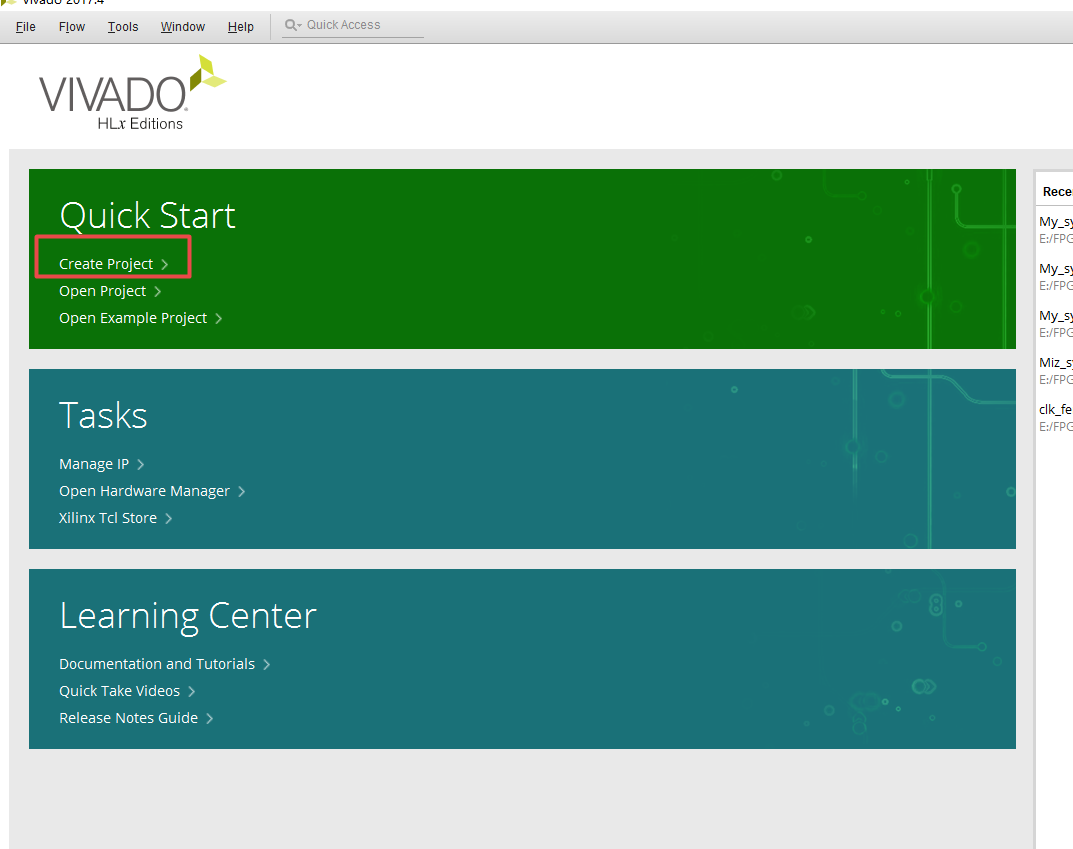

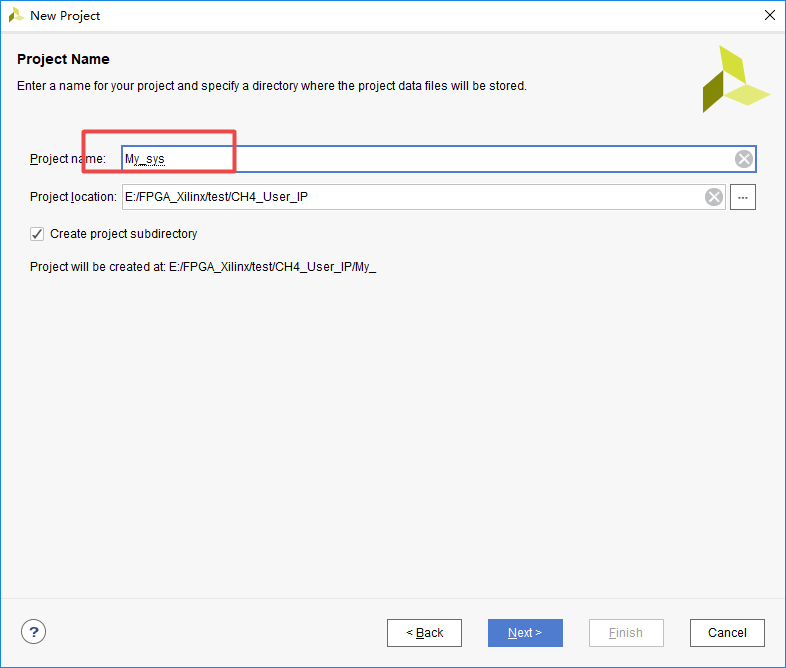

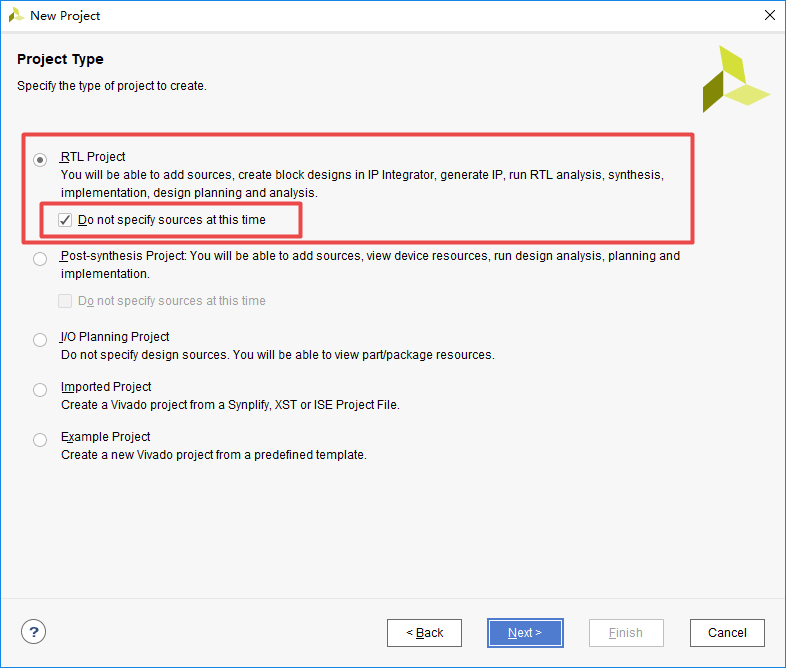

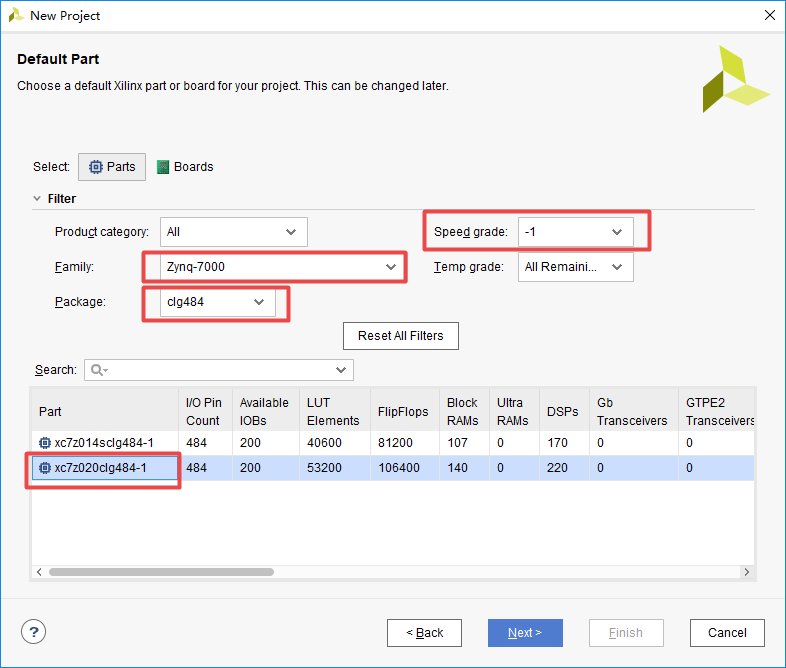

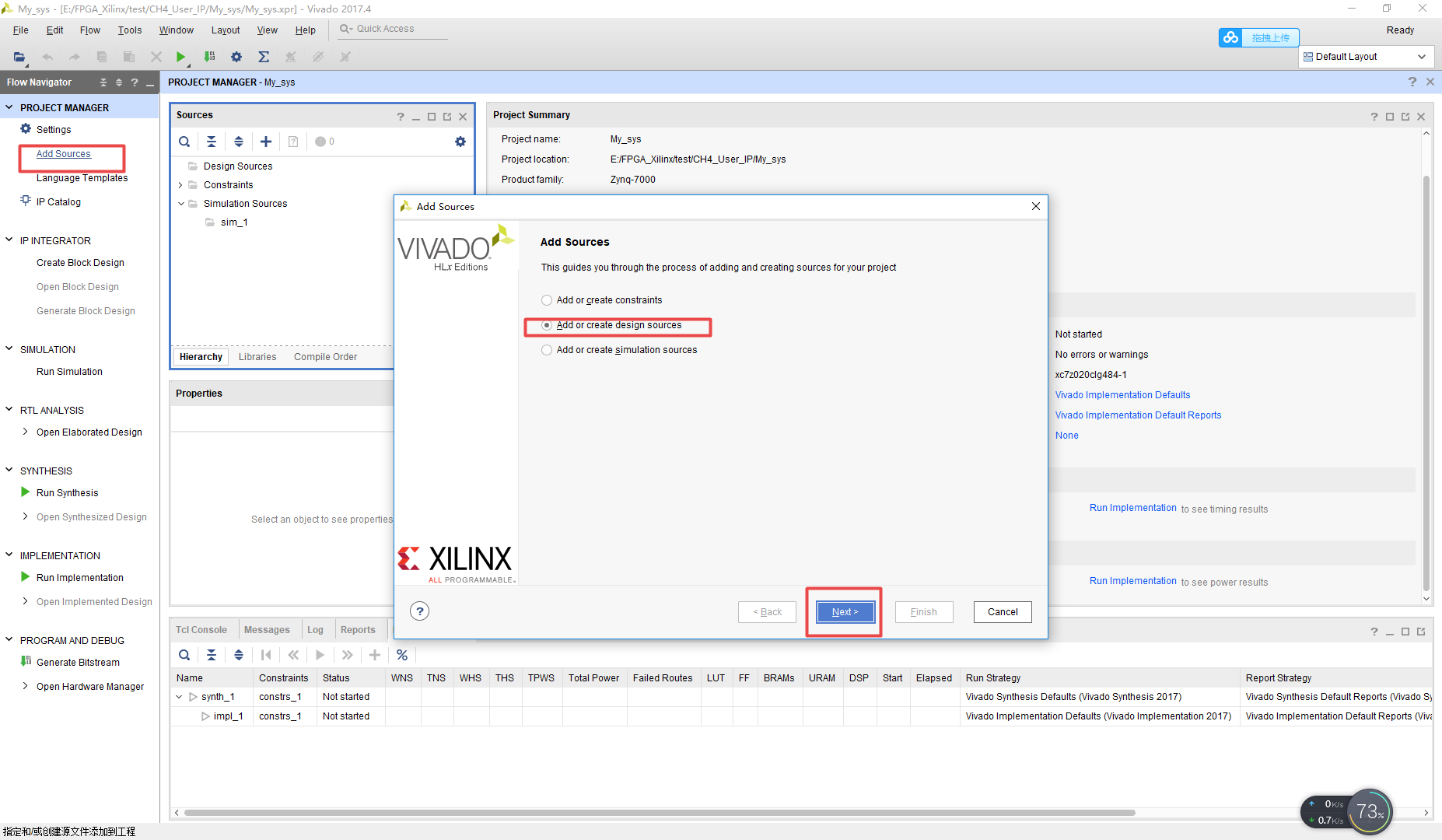

1.新建工程

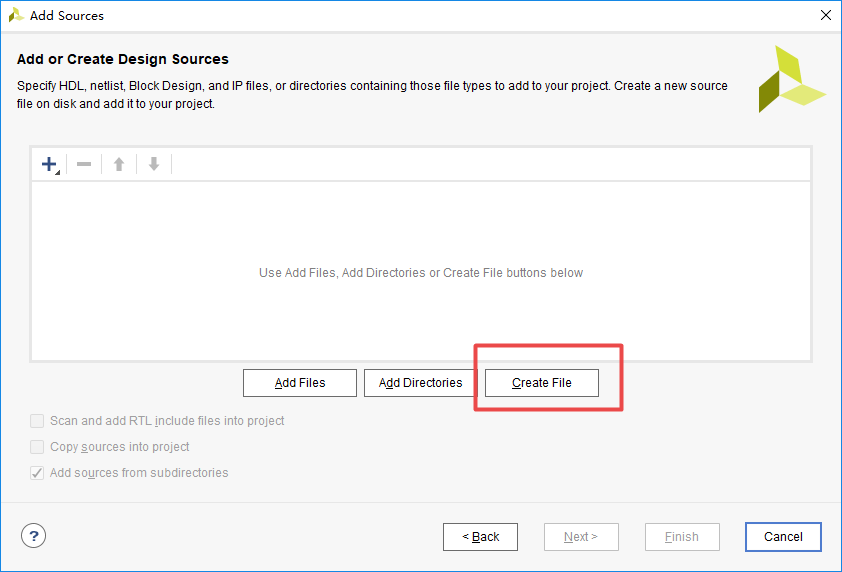

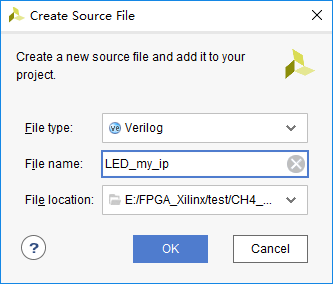

2.添加文件,编写verilog代码

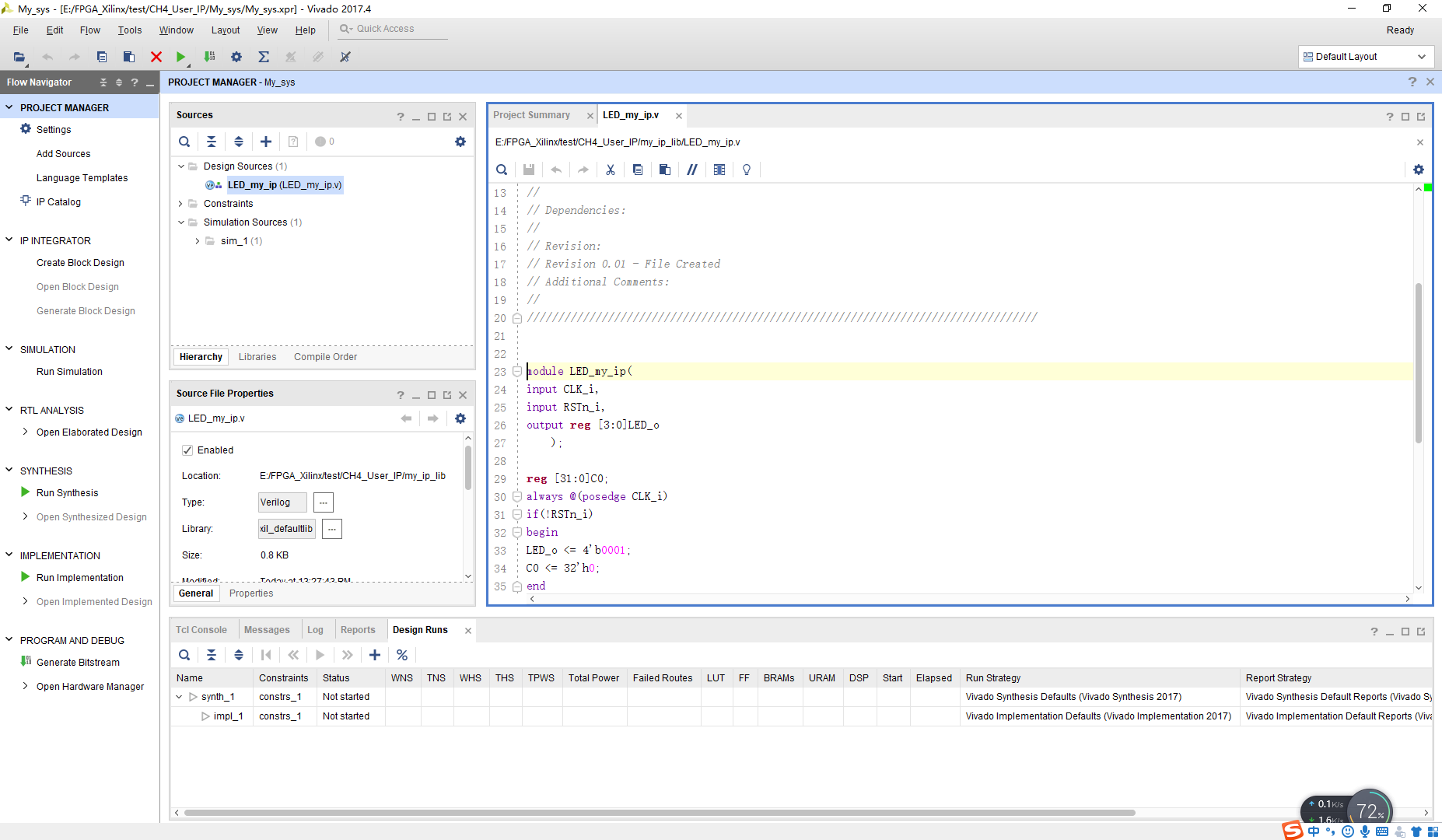

3.写入代码

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2019/02/13 13:26:19

// Design Name:

// Module Name: LED_my_ip

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module LED_my_ip(

input CLK_i,

input RSTn_i,

output reg [3:0]LED_o

);

reg [31:0]C0;

always @(posedge CLK_i)

if(!RSTn_i)

begin

LED_o <= 4'b0001;

C0 <= 32'h0;

end

else

begin

if(C0 == 32'd49_999_999)

begin

C0 <= 32'h0;

if(LED_o == 4'b1000)

LED_o <= 4'b0001;

else LED_o <= LED_o <<1;

end

else

begin

C0 <= C0 + 1'b1;

LED_o <= LED_o;

end

end

endmodule

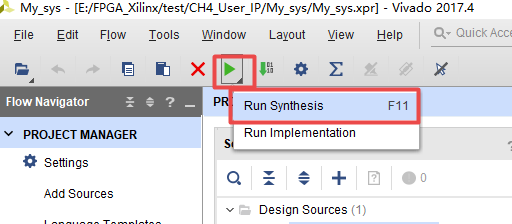

4.综合

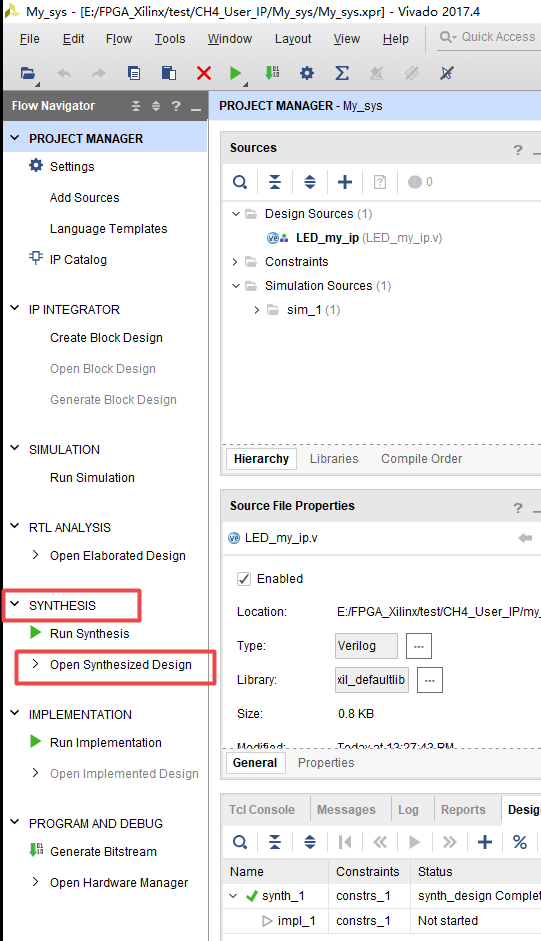

5。打开设计

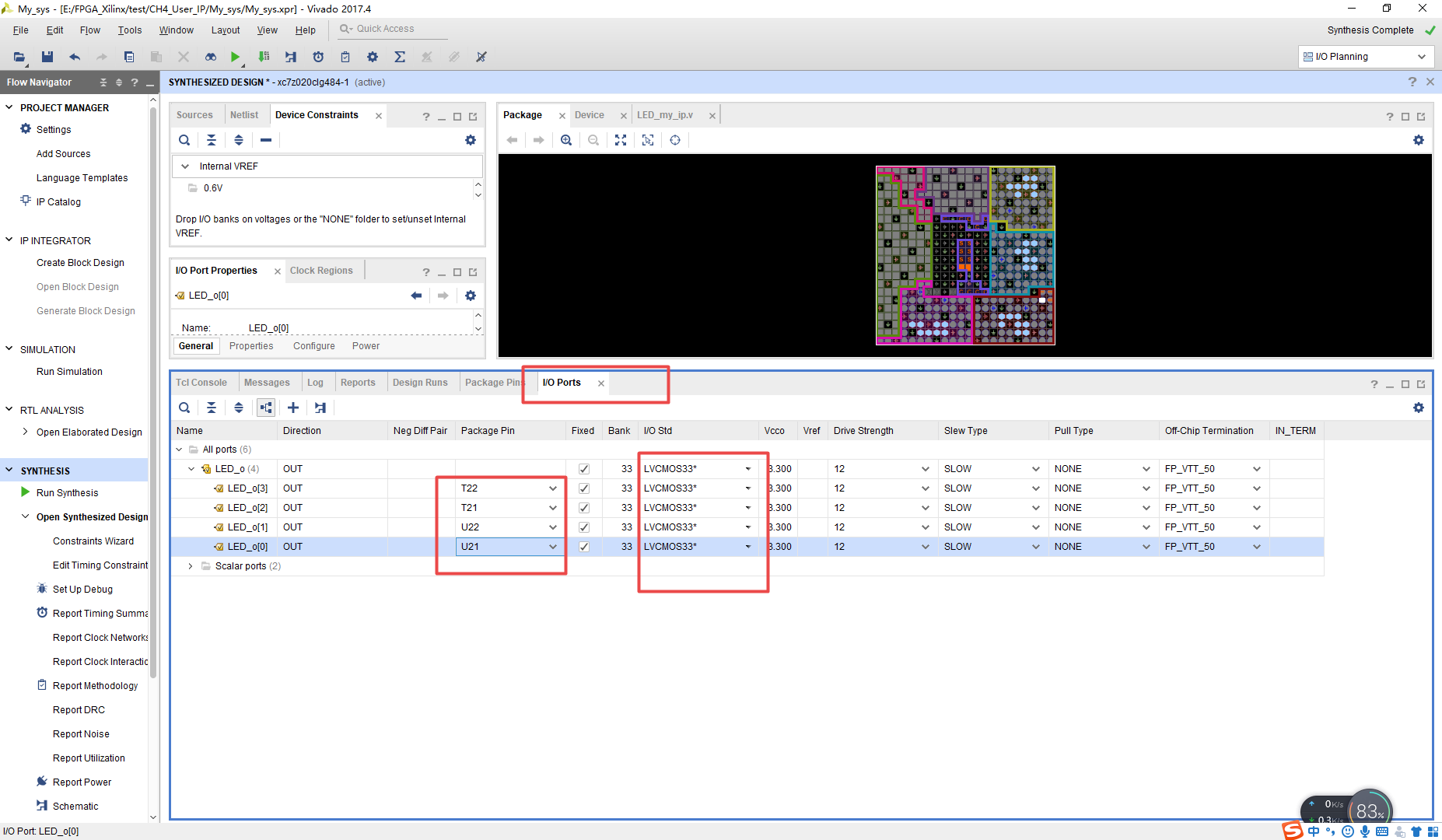

6.添加引脚约束

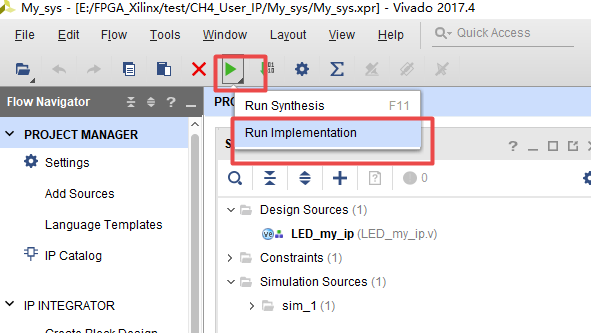

7.编译

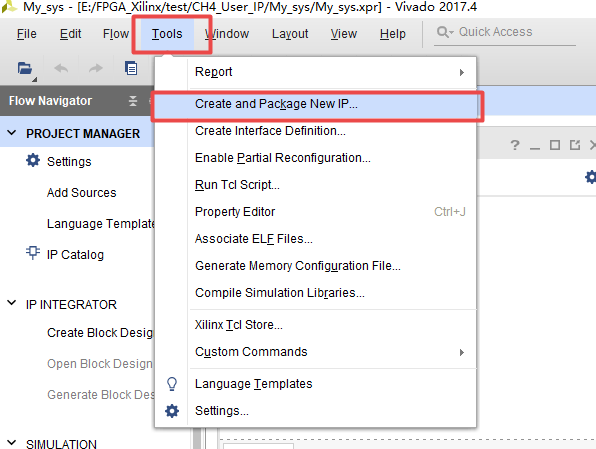

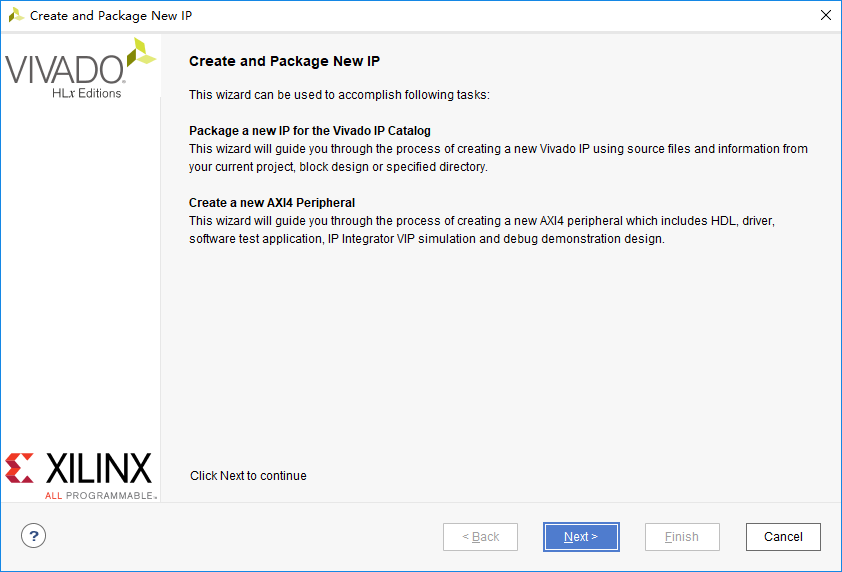

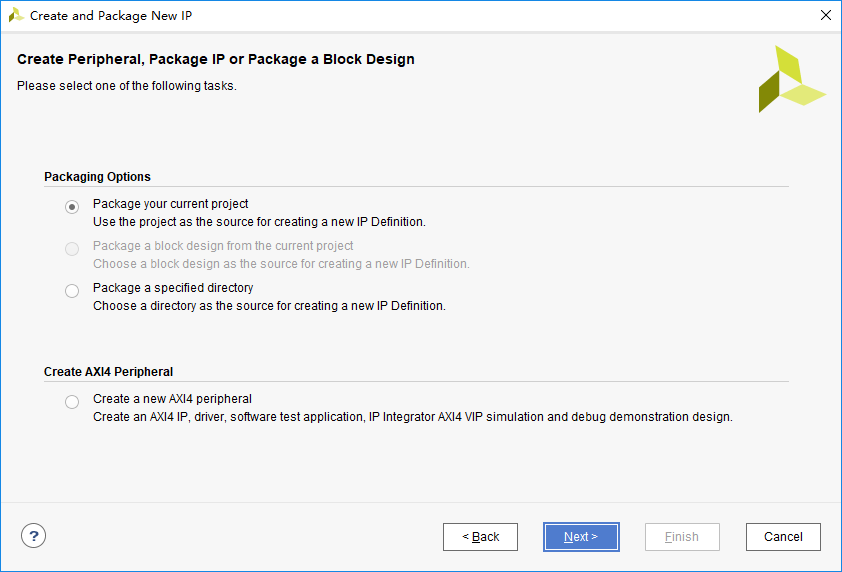

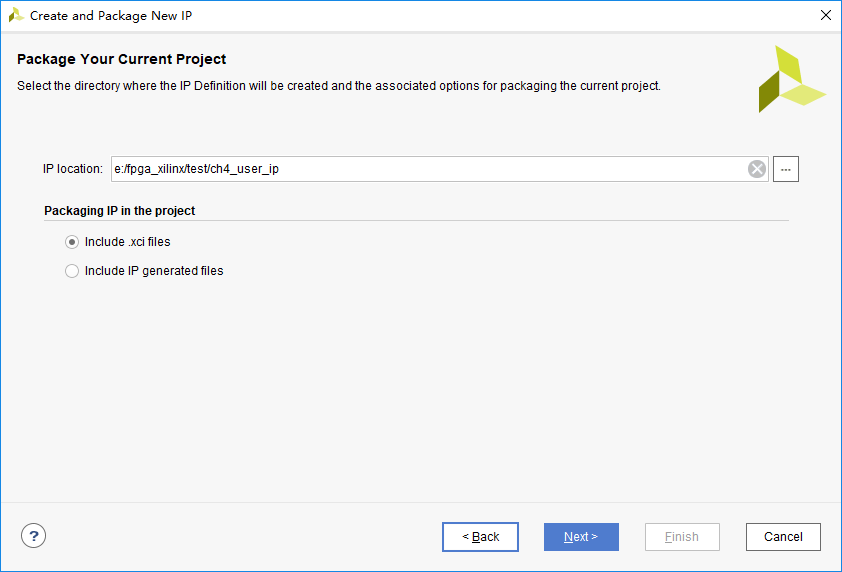

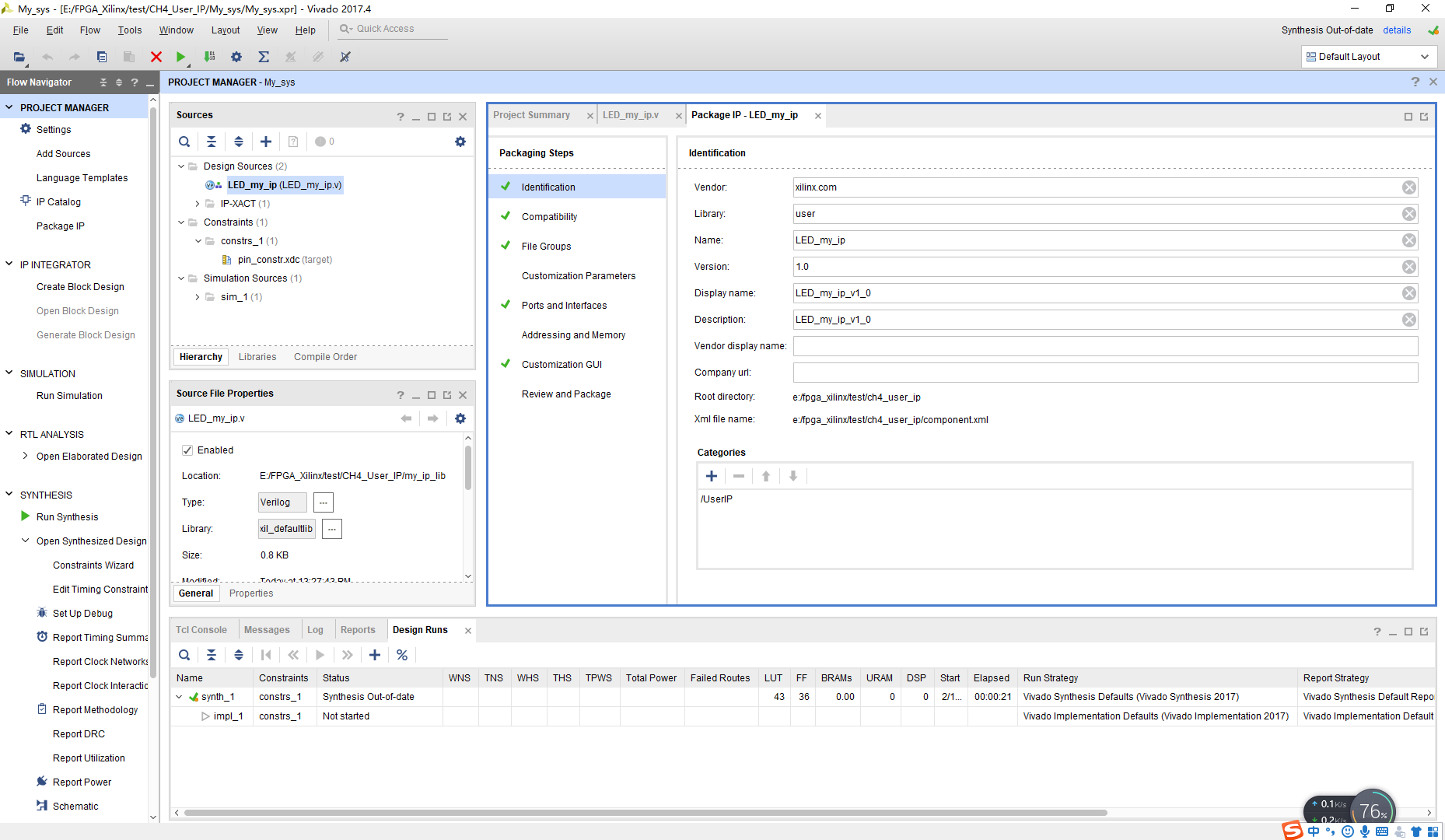

8.创建自定义IP

创建完成

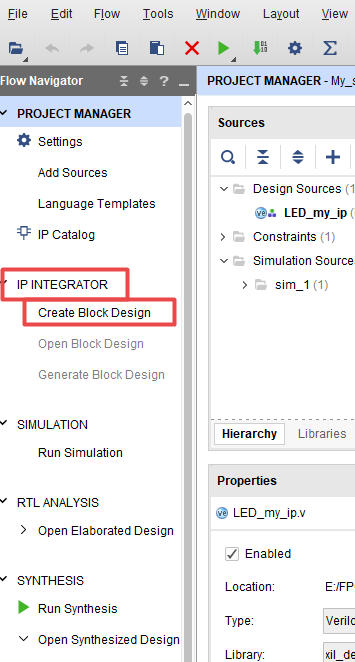

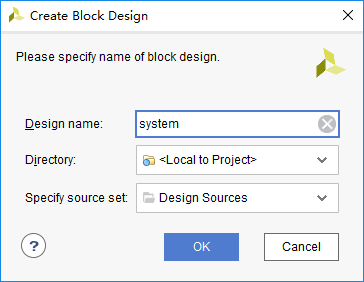

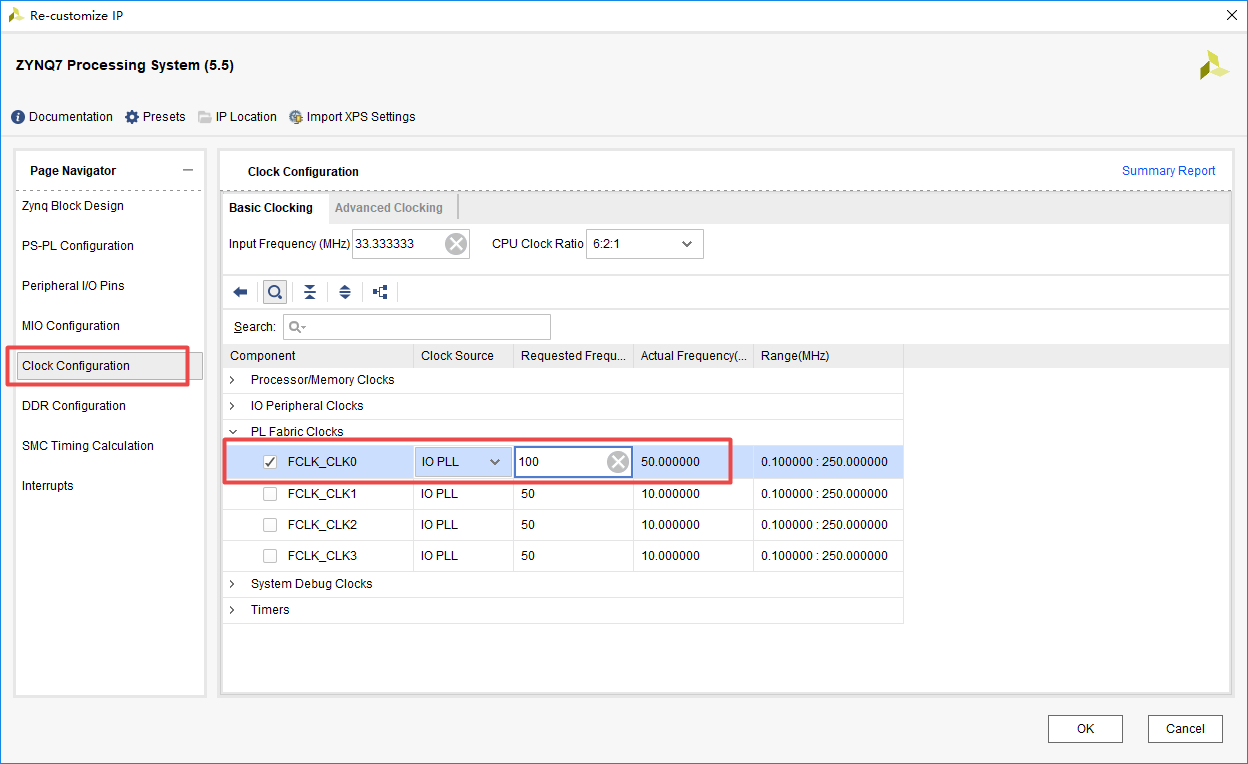

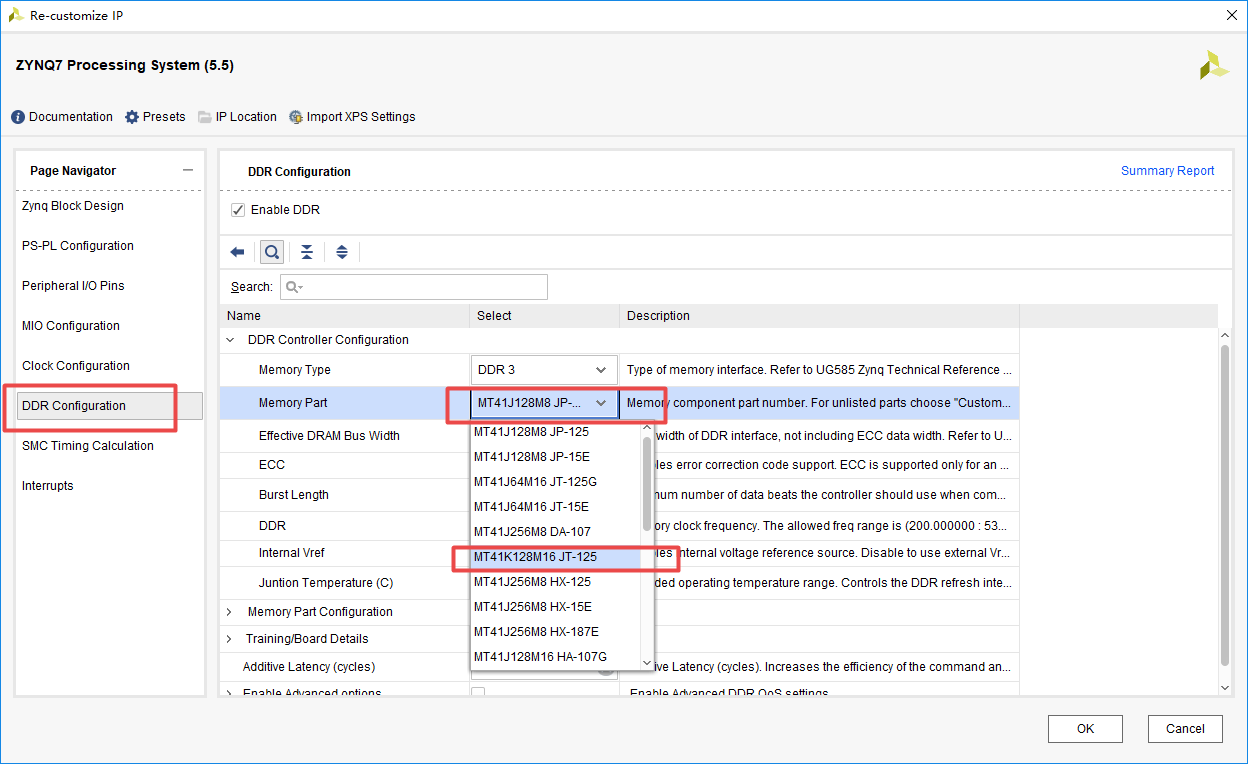

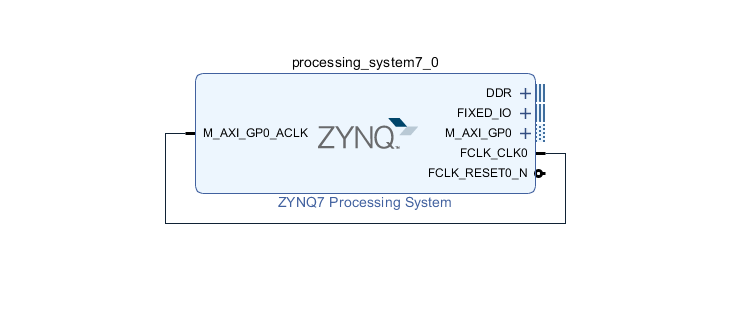

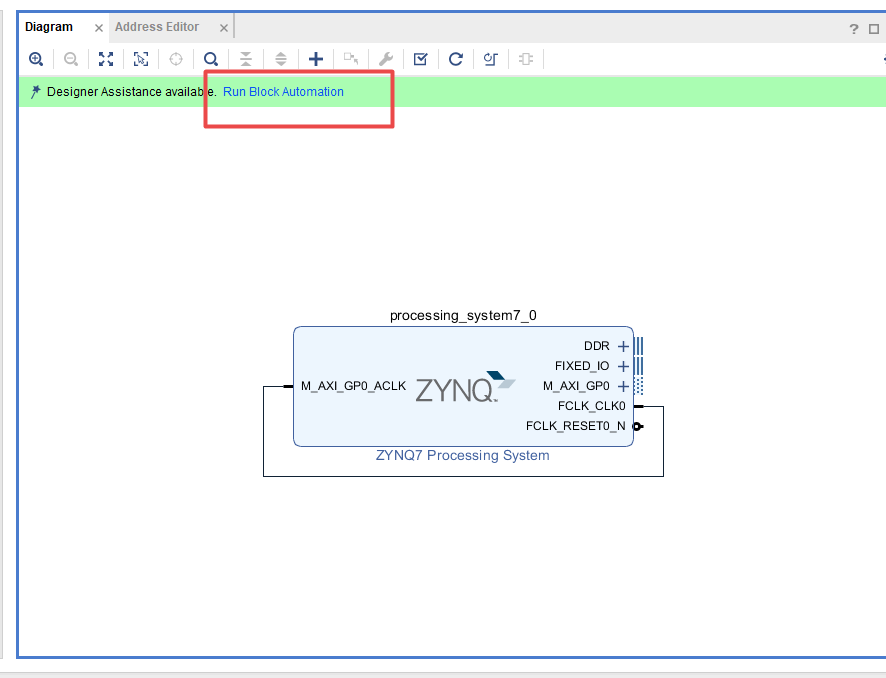

9.创建系统

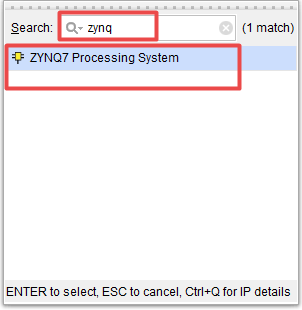

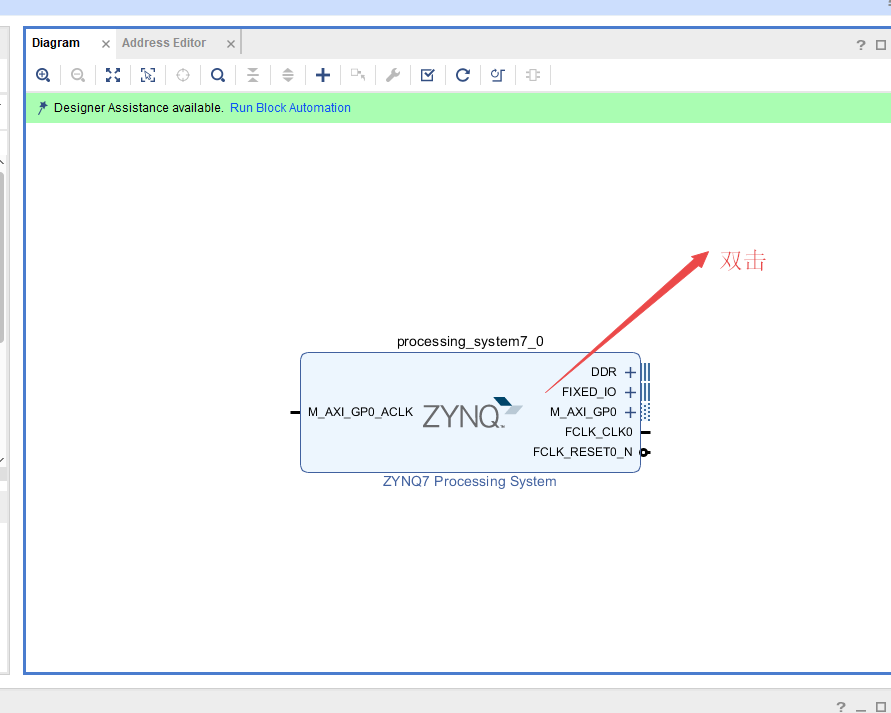

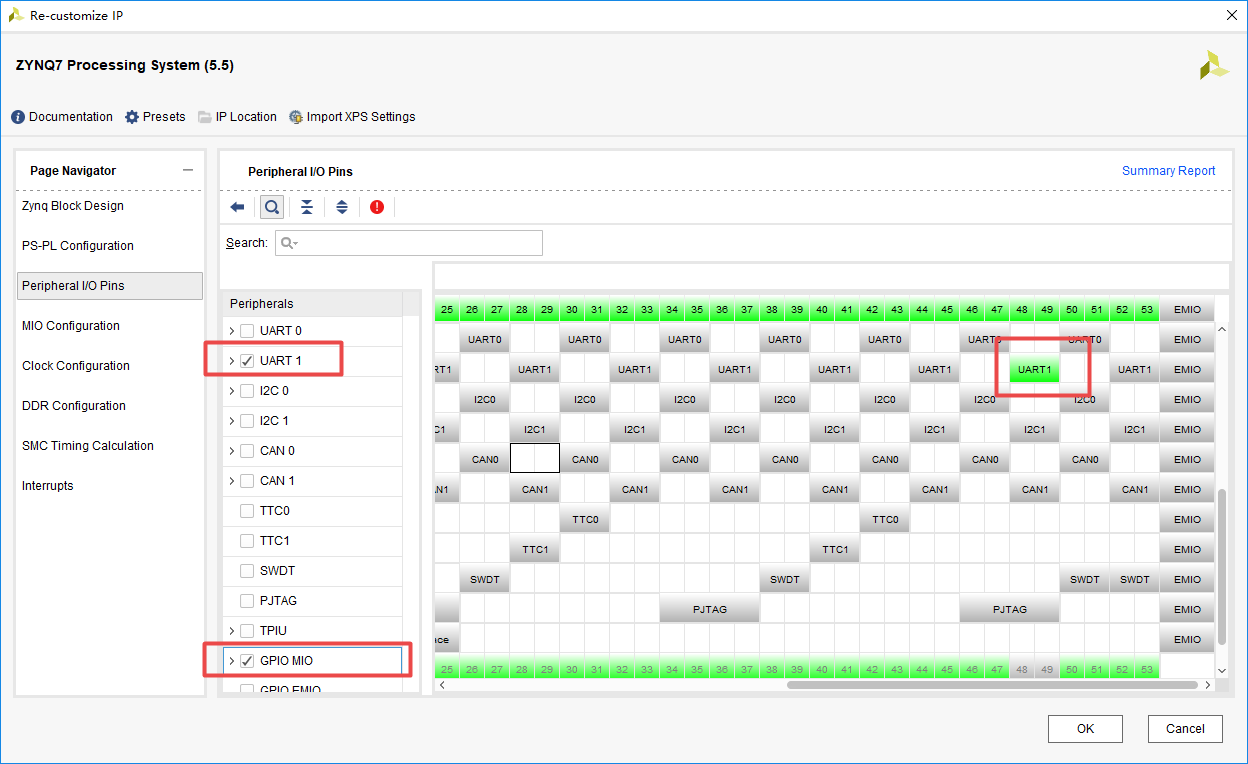

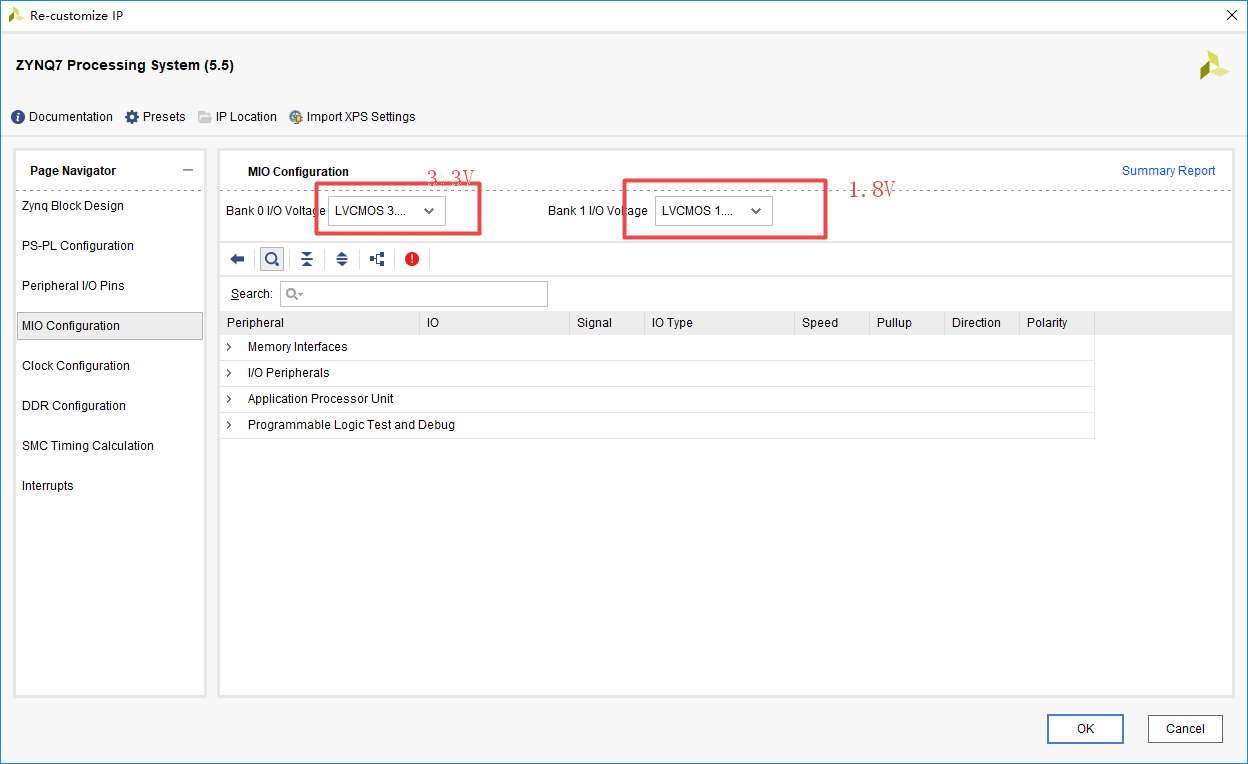

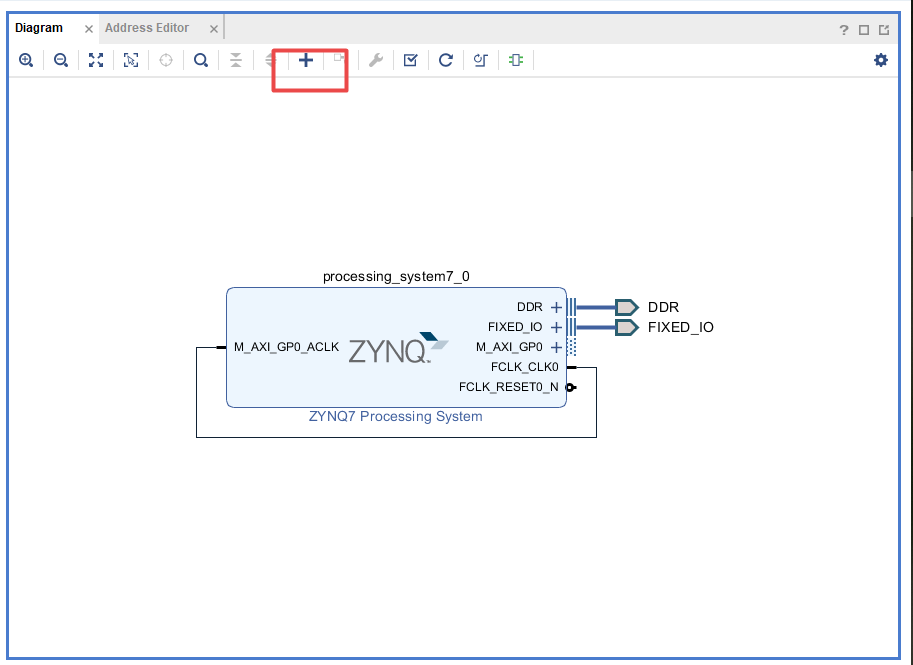

10.添加IP,首先是能够输出helloworld

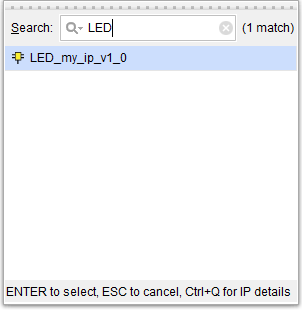

11.添加自定义IP

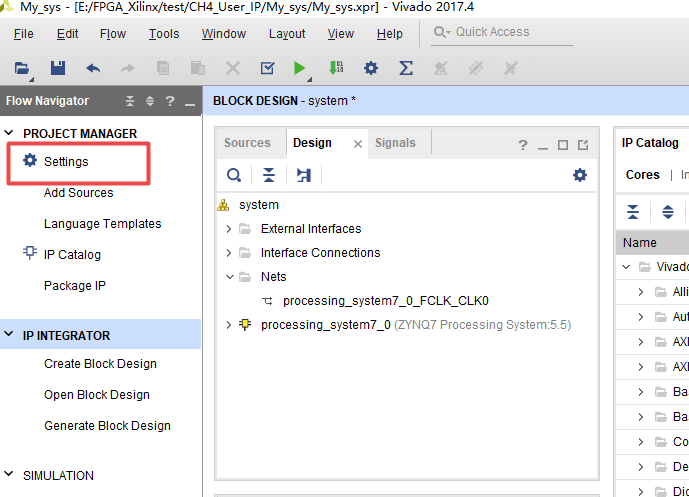

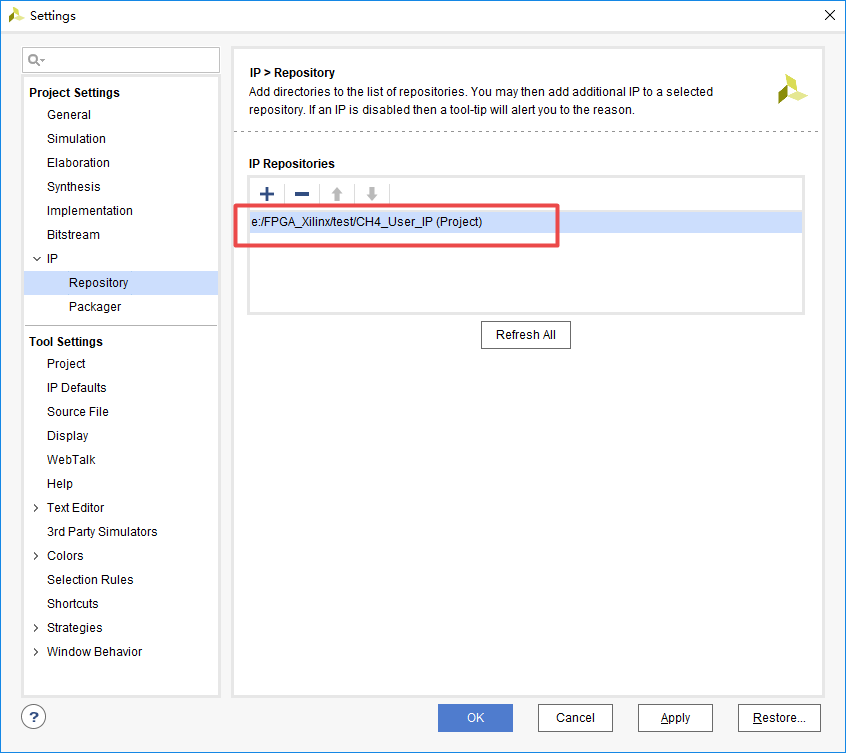

首先把文件添加到工程中

添加IP

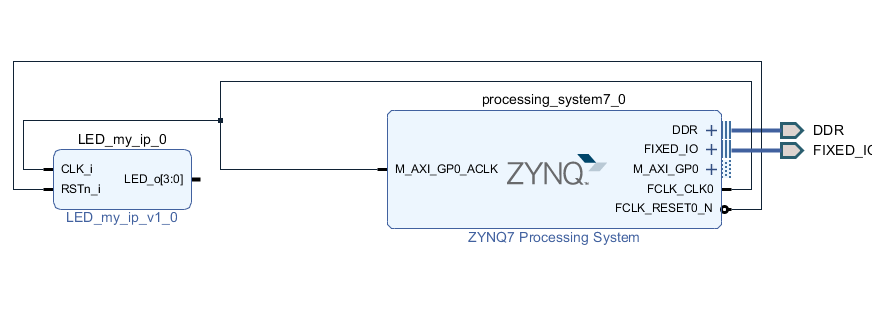

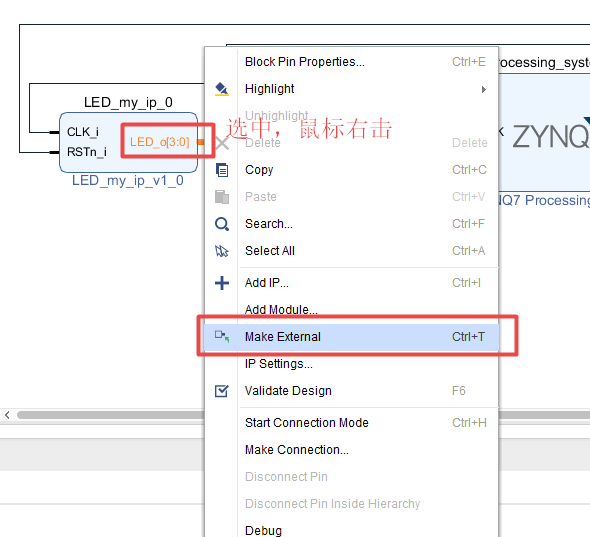

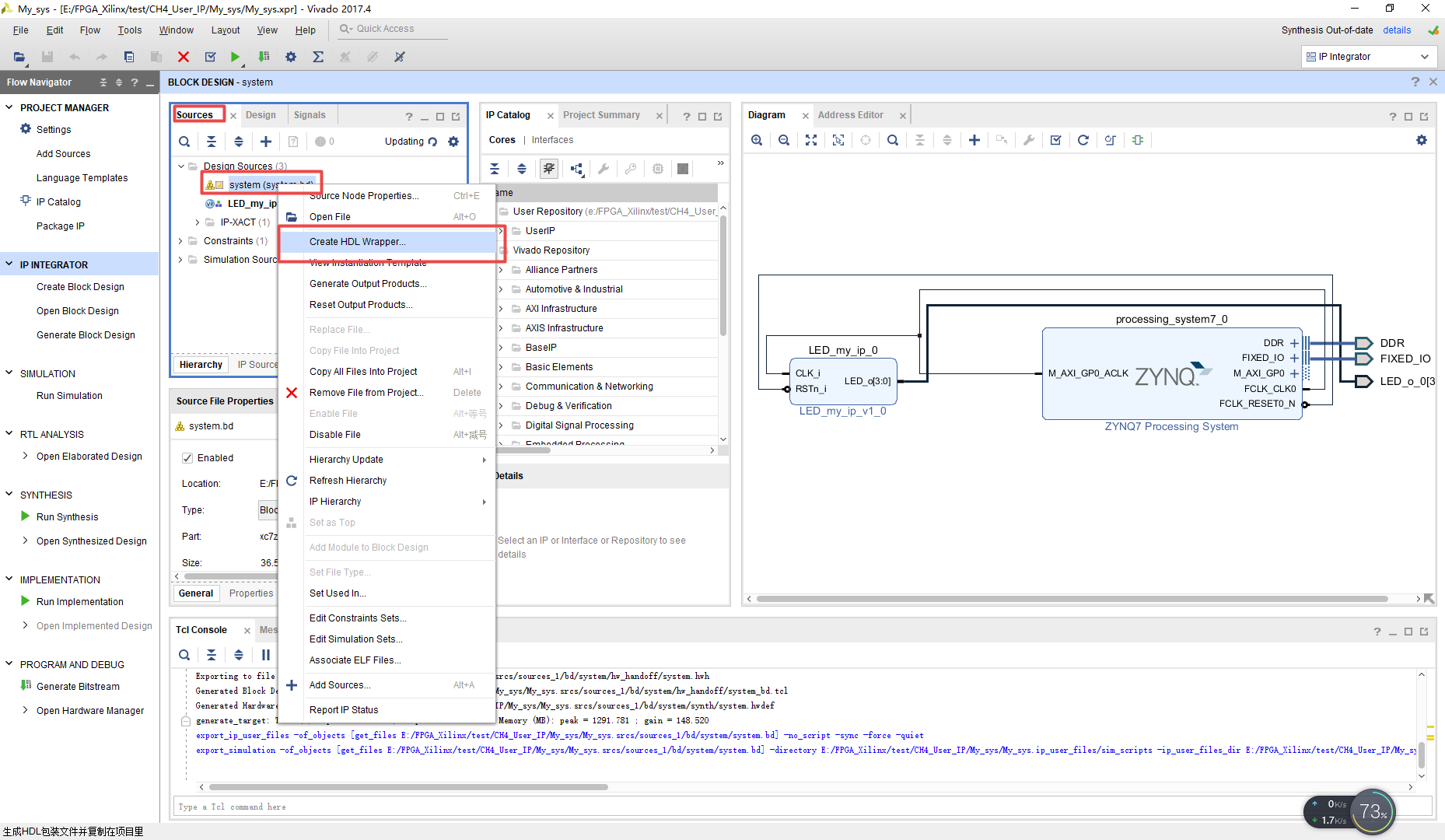

线连接

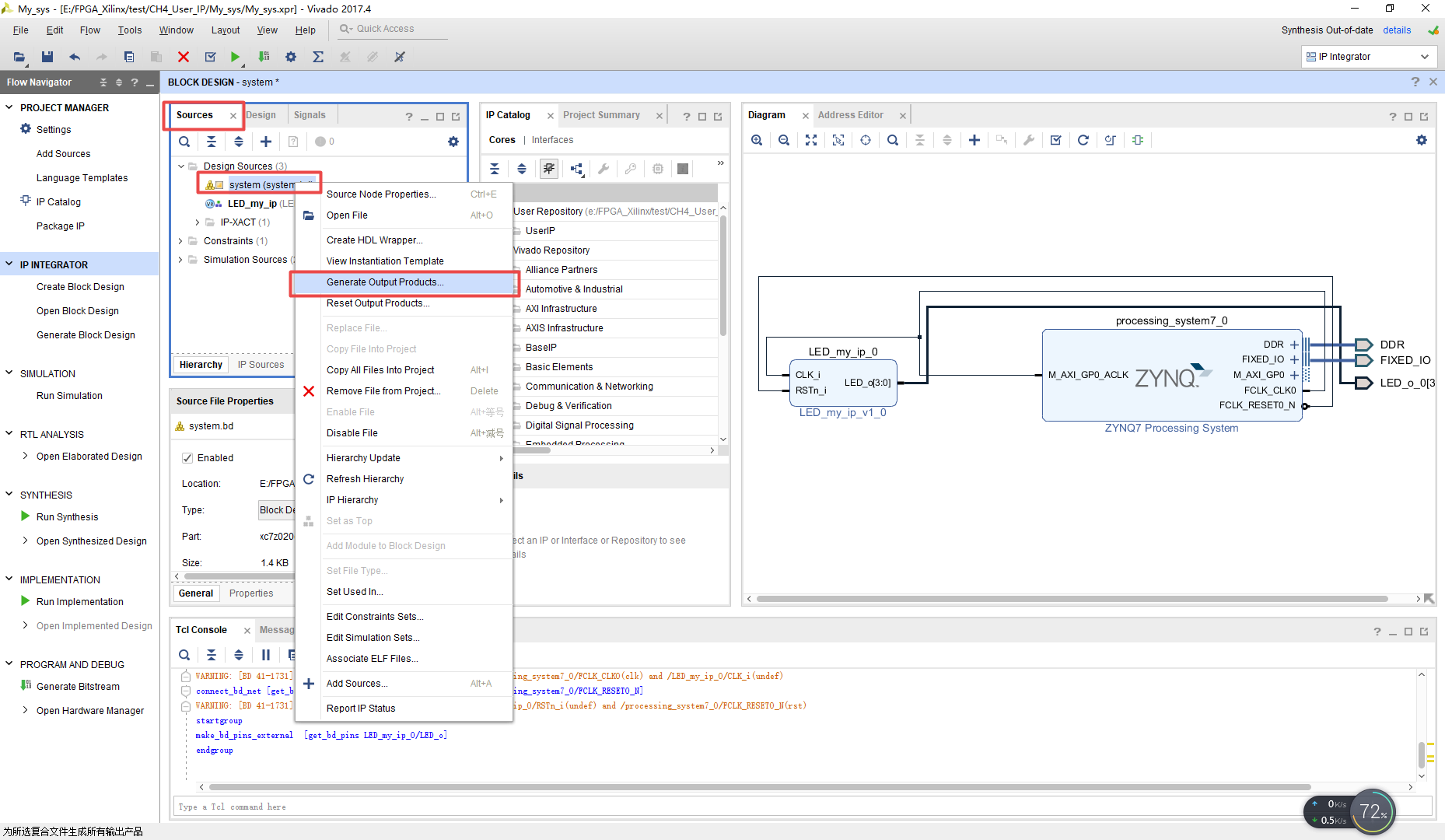

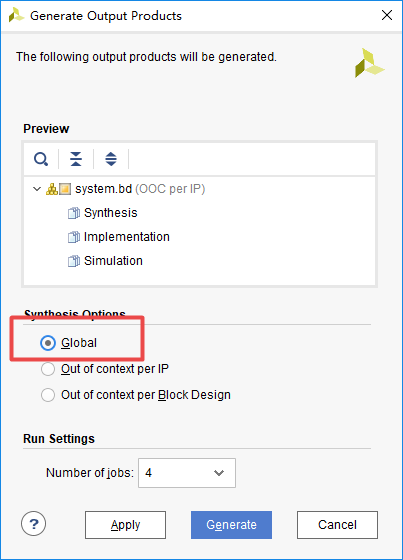

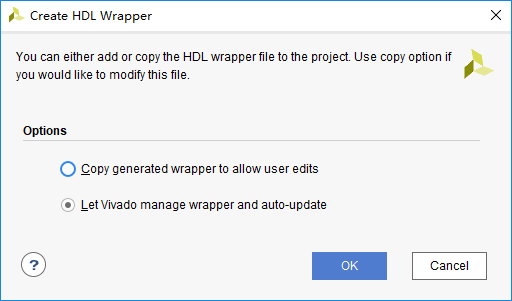

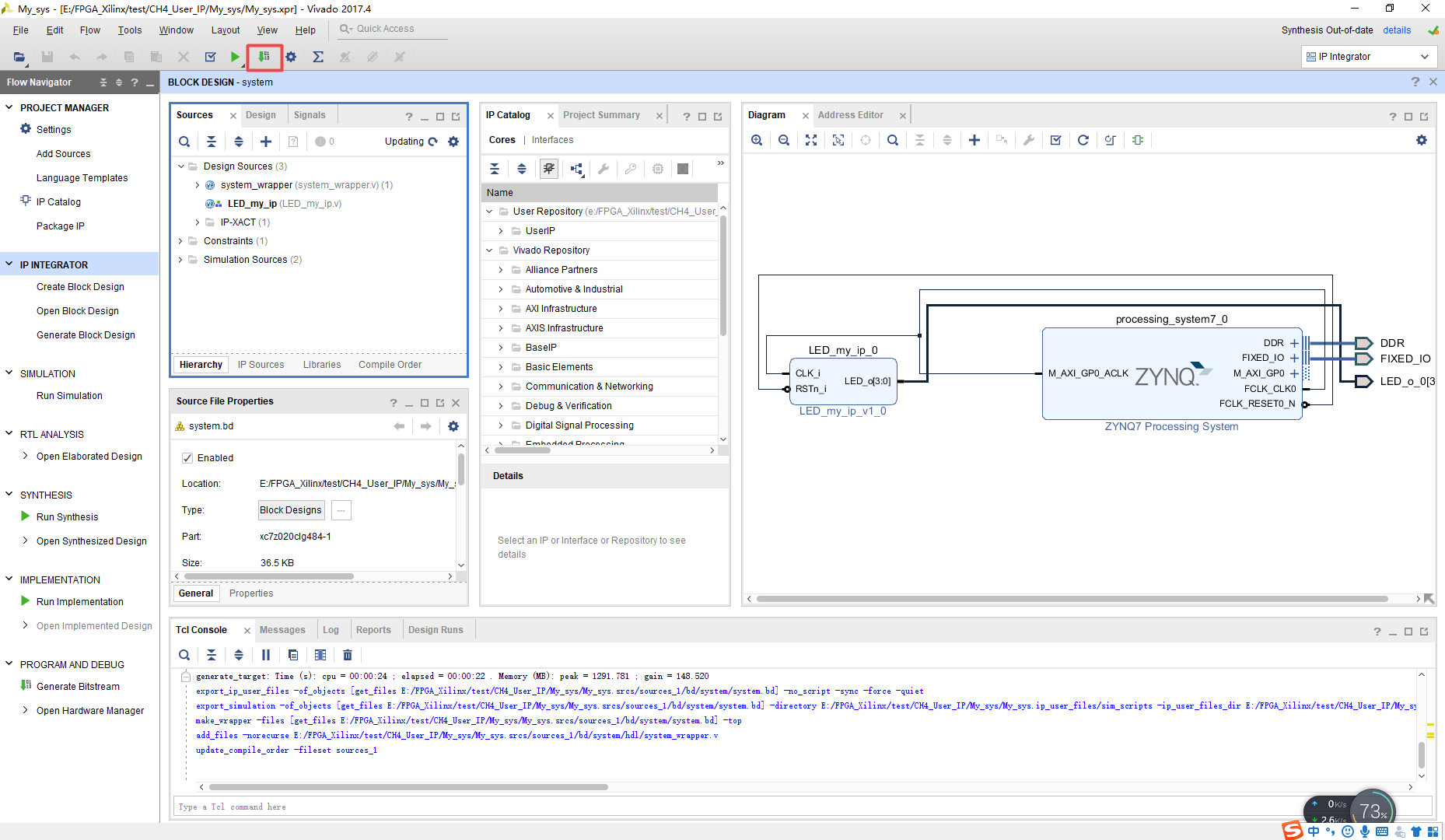

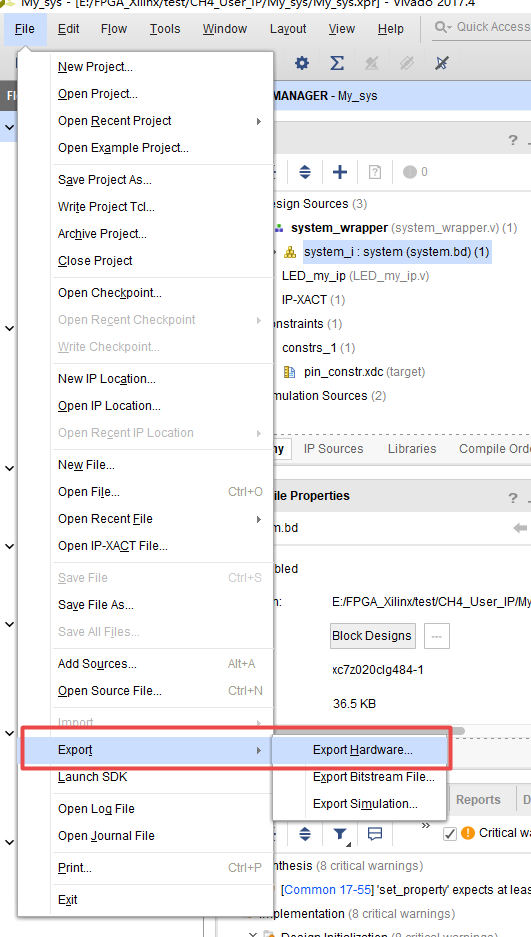

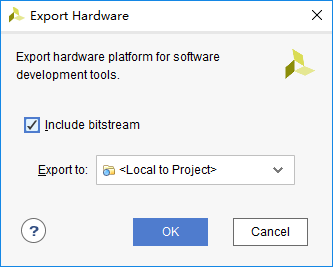

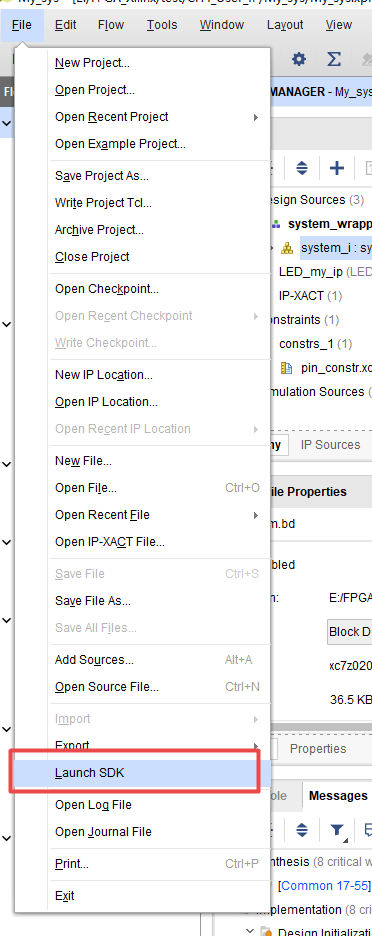

输出文件

生成bit文件

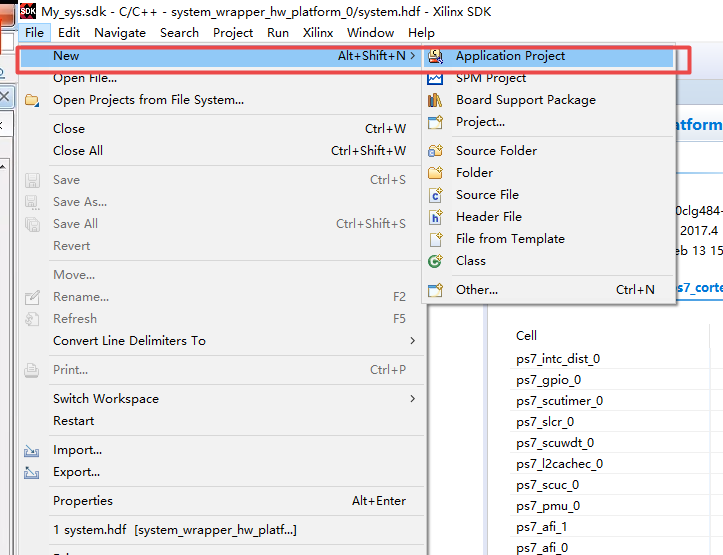

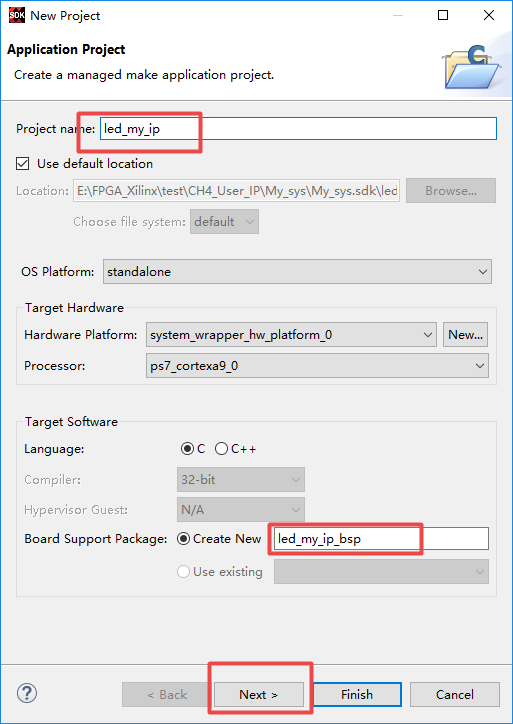

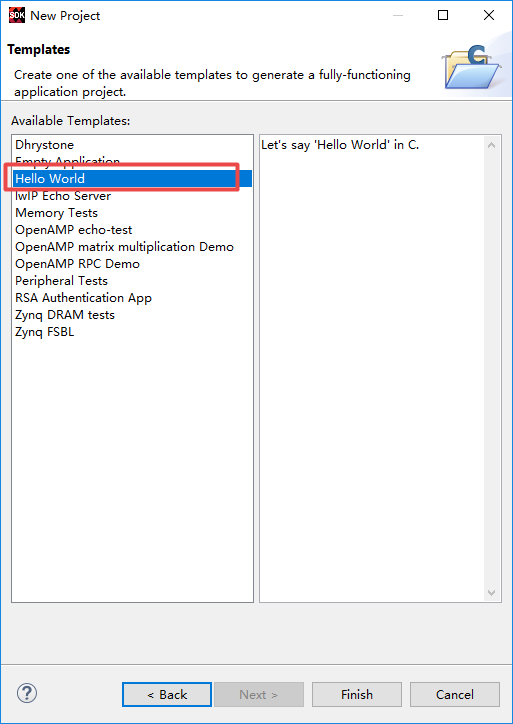

新建工程

最后下载到开发板中即可。