本节内容是sv里的剩余语法,task,function,automatic

一:procedural statement

1:新操作符

1) i++,++i,i--,--i 同c语言,但易出现race现象。

2) ==?,!=? 如:a==?b ,x与z只能出现在右侧,即b的值有x或者z

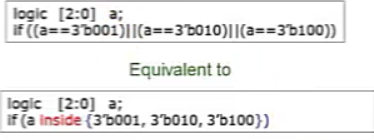

3) inside 用于值的范围

2:强制转换

1)数据类型强制转换

通过赋值的方式,例如

longint a,y;

real r;

y=a+longint(r);

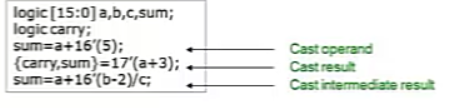

2)位宽强制转换

在要处理的数据前面加上要扩展位宽值,如16‘

3)符号位强制转换

将无符号数转化为有符号数,将有符号数转化为无符号数

signed'(expression) unsigned'(expression)

3: 循环

1)for

verilog中,循环体内的变量需要在循环体外声明,sv里,可在循环体内声明变量,这种变量是local的,在循环体外看不见。若在循环体内外同时声明同一变量,则互不干扰。

2)do while sv里增加的循环,verilog里没有。

3)case

增加unique,priority(优先级)选项;

二:function

1:主要概念

不消耗时间;不带时序,function里不能包含延时信息,@,wait等时间信息关键字;

由于task可以带时序,所以规定function不能调用task;

2:格式

function [range] function_name; //[range] 指返回值function_name的类型

parameters

input declaration

reg declaration

--code body --

endfunction

3: void function

不返回值;在verilog里,function一定返回值,且返回的值是function的名字。

三:task

1:基本概念

消耗时间,含有输入输出双向端口;可含delay,timing,event;

2:格式

task task_name

parameter

input dedclarations

output declarations

reg declaration

--code body--

endtask

3: task与function内部变量是静态变量,在不同地方对同一个变量赋值会产生race,需要注意

四:sv里task与function增加点

1:不需要加begin...end

2:添加return,直接退出函数

3: function增加了void function

function void fill_packet(input logic[63:0] data_in,output packet_t data_out);

data_out.data = data_in

endfunction

没有输出,通过输出变量data_out输出

4:在verilog里function只有input,没有output,返回值就是函数值;但在sv里,function增加了output,inout变量

5:参数方向类型缺省时,类型默认为logic,方向默认为input

6:引用ref

所谓引用传递,就如c++里面的指针,也就是变量的入口地址;只有automatic型task,function可以使用ref;

传值方式来传递参数,那么参数会被整体复制到其他地址,这样消耗一定的内存和操作时间;而用ref传值方式来传递参数,只是获得参数的入口地址,操作速度快,减少内存使用

可在ref数组前加const,使数组不变。

五:automatic

一般硬件里的所有对象都是静态的;在verilog-1995,如果在多个地方调用同一个任务,本地变量是共同而且静态分配的,为此,不同的进程相互访问同一个值。在verilog-2001中,可以通过使用automatic关键字,将任务,函数和模块声明为自动存储模式,这样,仿真器就能够对所有形式的参数和内部变量使用堆栈的形式来存储。