1. AMBA总线概述

AMBA2.0 以上版本都是基于单沿时钟、单向信号线的协议[1]。

现在市场上大部分的基于 AMBA 架构的 SoC 产品, 系统总线采用 AHB, 外部总线采用 APB。系统总线负责连接例如 ARM 嵌入式处理器、DMA 控制器、片上存储器或其他需要高带宽的元件。 外围总线则是用以连接系统的外围元件, 其协议相对来说较为简单, 而两种总线通过总线桥相连。 通过这种机制来减轻系统总线的负担。

根据intergration手册,Cortex-m0p和Cortex-m4均采用AMBA 3.0协议,Cortex-m0p只用了其中的AHB、AHB-Lite,对于GPIO自己定义了一个IO port(IOP),用户例化时可自行选择使用IOP还是AHB-Lite,Cortex-m4则分别支持AHB、AHB-Lite和APB协议。

2. AHB-Lite信号

AHB-Lite协议下的总线与设备间接口port定义:

input HCLK; input HRESETn; input [31:0] HADDR; //主发从收-地址总线 input [ 2:0] HBURST; input HMASTLOCK; input [ 3:0] HPROT; input [ 2:0] HSIZE; input [ 1:0] HTRANS; input [31:0] HWDATA; //主发从收-写数据 input HWRITE; //主发从收-写命令 input HSEL; //多路器发从设备收-从机选则 input HREADY; //多路器发主设备收-总线ready output [31:0] HRDATA; //从发主收-读数据 output HREADYOUT; //从发主收或多路器收-从设备ready output HRESP; //从发主收:0-OKAY;1-ERROR

不管是m0+还是m4,访问GPIO都是用的AMBA3.0 AHB Lite协议,使用的总线信号如下:

HSIZE[1] HSIZE[0] 单次传输的数据宽度

0 0 8bit

0 1 16bit

1 0 32bit

当HSIZE[1:0] ={ 00 }, 8bit访问的情况:

HADDR[1] HADDR[0] 字节地址选择 对应屏蔽码

0 0 0 0001

0 1 1 0010

1 0 2 0100

1 1 3 1000

当HSIZE[1:0] ={ 01 }, 16bit访问的情况:

HADDR[1] HADDR[0] 读写地址选择 对应屏蔽码

0 0 0 0011

0 1 X(0) 0011

1 0 2 1100

1 1 X(0) 1100

当HSIZE[1:0] ={ 11 }, 32bit访问的情况:

HADDR[1] HADDR[0] 读写地址选择 对应屏蔽码

1 0 0 1111

0 1 X(0) 1111

1 0 X(0) 1111

1 1 X(0) 1111

HTRANS[1] HTRANS[0] 总线状态 – 只有当HTRANS[1]=1时才是一次有效传输

0 0 空闲

0 1 忙

1 0 传输-非连续传输

1 1 传输-连续传输(为突发传输而设,地址自增,GPIO访问不用)

HSEL: 设备选择,为1表示选中此设备

HWRITE: 总线写命令,为1表示写数据,为0表示读数据

HREADY: 总线准备好(表示总线给设备的命令、地址或数据都是稳定的状态,设备可以取走了)

HWDATA: 总线给到设备的数据

HRDATA:总线从设备读走的数据

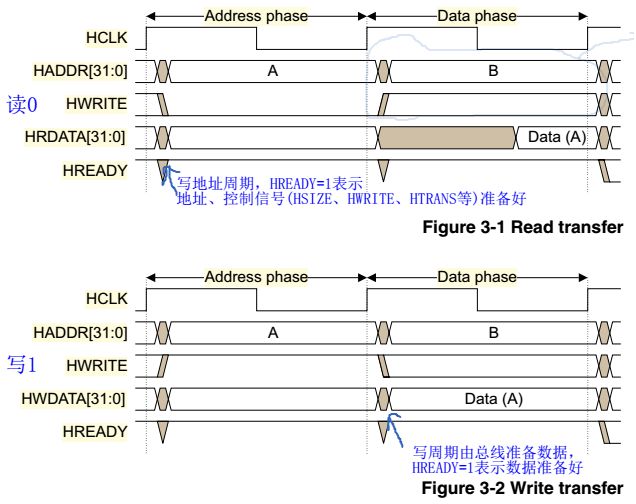

3.AHB Lite时序

一次基本的总线传输需要两个时钟(cm4手册表示LDR、STB指令可通过总线流水的方式一拍完成,cm0+没这个注释,但提供了一个用于一拍访问外设的接口IOP),第一拍写地址,第二拍读(或写)数据:

4. Examples

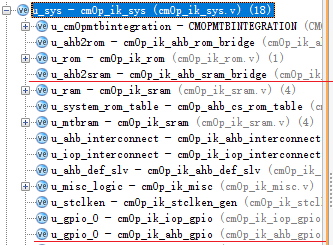

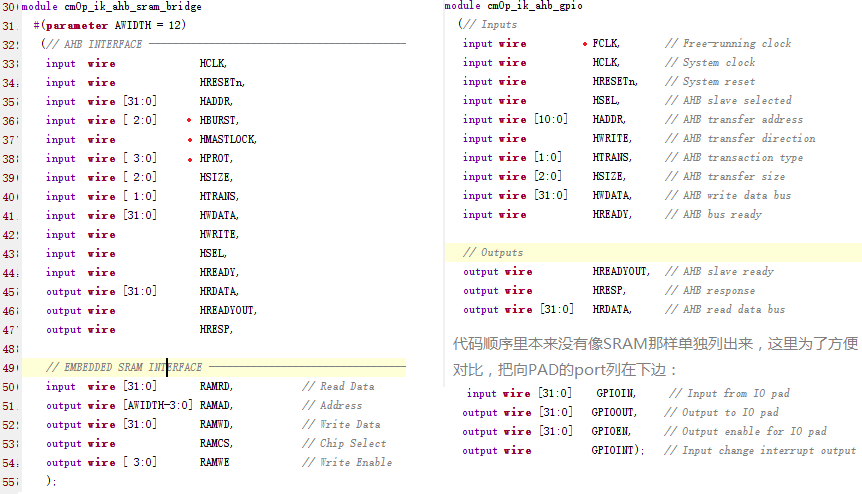

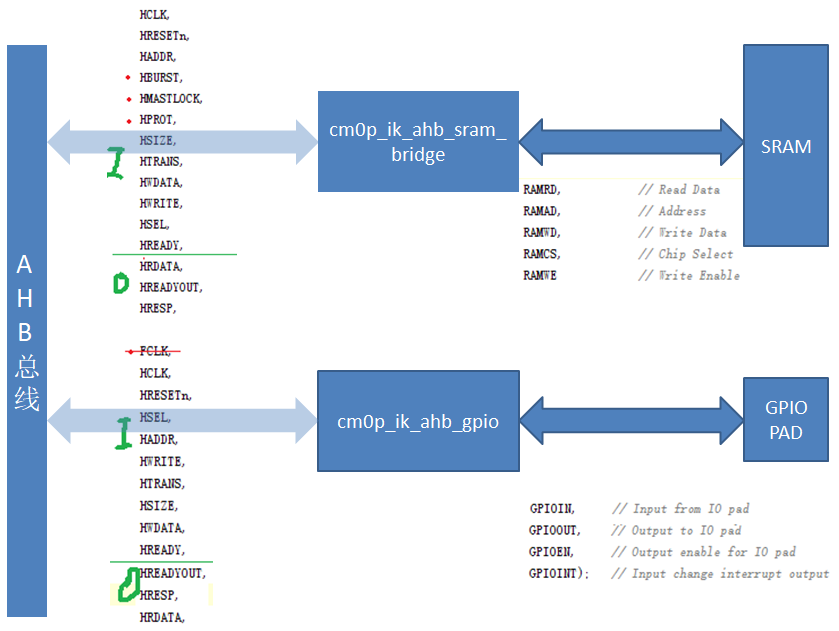

以Cortex-m0p的SRAM接口、GPIO接口为例(Cortex-m4里这两个接口实现方式完全一样):

接口信号:

PowerPoint画了一张丑到不忍直视的接口示意:

【1】蒋周良.AMBA 总线新一代标准 AXI 分析和应用