在上一篇中详细的介绍了怎样创建原理图工程,这篇同样使用原理图工程新建一个多路选择器,目的是学习使用图形输入的仿真工具输入仿真激励。

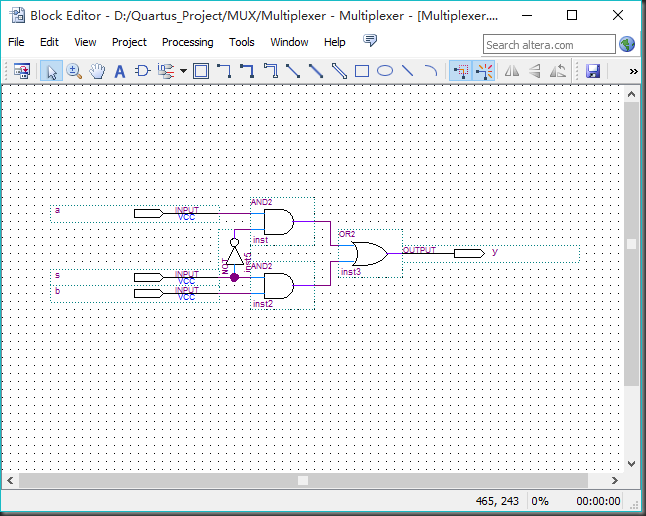

新建工程,并绘制以下的原理图。

编译项目,会多出一个警告: Critical Warning (169085): No exact pin location assignment(s) for 4 pins of 4 total pins,其大致意思是在目标器件上有四个引脚没有被分配,由于这次我们只用到仿真,不需要下载文件到板子上,因此没有必要去分配管脚。

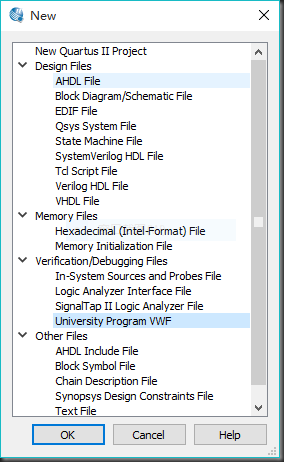

编译成功后新建一个 University Program VWF (仿真波形文件),

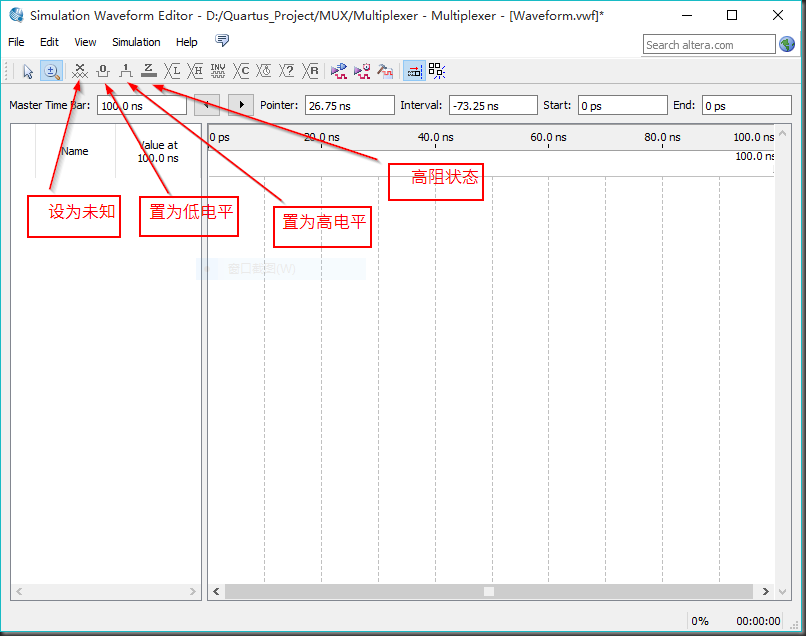

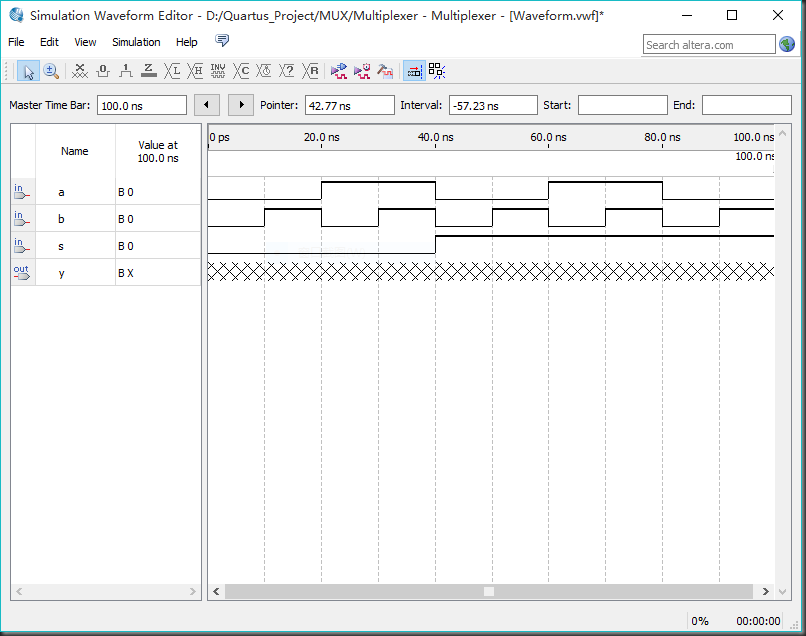

双击主界面 Project Navigator Files 标签下的 waveform.vwf 文件打开仿真波形文件编辑器,如下:

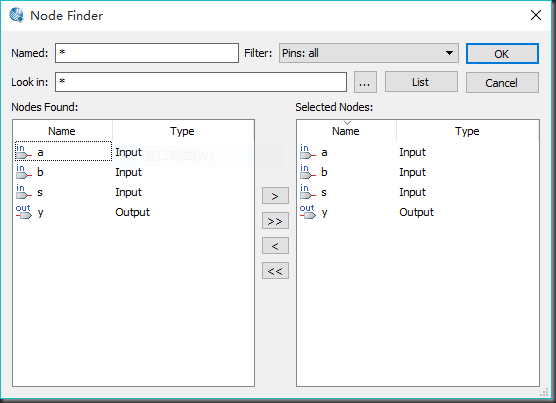

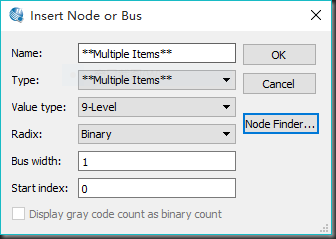

接下来在仿真波形文件编辑器中添加管脚,依次点击 Edit –> Insert –> Insert Node or Bus,再点击下图中的 Node Finder...

点击 List,图为仿真引脚的选择工具,这里我们需要添加所有的引脚。完成后点 OK。

再点一次 OK

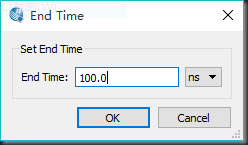

完成引脚添加工作,接下来在 Edit --> Set End Time 中设定仿真时间,由于该编辑器的一个格子是 10 ns,这里我们设为 100 ns。

选择需要修改的时间段,修改为需要的高低电平,修改到下面这个样子就可以了(*^__^*)。

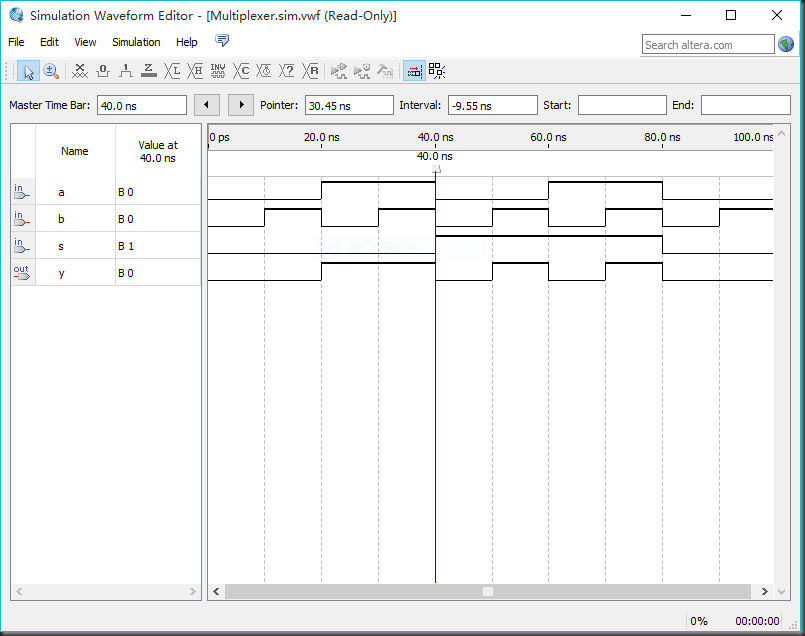

接下来点击 Simulation –> Run Function Simulator 进行逻辑仿真。仿真结果如下:

可以看到,当 s = 0 时, y = a;当 s = 1 时,y = b。

仿真验证了我们的设计是正确的。O(∩_∩)O 同样还可以使用 verilog 语言描述一个多路选择器,verilog 代码如下,各位可以试试。

module mymux ( input wire a, //这里是逗号 input wire b, input wire s, output reg y //这里没有逗号 ); //这里是分号 //**************************************************// always @ (*) //敏感信号列表,初学者打星号就可以了 begin if(s==1'b0) //两个等号表示判断是否相等 y = a; else y = b; end //*************************************************// endmodule