时钟脉冲信号

按一定的电压幅度,一定的时间间隔连续发出的脉冲信号叫做时钟脉冲信号。用于给处理器和其他硬件提供时钟度量。

时钟脉冲频率

在单位时间内产生的时钟脉冲的个数叫做时间脉冲频率

时钟源分类

1.晶振:又称晶体振荡器,通过石英晶体切割、加电极、通电后会产生固定的机械震荡。优点是结构简单、噪声低,缺点是生产成本高。

2.PLL:锁相环,通过外部晶振和锁相环电路来提高晶振的频率。

时钟体系

1.晶振频率是多少?

2.有多少个PLL?

3.PLL产生出了哪些时钟?(ARM核使用的是哪个时钟)

4.产生出来的时钟用来做什么?

5.在datasheet中的CLOCK & POWER MANAGEMENT中可以相关描述

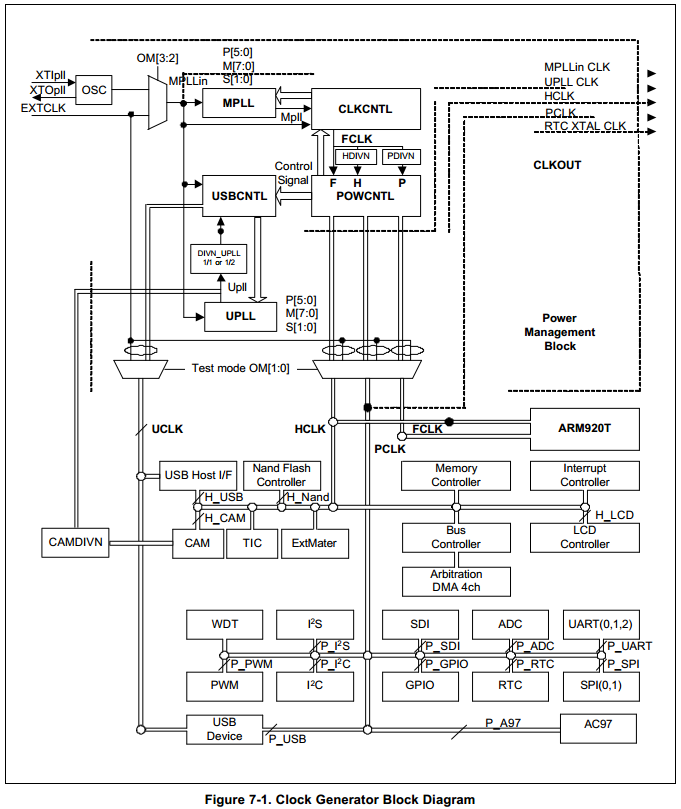

2440时钟体系

1.晶振频率是12MHz

2.MPLL,UPLL

3.MPLL产生出来FCLK、HCLK、PCLK;UPLL产生出来UCLK

|

时钟 |

应用场合 |

应用举例 |

所属PLL |

|

FCLK |

处理器 |

ARM9 |

MPLL |

|

HCLK |

AHB总线 |

LCD,DMA |

MPLL |

|

PCLK |

APB总线 |

UART,GPIO |

MPLL |

|

UCLK |

USB总线 |

USB |

UPLL |

6410时钟体系

1.晶振是12MHz

2.APLL,MPLL,EPLL

3.APLL产生出来ARMCLK;MPLL产生出来HCLK、PCLK;EPLL产生出来SCLK

|

时钟 |

应用场合 |

应用举例 |

所属PLL |

|

ACLK |

处理器 |

ARM11 |

APLL |

|

HCLK |

AHB总线 |

LCD,DMA |

MPLL |

|

PCLK |

APB总线 |

UART,GPIO |

MPLL |

|

SCLK |

USB总线 |

USB |

EPLL |

210时钟体系

1.晶振是24MHz

2.APLL,MPLL,EPLL,VPLL

|

时钟体系 |

所属时钟 |

应用举例 |

锁相环 |

|

MSYS |

ARMCLK HCLK_MSYS PCLK_SYS |

ARM核 内存控制器 中断 |

APLL |

|

DSYS |

HCLK_DSYS PCLK_DSYS |

显示相关部件如FIMC |

MPLL |

|

PSYS |

HCLK_PSYS CLK_DPM |

外设,如UART,I2C |

EPLL |

|

|

视频相关 |

|

VPLL |

思维导图设计

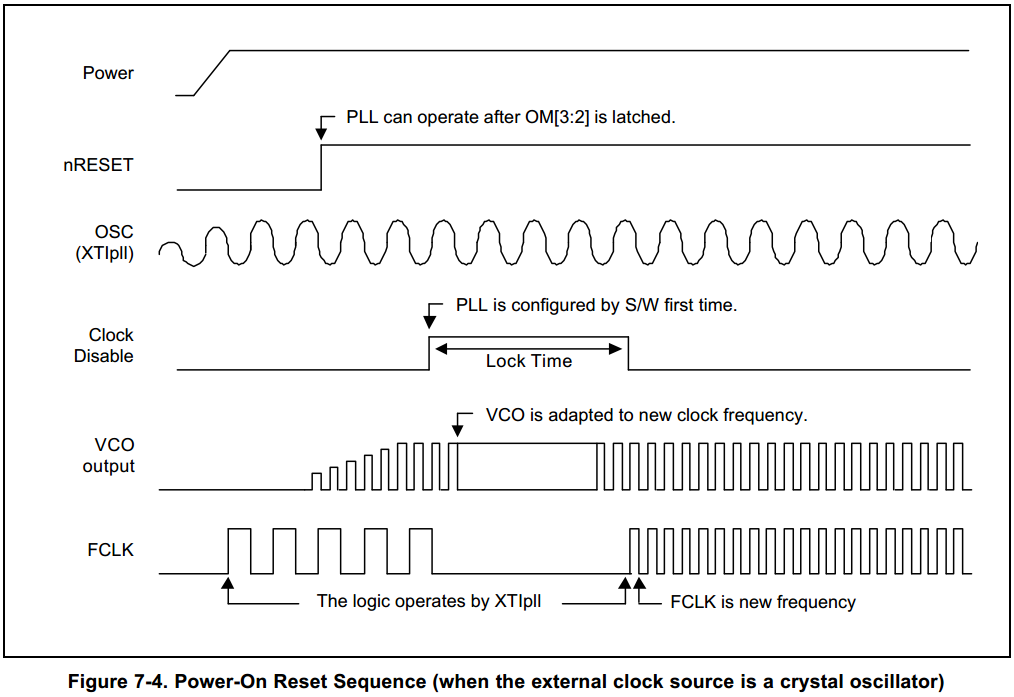

1.上电之后ARM核按照晶振频率在工作

2.当PLL配置完成是会进入Lock Time,处理器停止工作,然后以新的频率开始工作。

3.时钟初始化软件需要完成的工作:

3.1.配置Lock Time;

3.2.设置分频系数(用于FCLK来配置HCLK和PCLK);

3.3.如果HDIVN不等于0,需要设置CPU从快速模式到异步模式。FCLK是核的频率,HCLK是总线的频率,当核的频率和总线的频率不相等的时候需要设置CPU到异步工作模式。

3.4.配置FCLK

代码编写

1.找到设置lock time的寄存器LOCKTIME(0x4C000000),一般使用默认值,所以不需要去设置

2.设置PLL需要去设置MPLLCON(0x4C000004)中的MDIV=127 PDIV=2 SDIV=1

3.设置分频系数一定要在datasheet中对应的表里面。可以参考uboot中的分频系数来设置FCLK:HCLK:PCLK=1:4:8 HDIVN=2 PDIVN=1。在CLKDIVN(0x4C000014)寄存器中是用来设置HDIVN和PDIVN的

4.设置异步工作模式需要在ARM核手册中找到CP15的R1寄存器的iA和nF位,并设置为1

时钟设置总结(可以参考芯片手册和uboot代码)

1.设置PLL系数

2.设置选择器

3.设置分频系数

4.设置异步模式

/* *名称:init_sysclk *功能:初始化系统时钟 */ init_sysclk: //设置PLL系数 ldr r0, =MPLLCON ldr r1, =MPLLCON_VAL str r1, [r0] //设置分频系数 ldr r0, =CLKDIVN ldr r1, =CLKDIVN_VAL str r1, [r0] //设置异步模式 mrc p15, 0, r0, c1, c0, 0 orr r0, r0, #0xC0000000 //设置iA:1 iF:1 mcr p15, 0, r0, c1, c0, 0 mov pc, lr