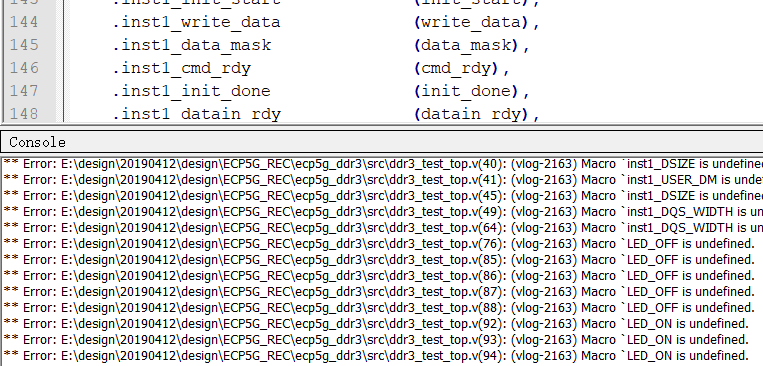

DS的时间很珍贵的 ,尤其是过了32岁以后,一身的病,扛不住996的制度。为了增加速度,只能想办法怎么在fpga工作上面降低时间。你有心思点来点去的GUI的界面。还不如用一个脚本完全做完。notepad++ 是DS最爱的verilog的编辑器,这个编辑器好用在,傻瓜一类gui节目。其实VScode一样可以用的,Vim在linux环境下更牛逼用。notepad++ 不能只是写写代码。然后切换modelsim 或者 quartus和xilinx 检查语法,这两个软件检查语法太垃圾了。检查语法,要你半天时间,代码只有1000行的,你一天下来,又得996了。

首先说明下,notepad++ 需要32位版本

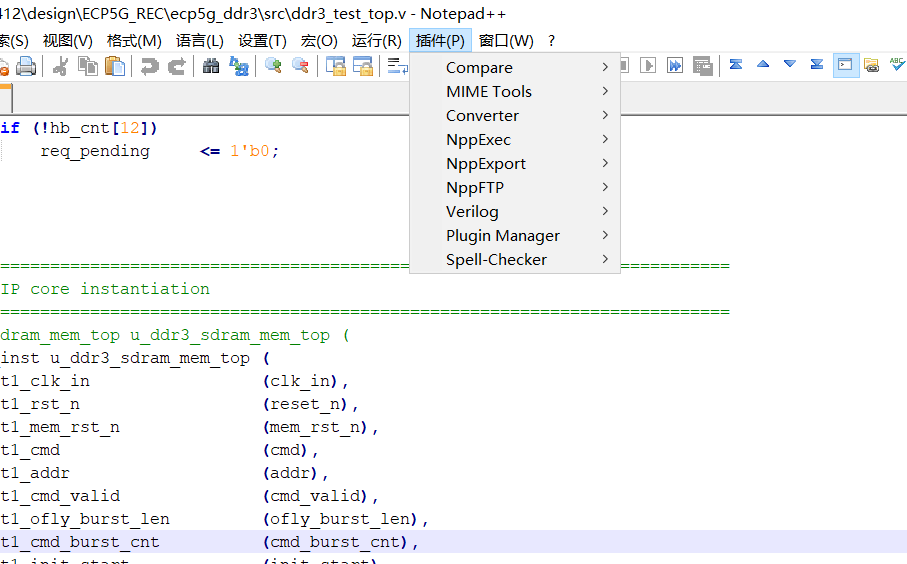

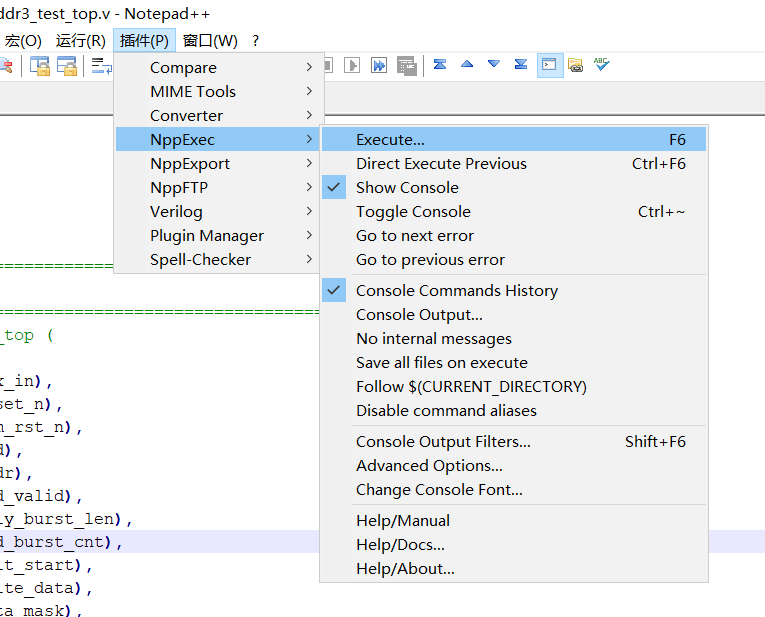

NPP EXEC是运行cmd的程序,能在输出代码 能在界面显示结果。

在Execute 输入命令 cmd /k cd "$(CURRENT_DIRECTORY)" & vlog.exe "$(FULL_CURRENT_PATH)" & ECHO. & EXIT

这些每次写完代码,就可以按F6检查verlog语法。

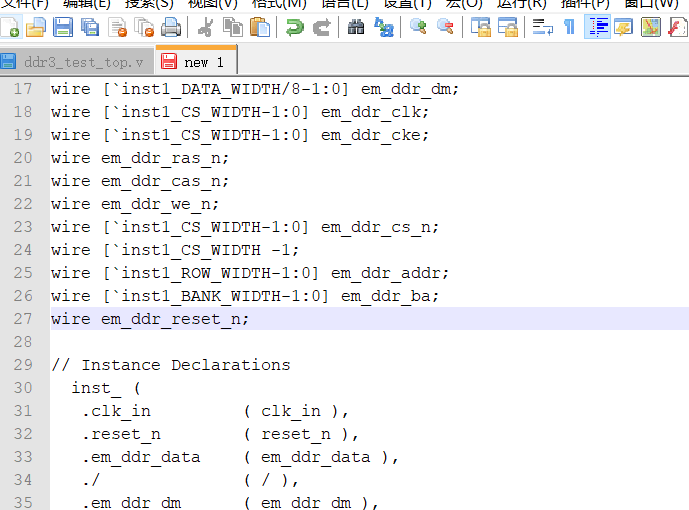

还有一个verilog插件用来自动生成测试脚本的。

但是特别是create tedt bench很实用。如果叫DS花一天时间写一千信号测试接口很痛苦的。不过要用这个命令,需要对着模块,使用shift+ctrl+c的功能,然后点击这个create test bench功能。