Description

Attached to this Answer Record is an Example Design for using the AXI DMA in polled mode to transfer data to memory.

Solution

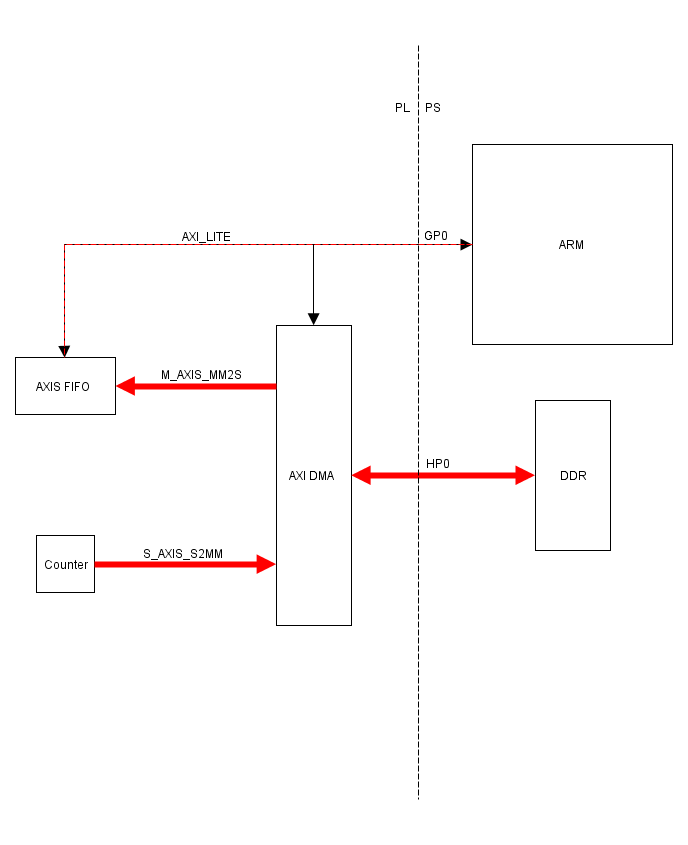

This design targets Zynq devices and uses a simple counter to drive the S2MM channel of the AXI DMA.

Counter data is sent into and then read out of memory, and is finally sent out of the MM2S channel to an AXI Streaming FIFO.

The data received by the AXI Streaming FIFO is verified against the counter data.

The ARM controls DMA transfers via GP ports by accessing the AXI DMA core through its AXI Lite interface.

It uses simple polling of the status register to manage DMA transfers.

For more details about the design, refer to the dma_ex_polled/doc directory.

The current version of this design was created in Vivado 2015.1.

https://www.xilinx.com/support/answers/57561.html