本次设计的工具和源码在:http://download.csdn.net/detail/noticeable/9914766

课程目的:调用quartus II提供的rom(read only memory)进行系统项目设计

实验现象:将一组固定的波形数据以MIF的格式存储于fpga中使用IP核构建的片上ROM中,开发板上电后,系统从ROM 中读取数据,并将数据通过I/O口输出,使用signal TAP II取I/O口输出的数据,即可得到三角波形;并通过quartus II提供的in system memory content editor 工具在线更改ROM 中的数据,然后再次通过signal TAP II将更改后的波形读取出来。

知识点:1、mif文件的生成方法2、ROM IP核的使用。3、In-system memory content editor 内存查看工具的使用。4、signalTap II 调试工具的简单使用

开发流程:

首先,自己创建对应波形的mif文件,以便后面调用rom IP核的时候使用

可以自己创建一个文本,然后在文件中输入自己想自己想要显示的波形的数据再保存,但是这样设计使得设计过于繁琐,这里推荐使用软件mif_maker2010直接生成.mif文件(软件在源码压缩包中)

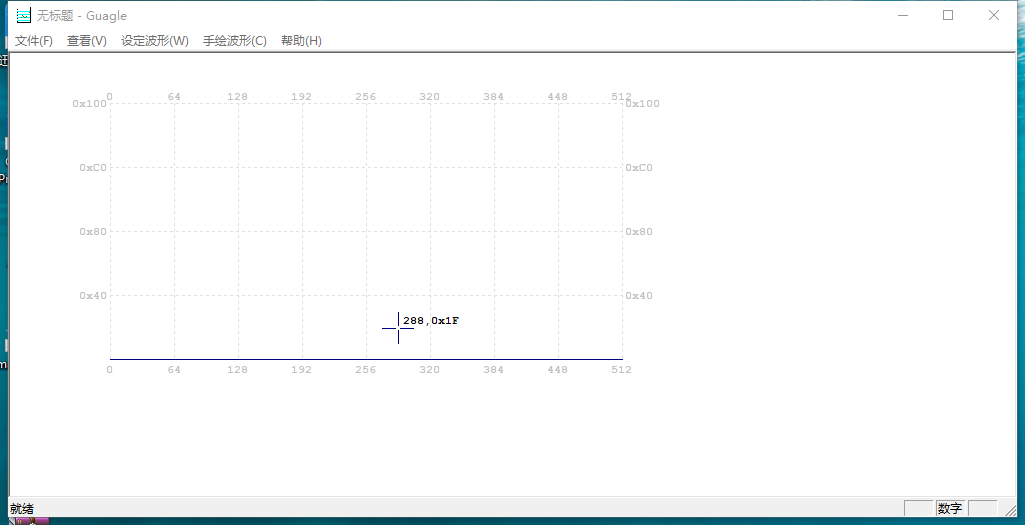

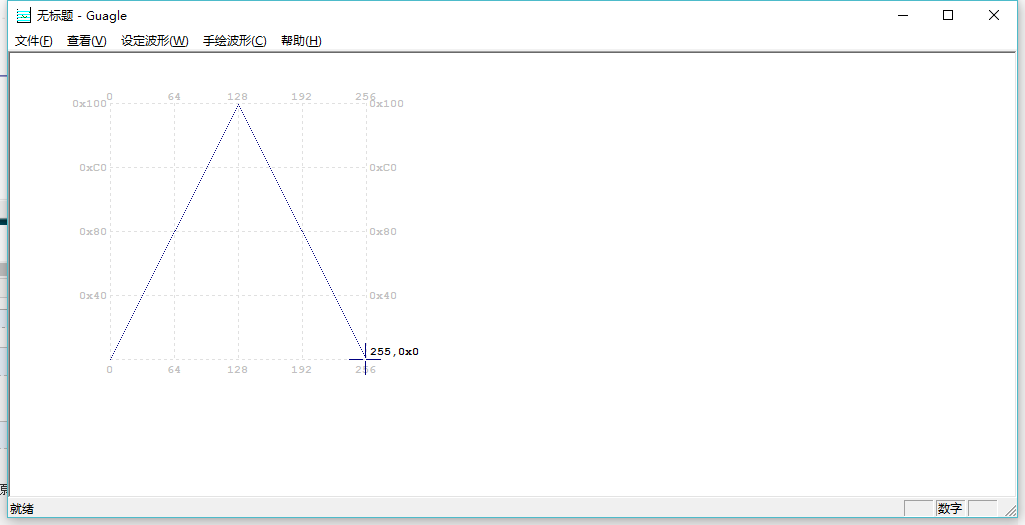

打开软件

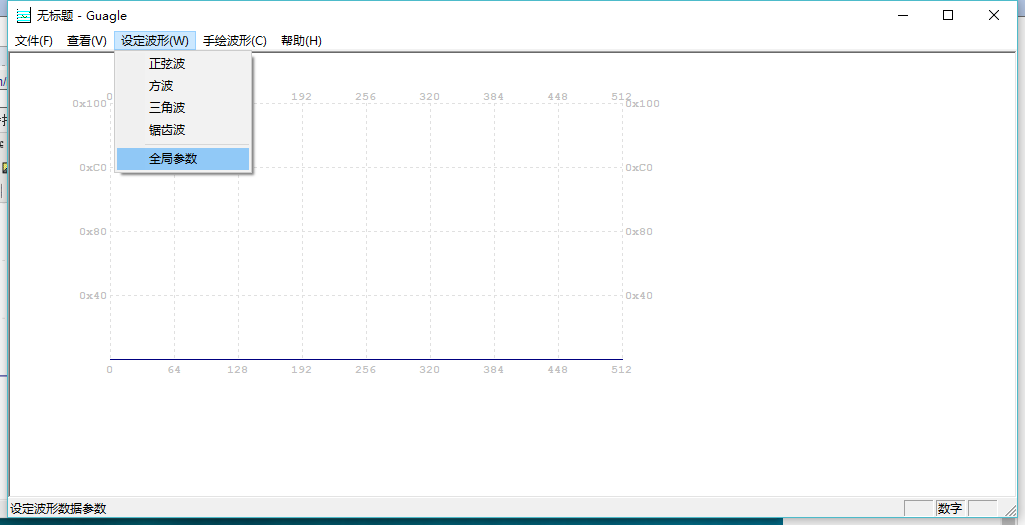

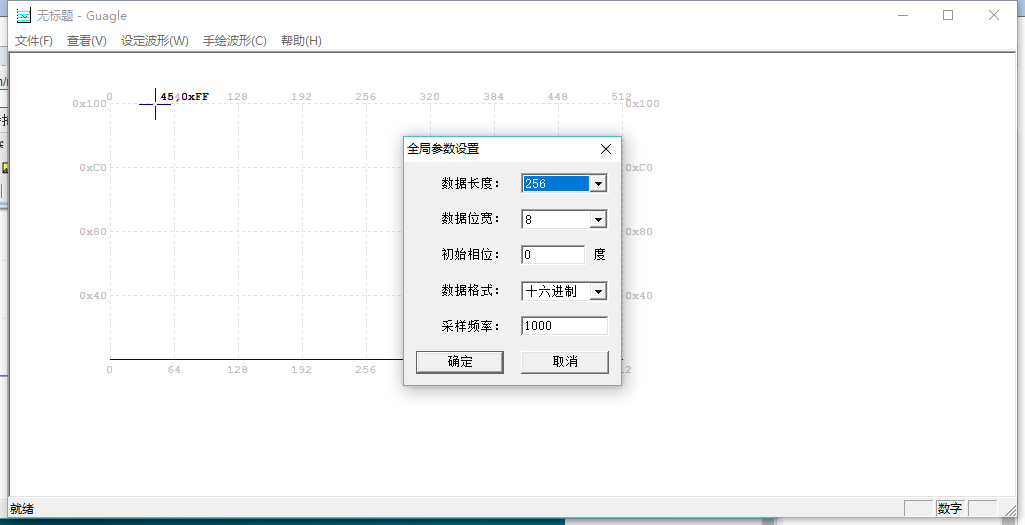

设置全局参数

本次设计为256个数据长度8位位宽

选择期望生成的波形,保存即可得到相应波形对应参数的mif文件。

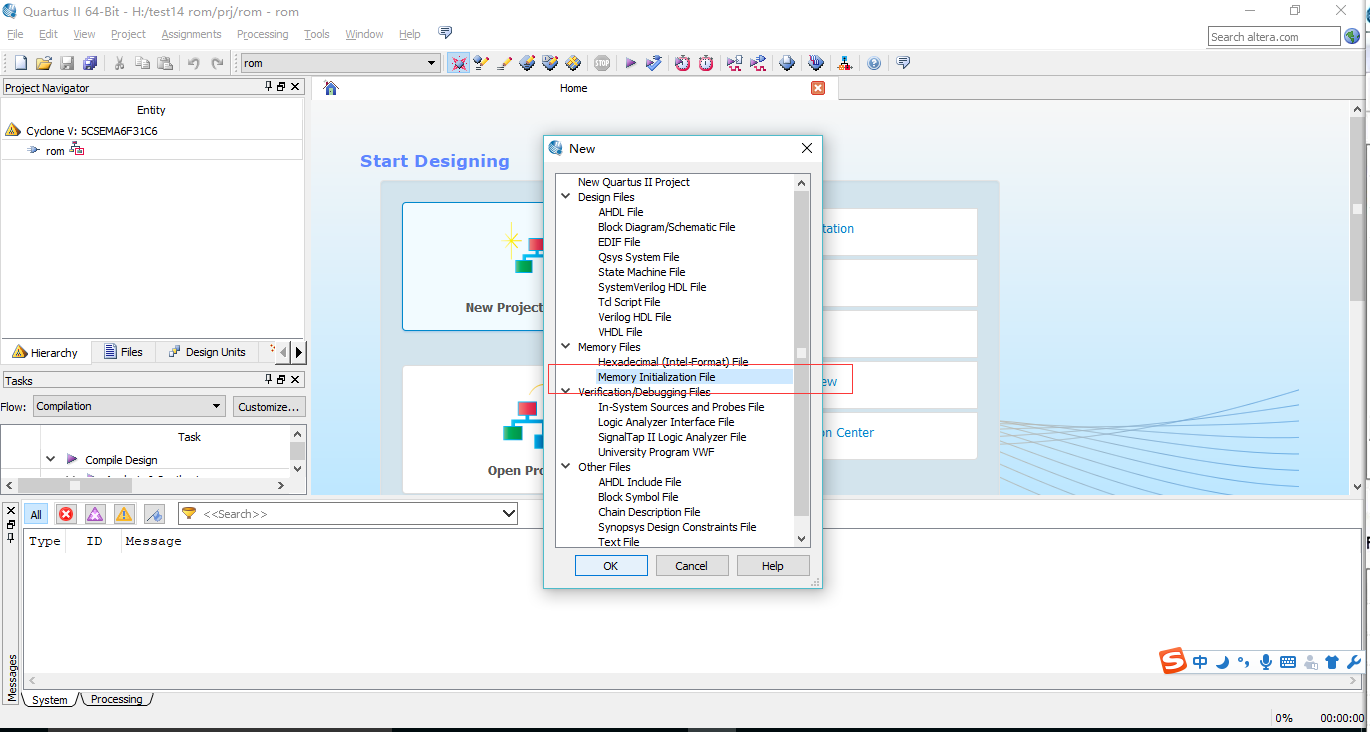

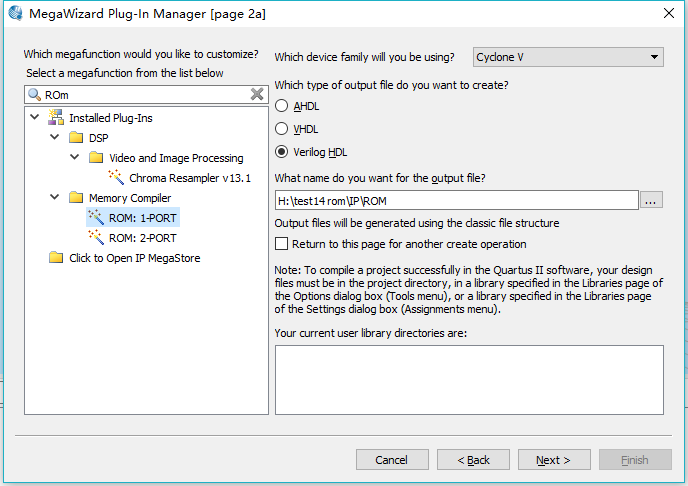

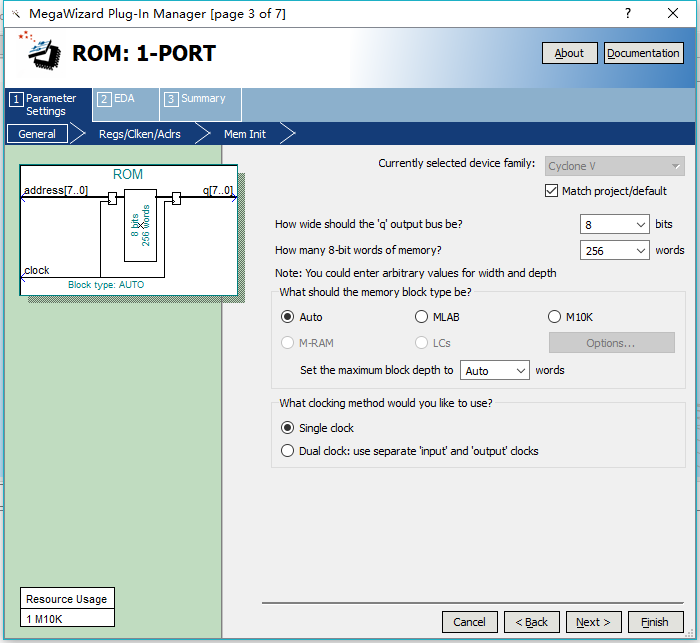

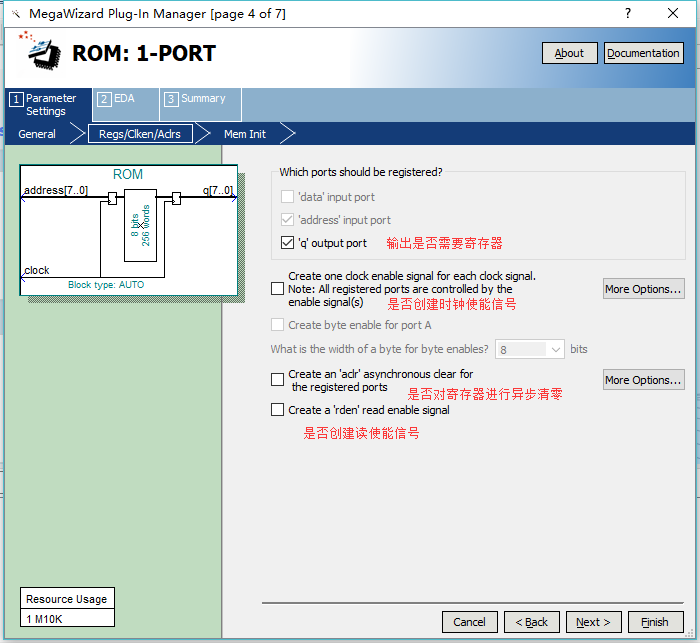

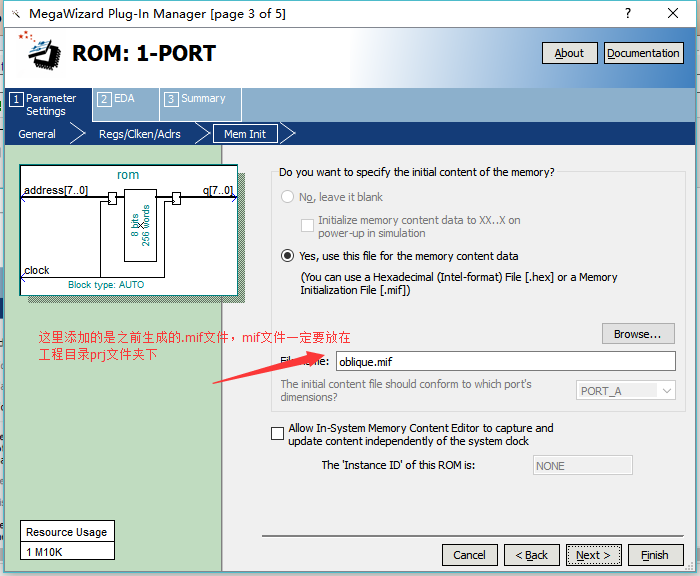

新建工程,调用rom ip核

之后直接next到finish即完成生成rom文件了。

之后直接next到finish即完成生成rom文件了。

将IP核设置为顶层文件

然后编写IP核的testbench文件

`timescale 1ns/1ns `define clock_period 20 module rom_tb; reg [7:0]addr; reg clk; wire [7:0]q; rom rom ( .address(addr), .clock(clk), .q(q)); initial clk=1; always#(`clock_period/2) clk=~clk; integer i; initial begin addr=0; for(i=0;i<=2550;i=i+1)begin #`clock_period; addr=addr+1; end #(`clock_period*50); $stop; end endmodule

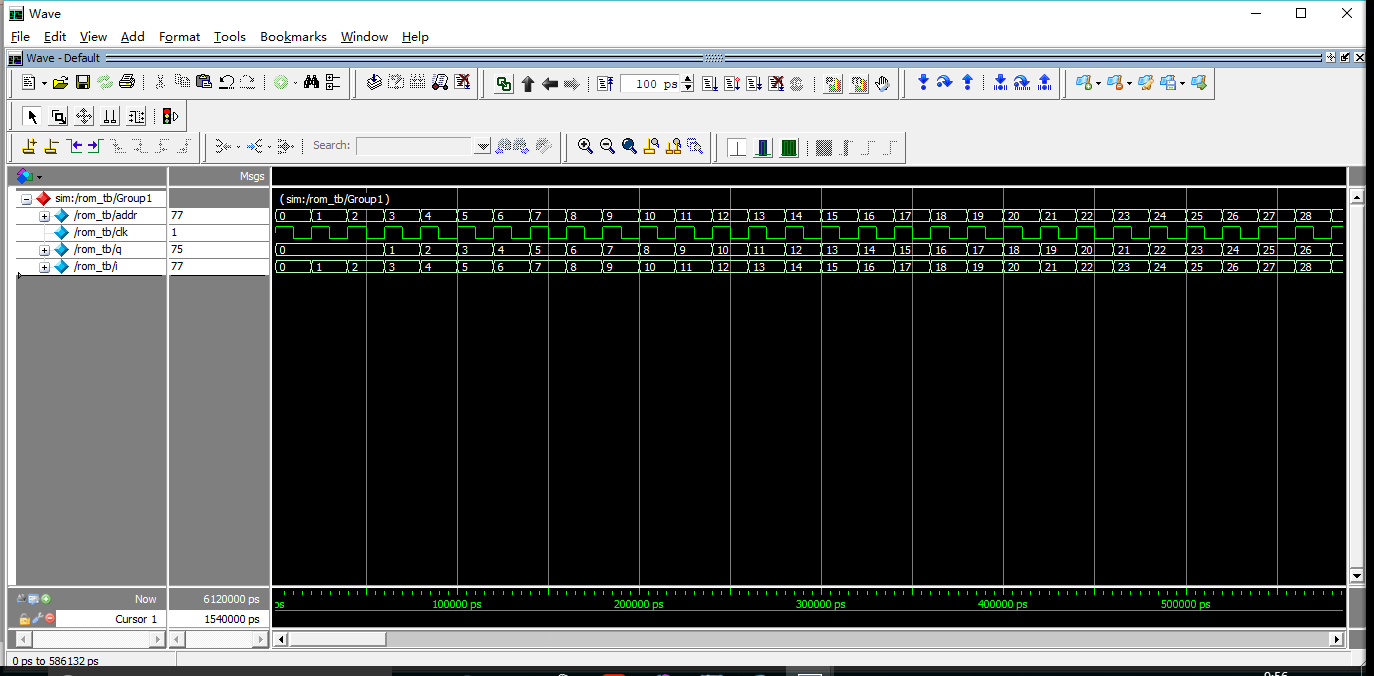

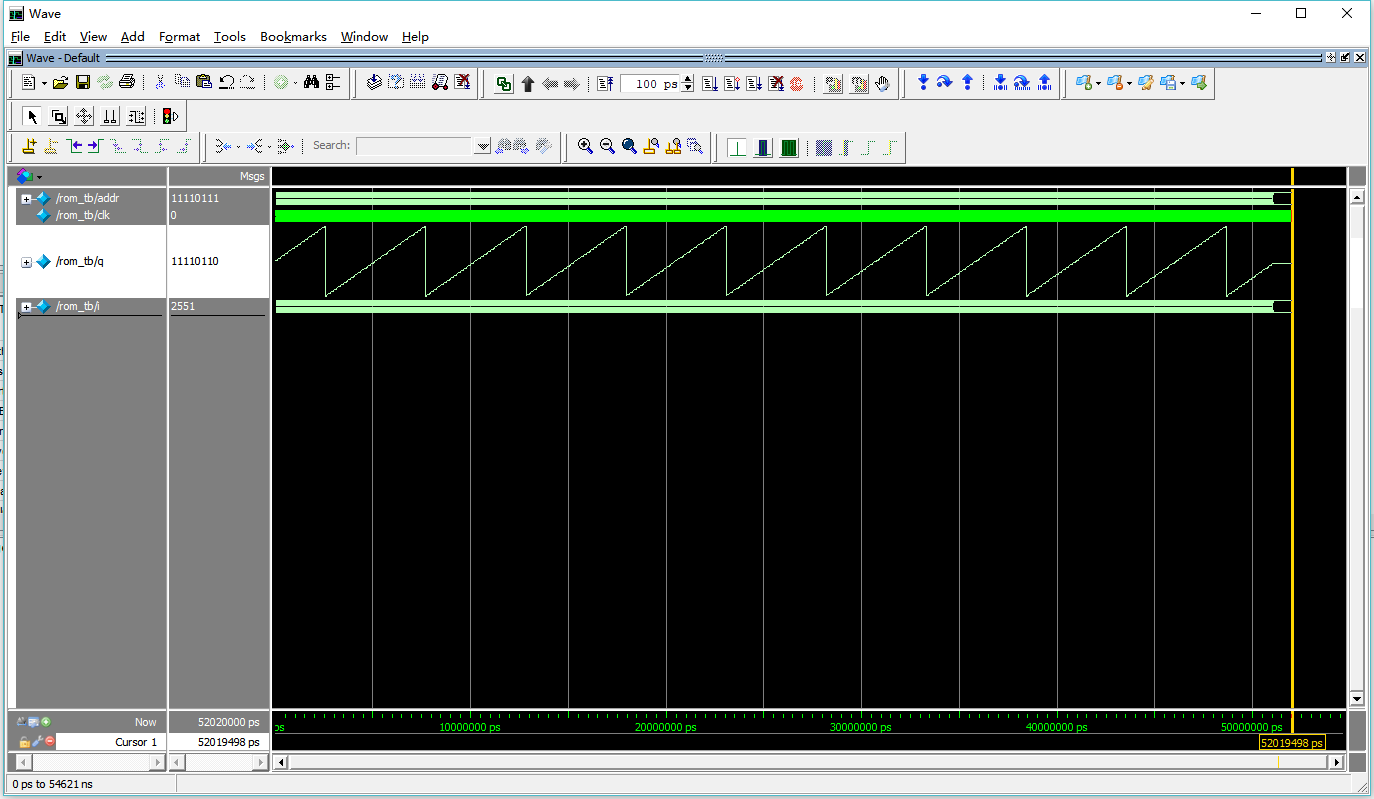

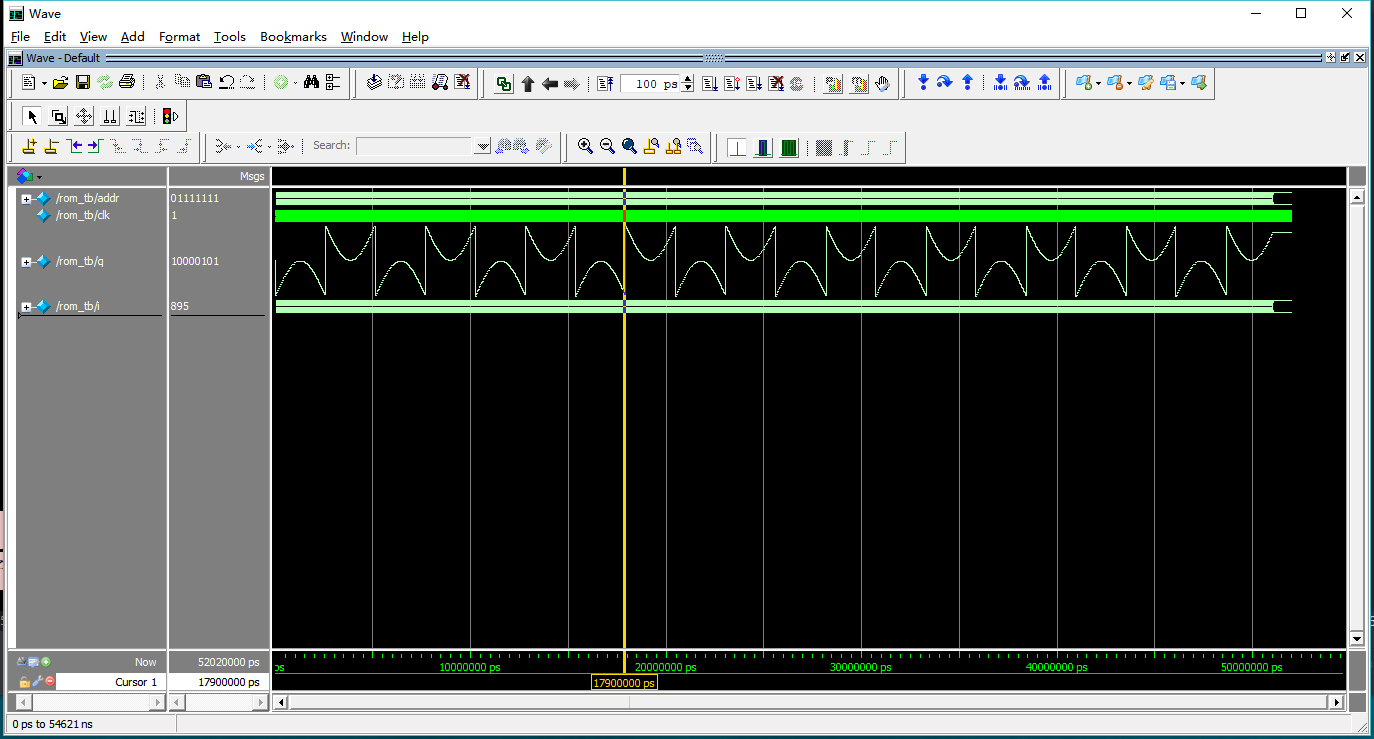

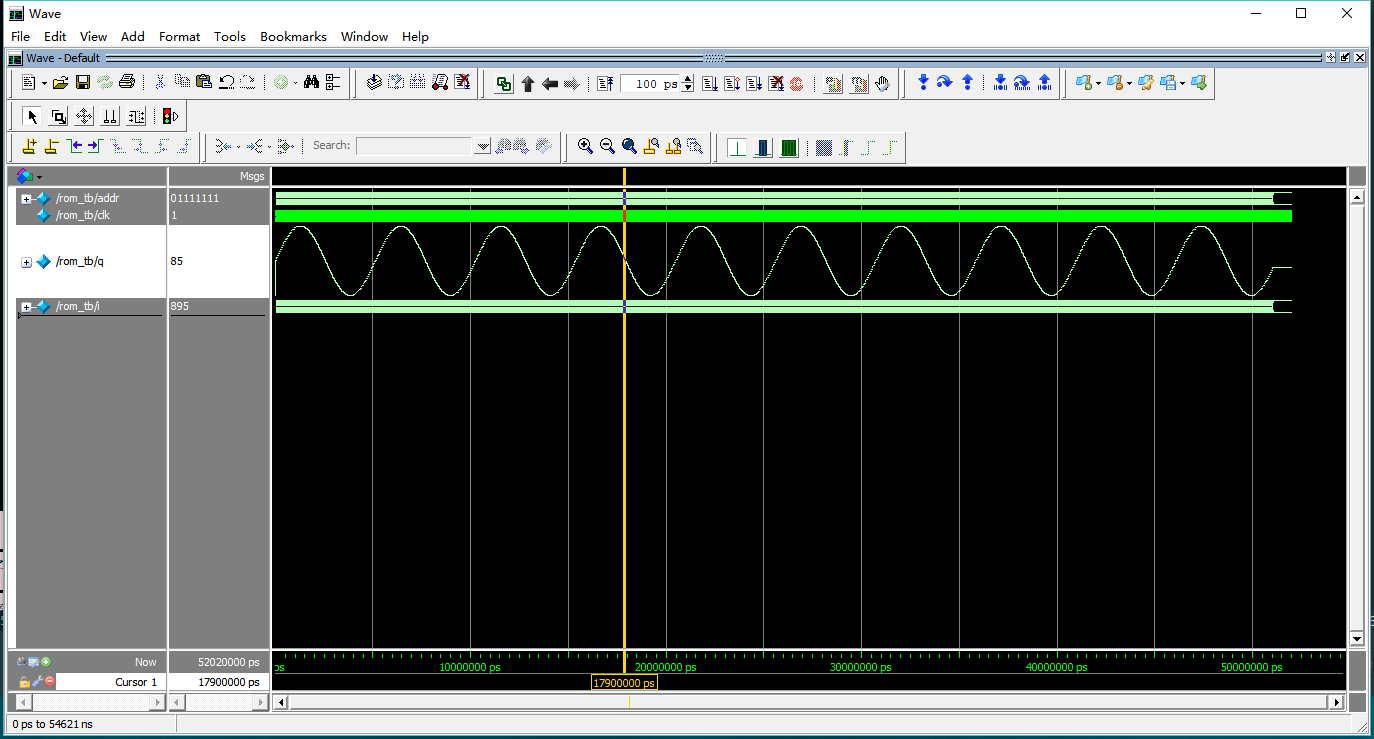

设定仿真路径进行仿真,可以看到q成功的将mif文件提取出来了,并通过仿真加强对romIP核的理解

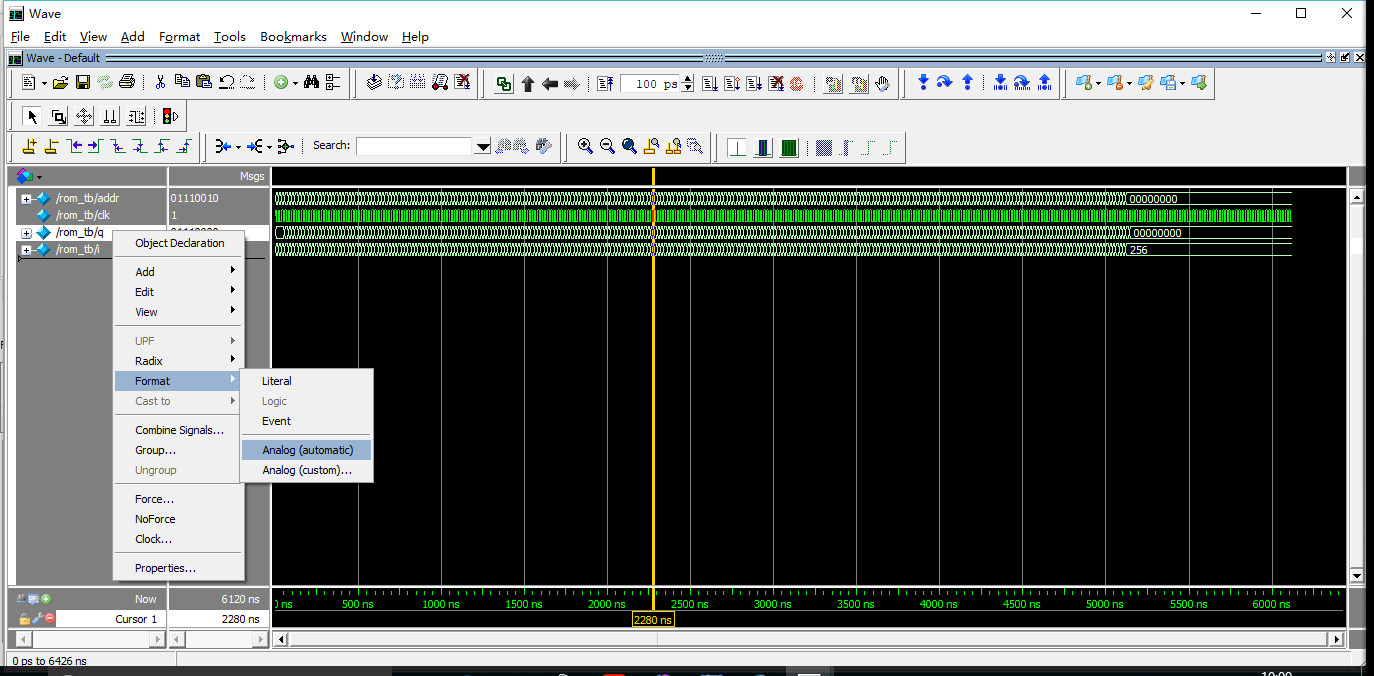

选中q,右键修改显示格式,即可看到仿真出来的模拟的锯齿波形。

将mif未见改为正弦波的mif文件观察

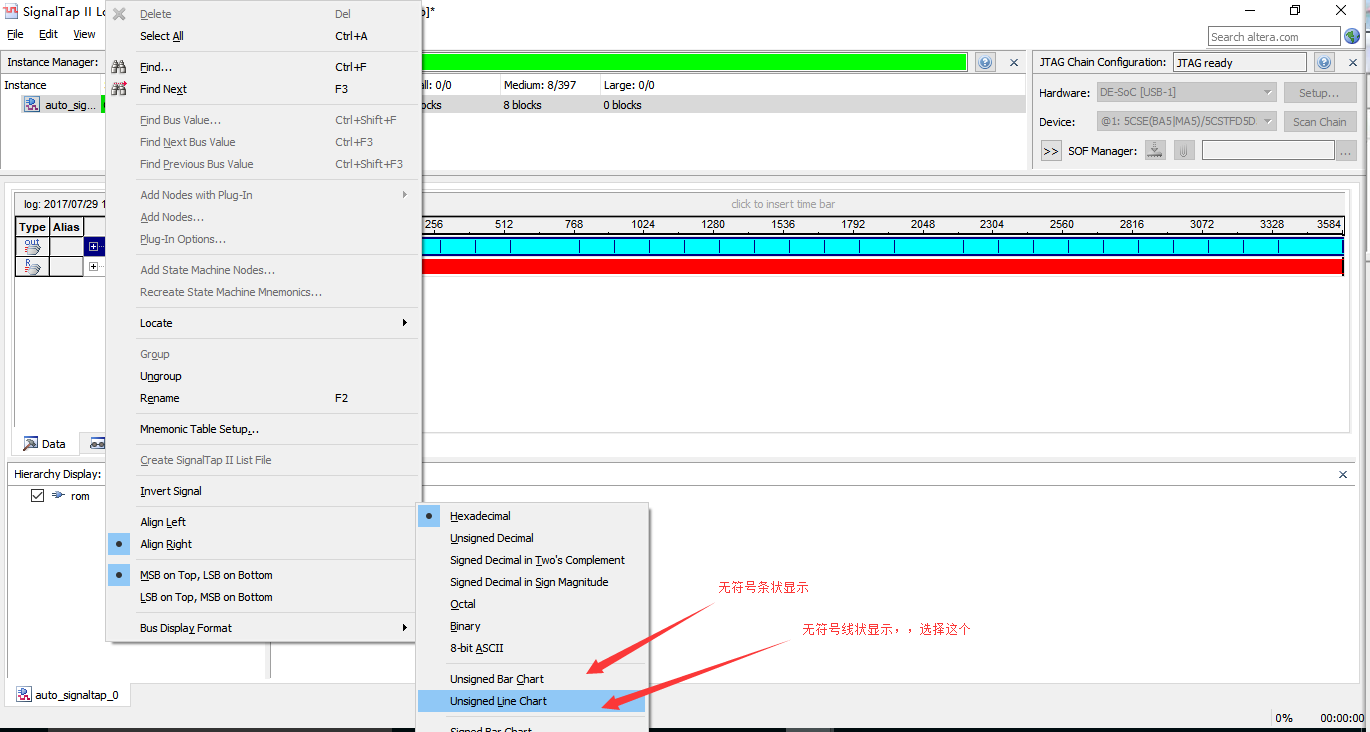

此时发现波形有断层

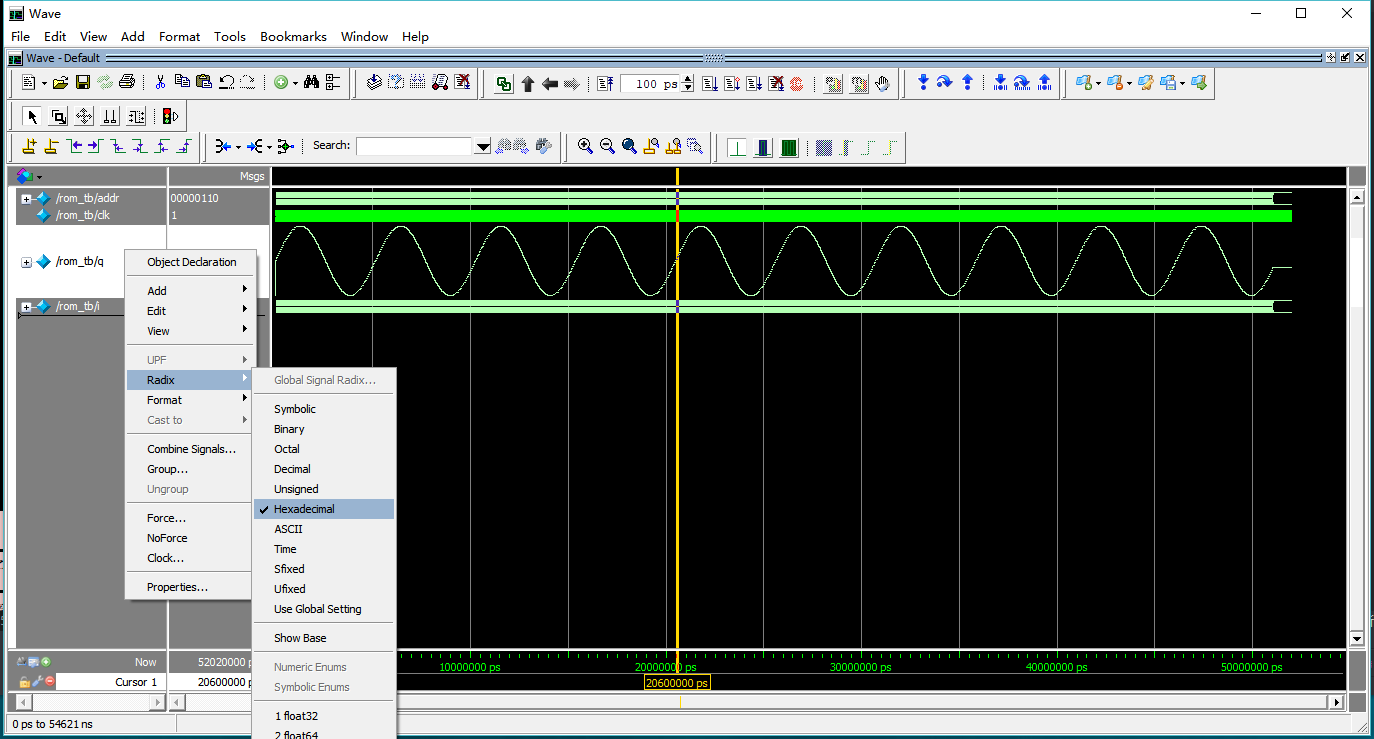

这是因为选择的显示格式为无符号的,将格式改为有符号的即可

在这里,波形发生器的仿真设计已经完成了(对于控制频率,其实就是一个控制地址变化的方式)。

新建一个rom_top文件,将其设置为顶层文件,其目的是设计地址发生模块:

module rom_top(clk, rst_n, q ); input clk; input rst_n; output [7:0]q; reg [7:0]addr; rom rom_1 ( .address(addr), .clock(clk), .q(q)); always@(posedge clk or negedge rst_n) if(!rst_n) addr<=0; else addr<=addr+1; endmodule

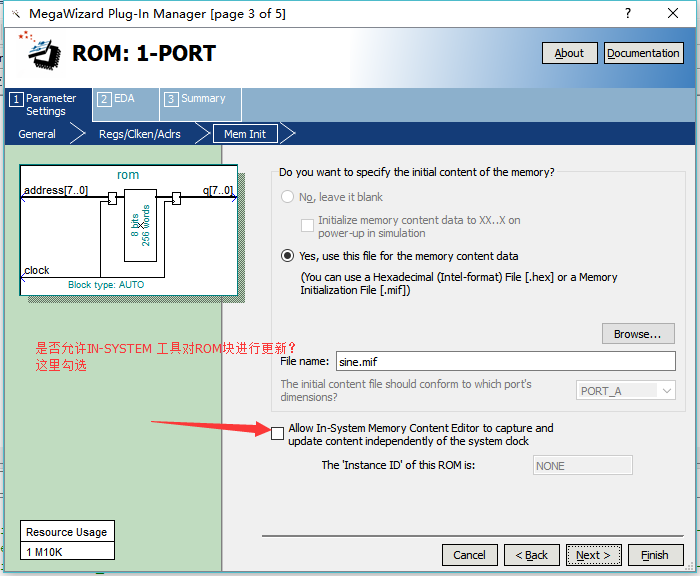

下面为了使in system memory content editor 工具在线修改ROM中的数据,需要对IP核进行设置

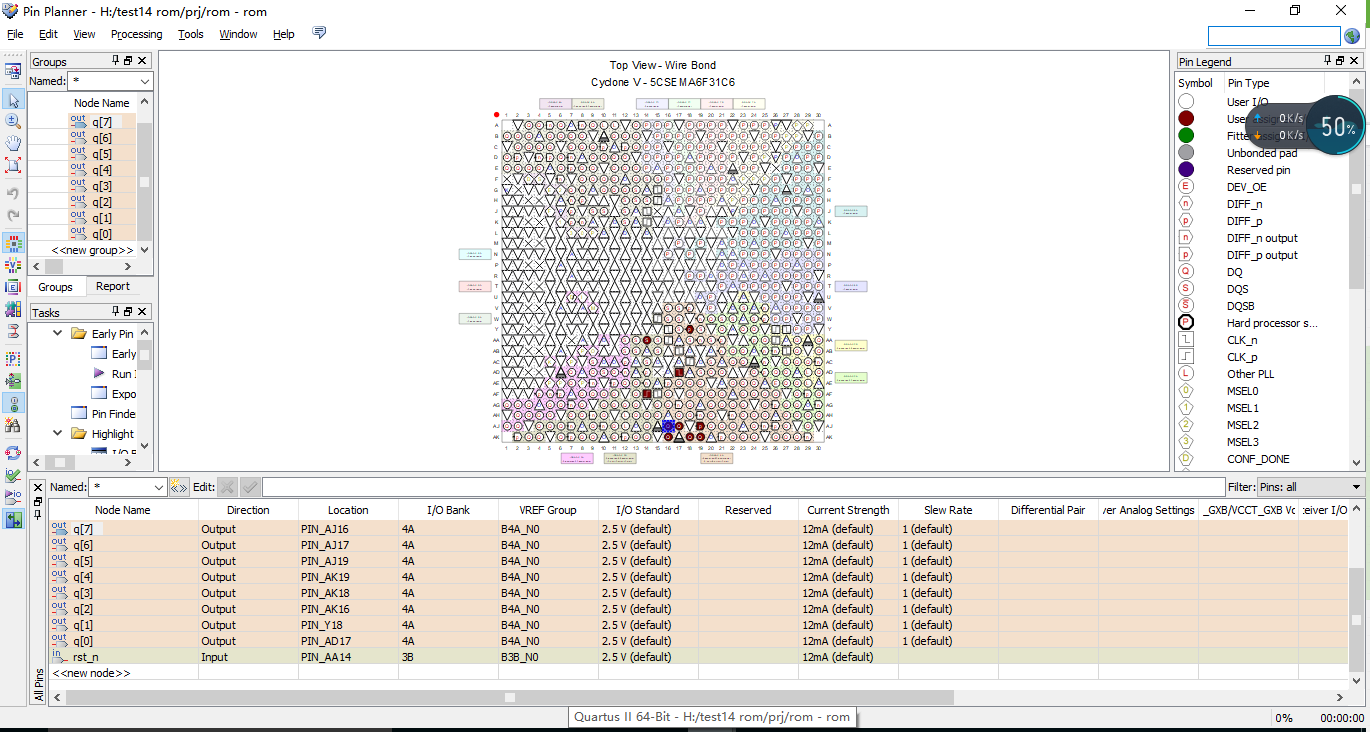

对引脚进行分配,其中q[0]~q[7]对应开发板上GOIP09~GPIO2

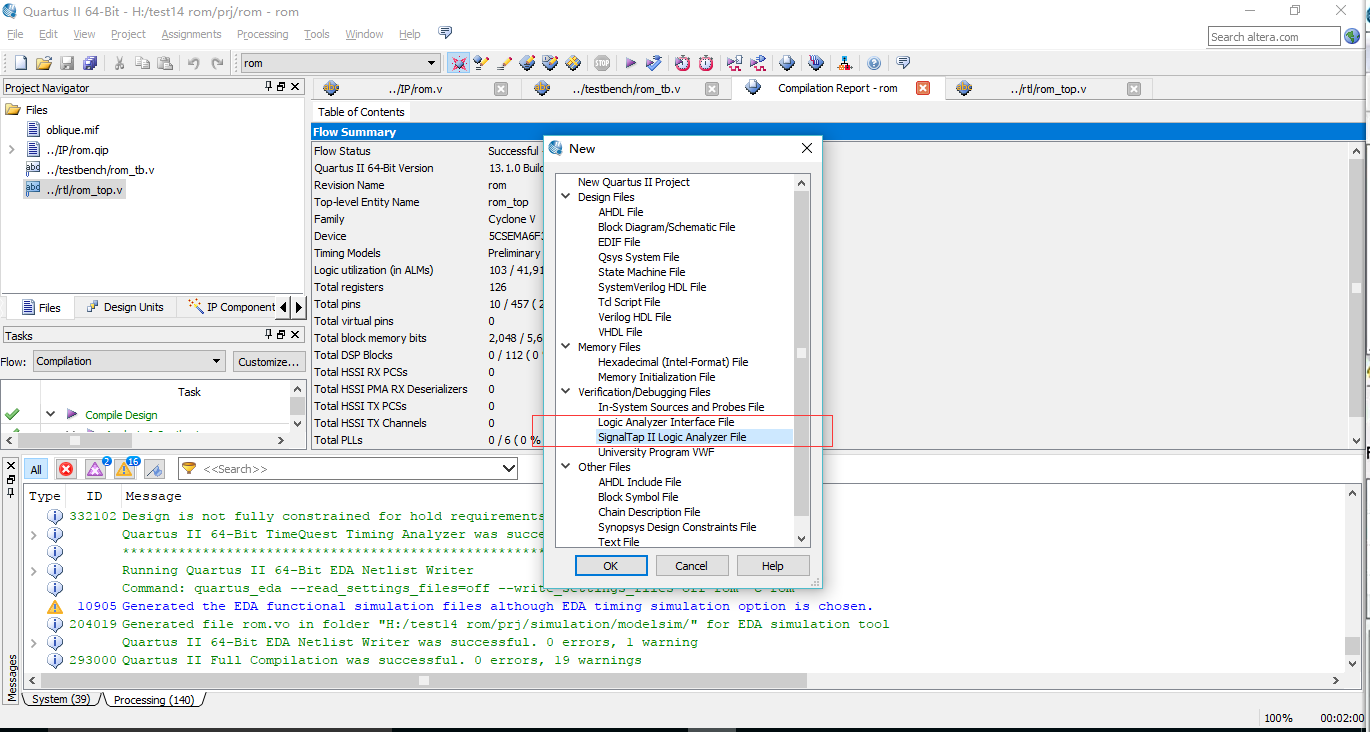

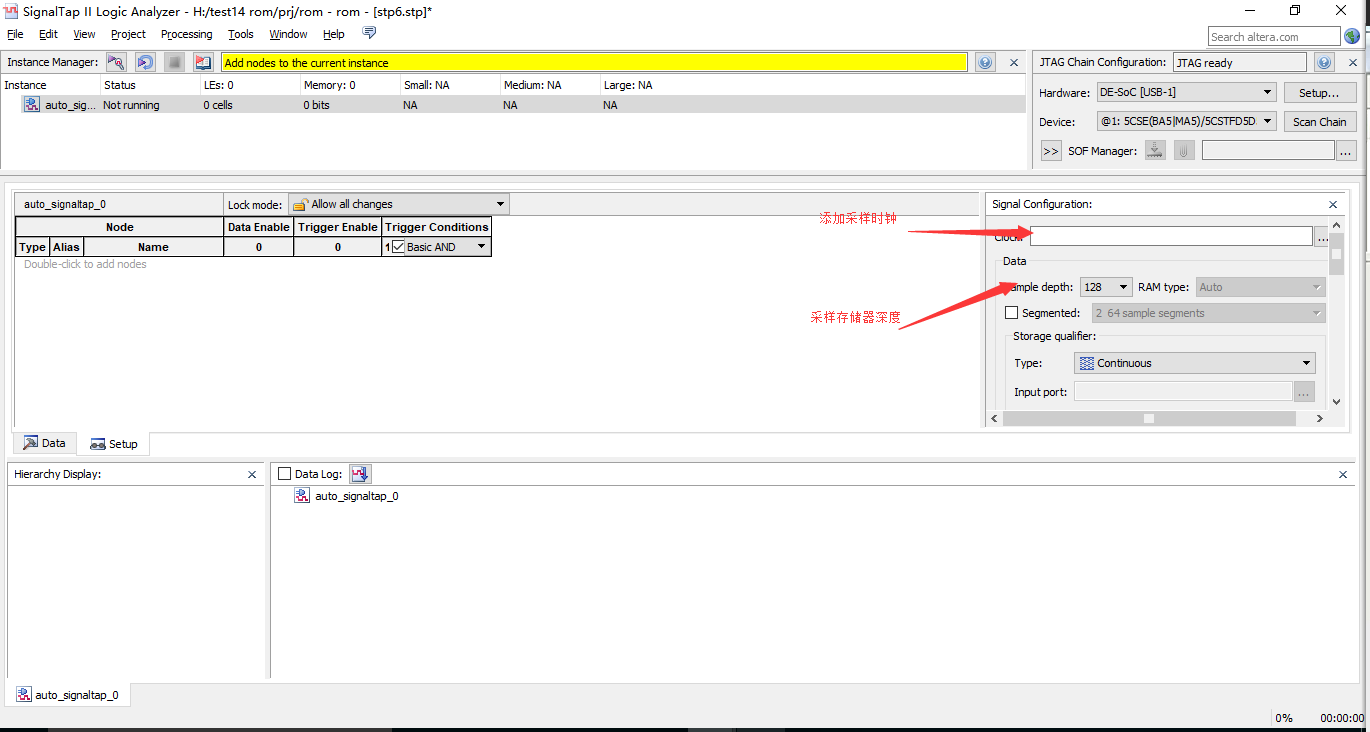

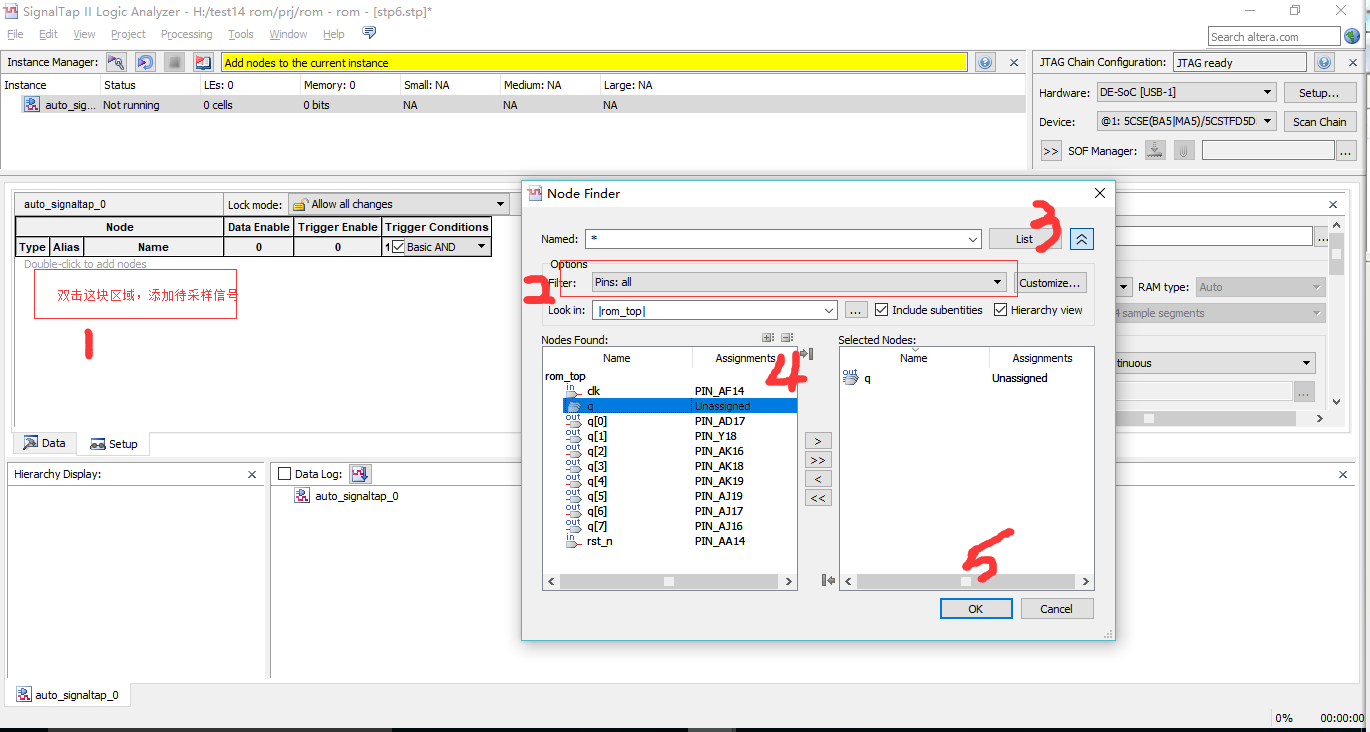

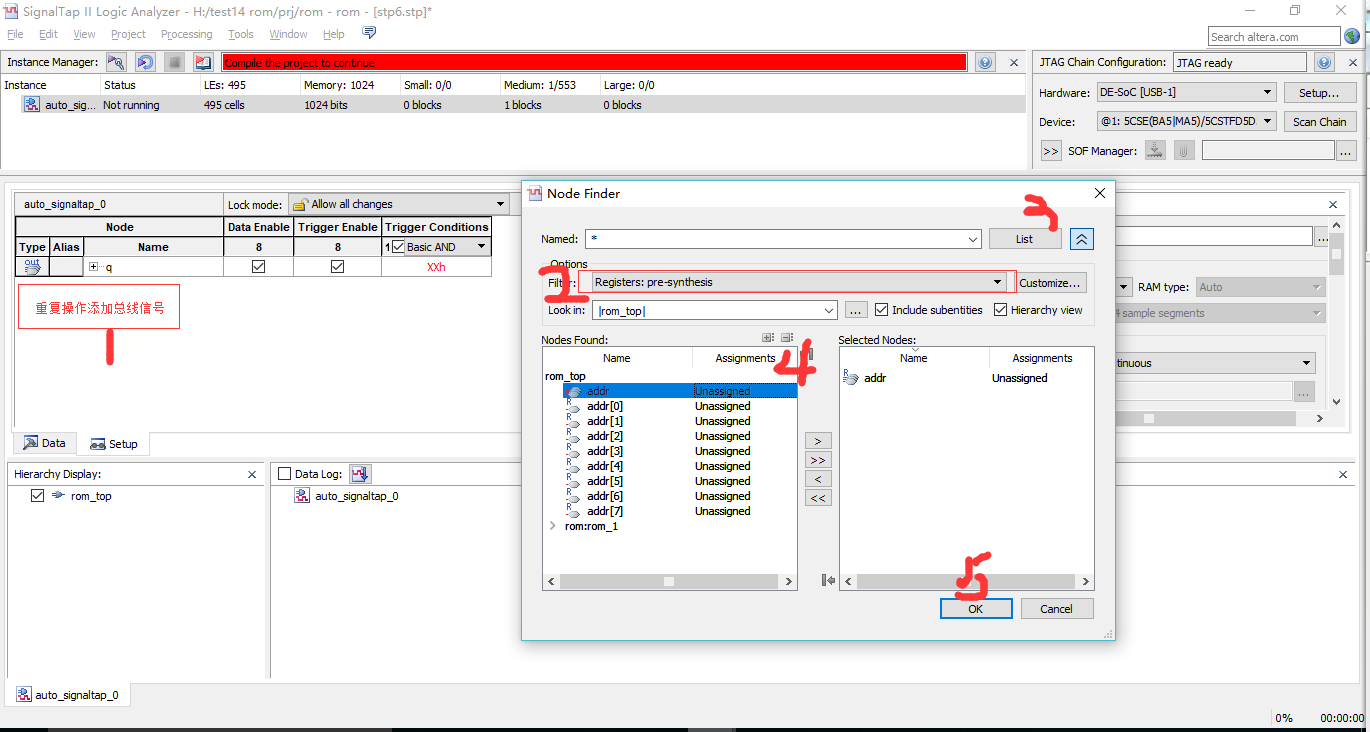

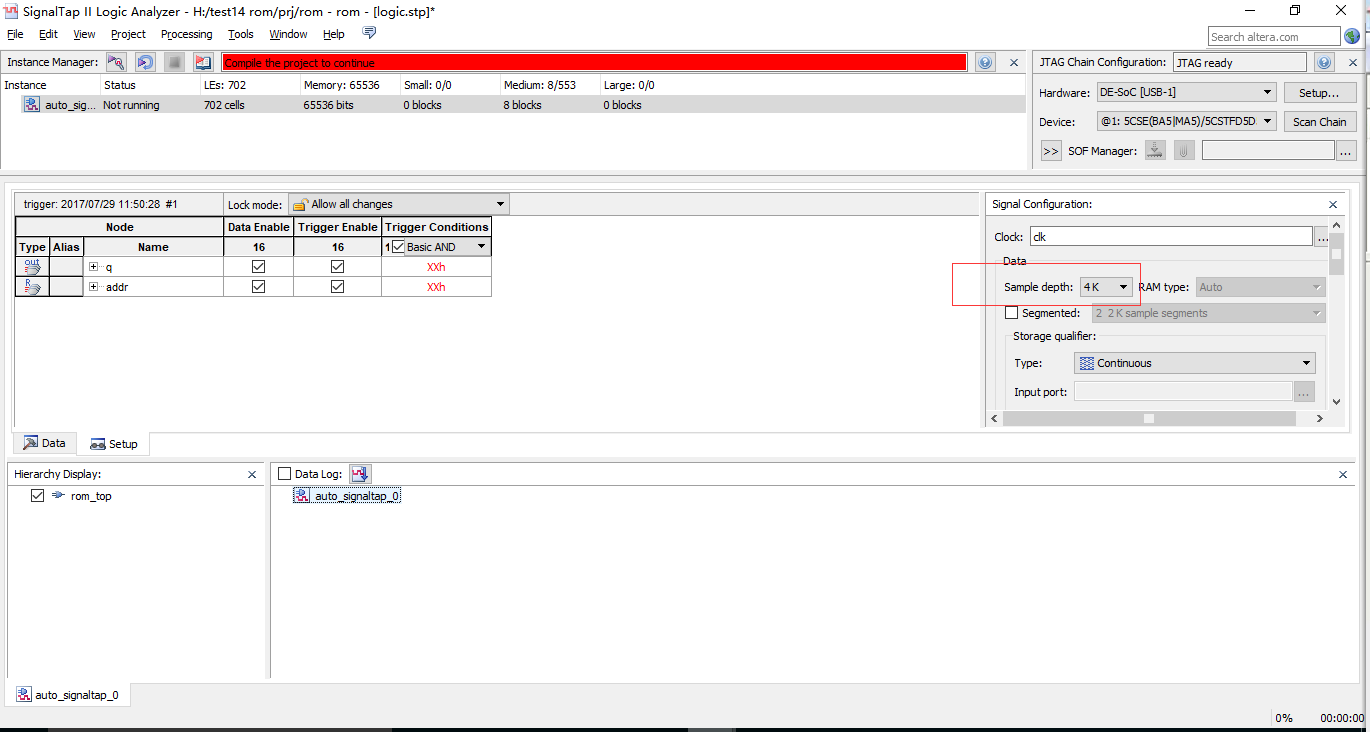

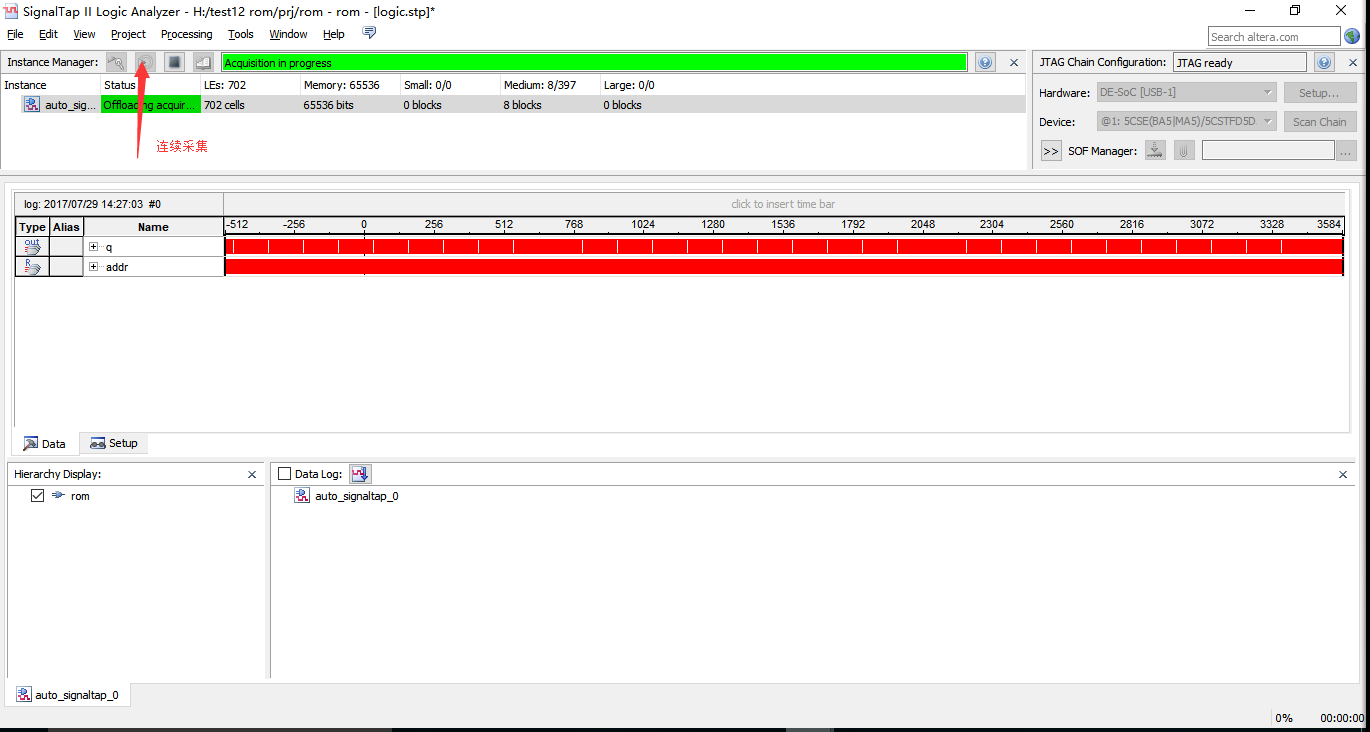

全编译后,通过FPGA内部搭建一个片上的逻辑分析仪,抓取rom里的文件:

新建一个signal tap II logic analyzer file文件

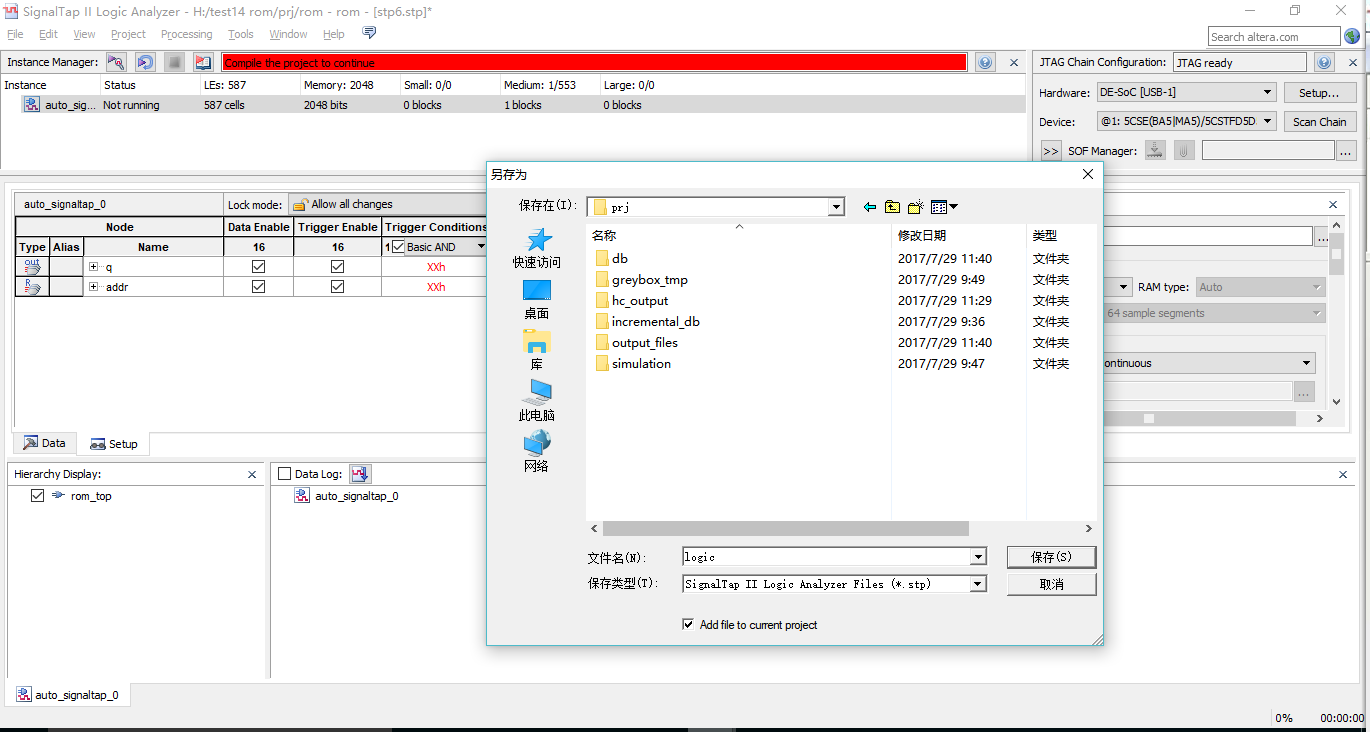

保存在工程目录下

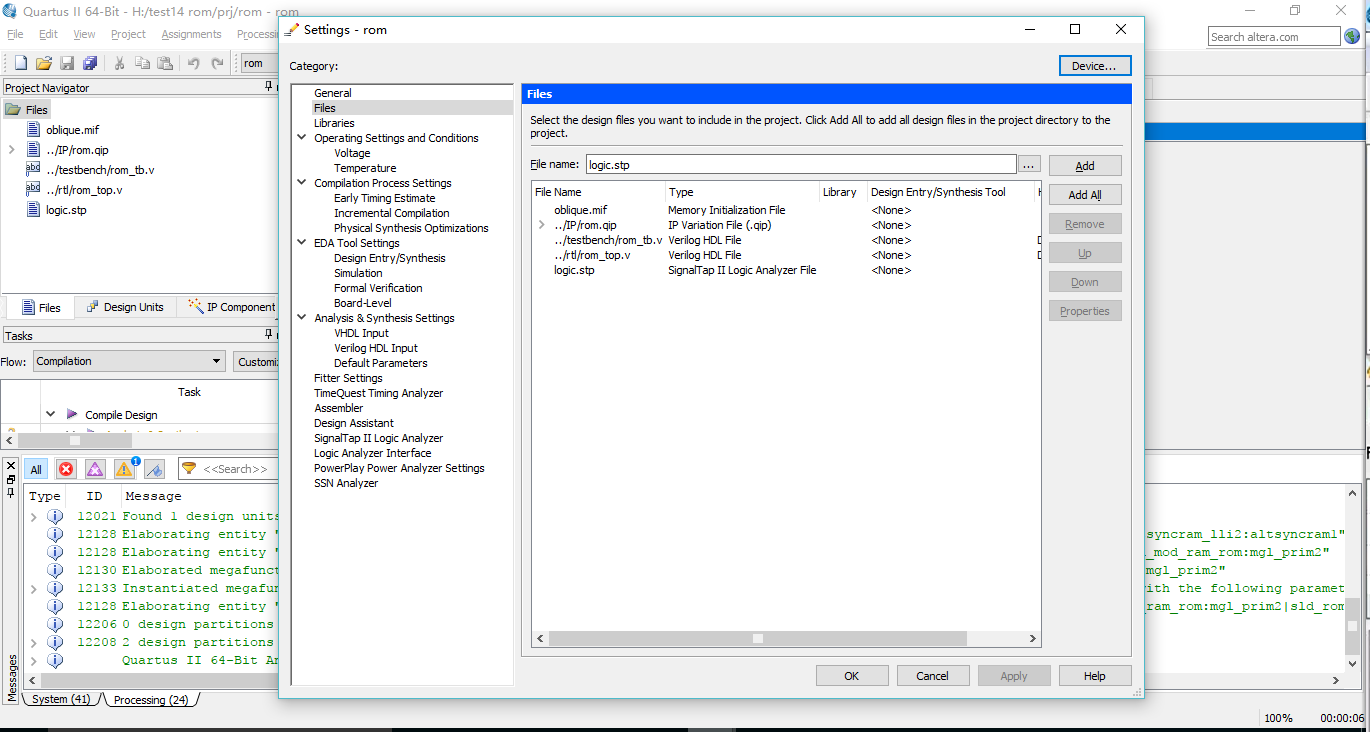

将逻辑分析仪工具添加到工程文件夹中,对工程进行全编译

将工程生成的.sof文件下载到FPGA开发板中,进行板级验证,烧写完成后打开logic.stp文件

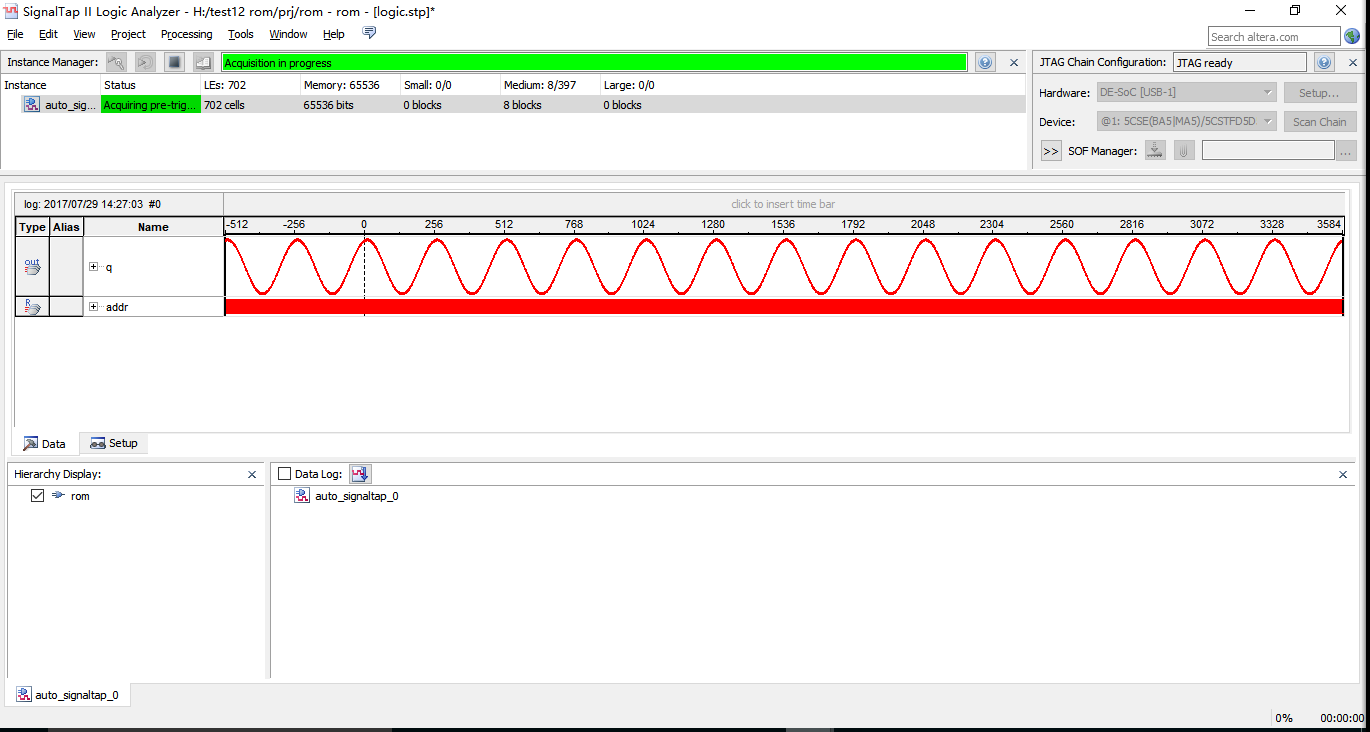

即可看到成功显示的正弦波波形了

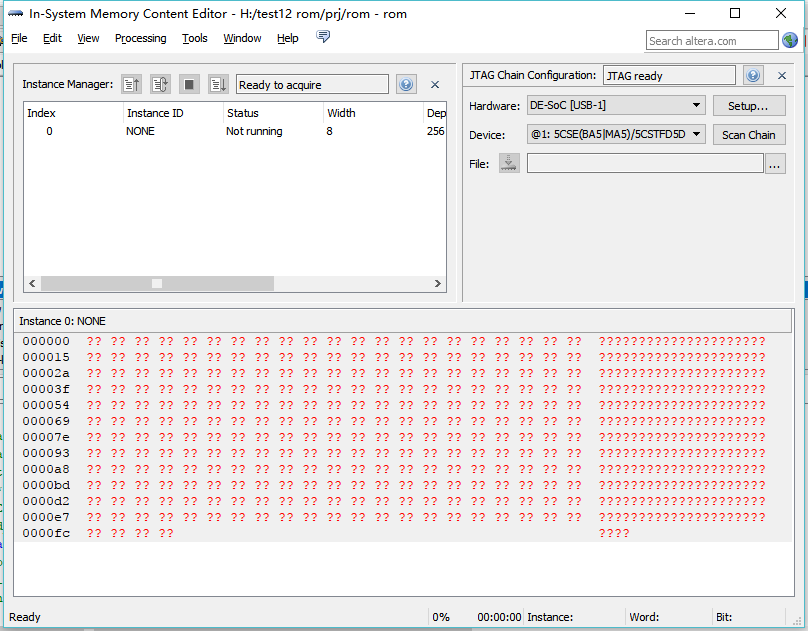

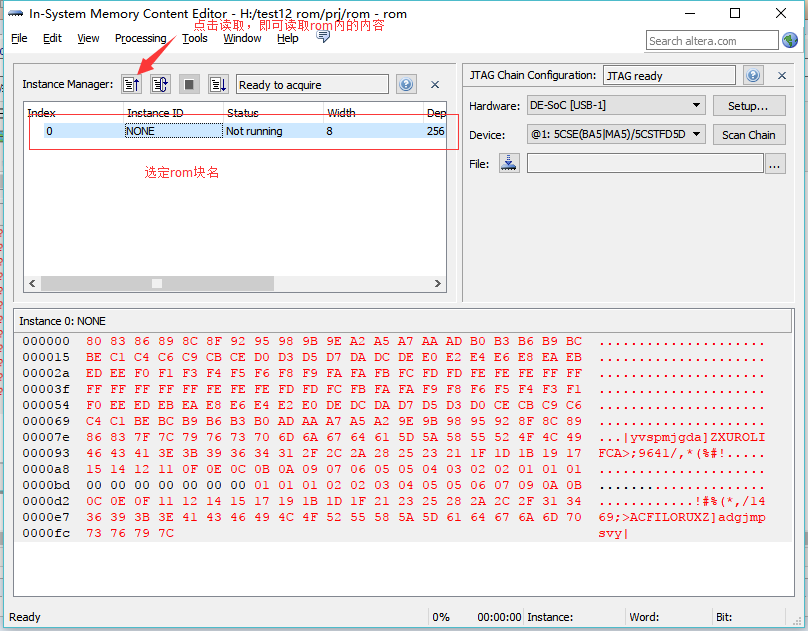

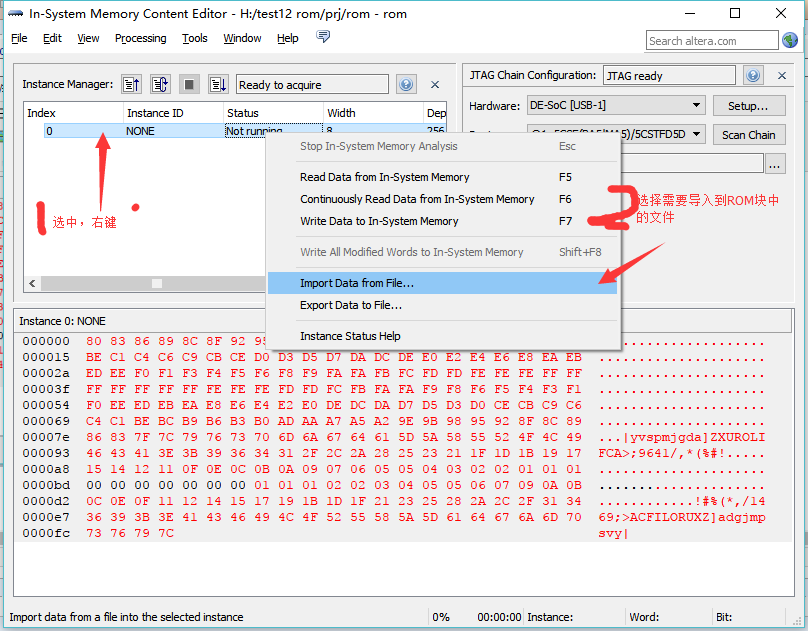

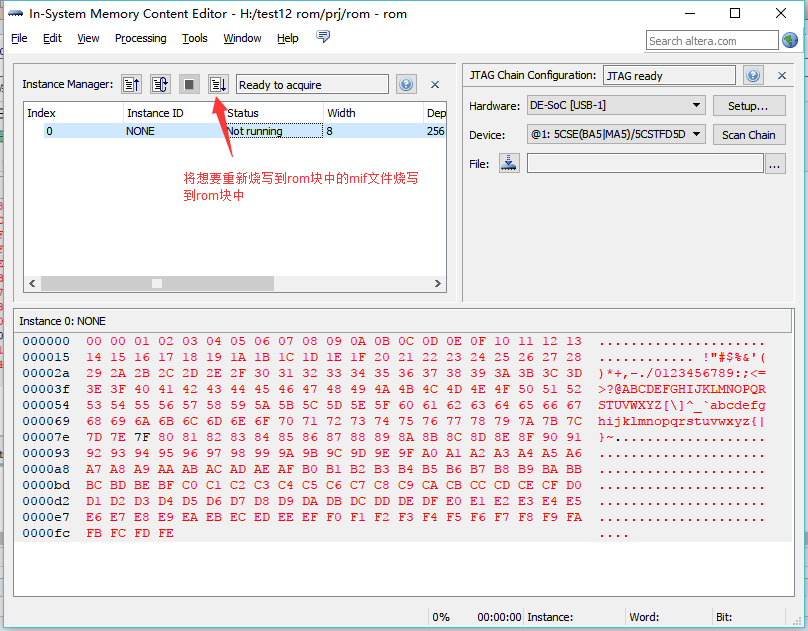

下面通过in system memory content editor 工具对rom 内容进行更改

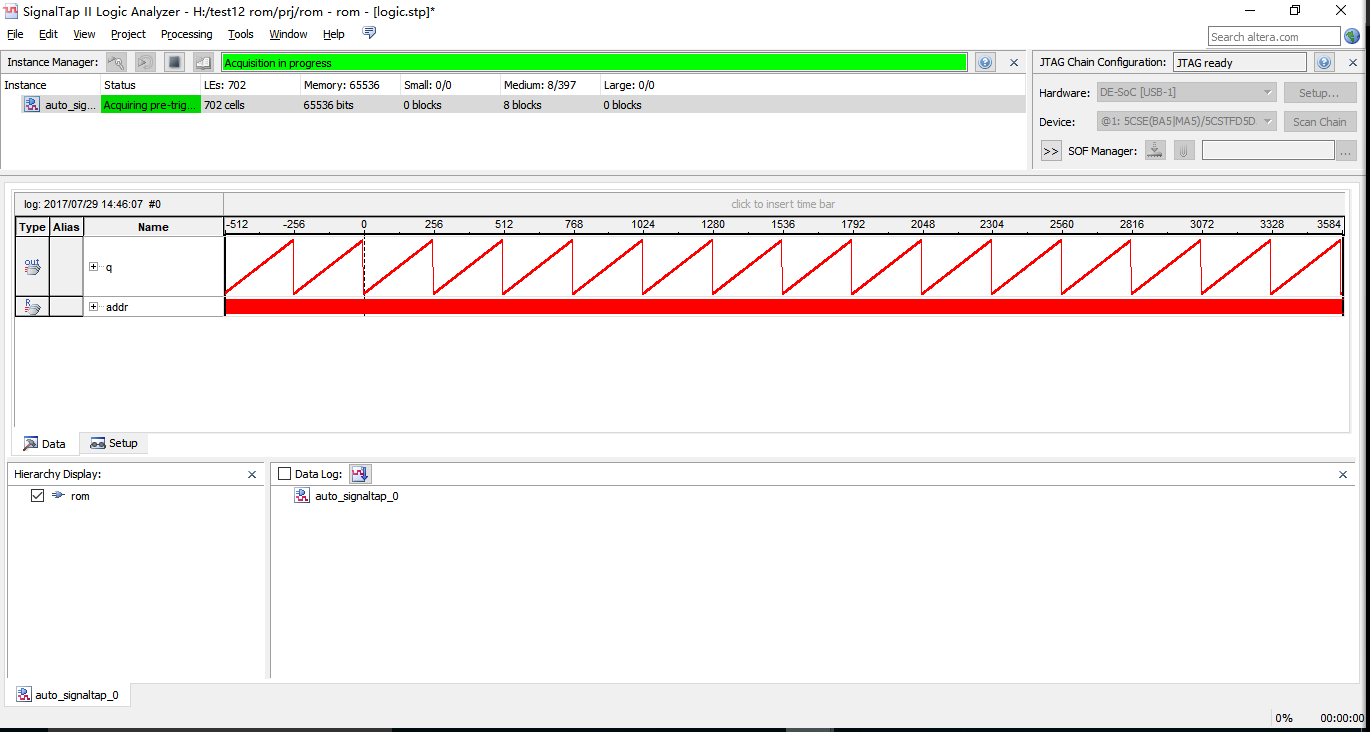

可以看到signalTap II logic analyzer中显示的波形变为了锯齿波了。

至此,整个设计就完成了