1.黑金板 简易操作: 通过判断数值累加 个人观点:黑金代码质量有待提高,讲解不够详细

2.正点原子的 位置调换

led[3:0] <= {led[2:0],led[3]};

3.传统位移

led<=led<<1; //循环左移一位

4.

# T sys_rst_n <= 1'b1; //在第20ns的时候复位信号信号拉高

# 延迟的作用,单位是上面定义的

5.

`timescale 1ns / 1ps //仿真时间单位/时间精度

6.对于 if else 如果有超过1条语句,请使用begin end。

7.对于管脚约束,一般来说寄存器可以直接对应引脚。

8.不存在的语句一定要删除,比如 rst

port connections cannot be mixed ordered and named

端口最后不能有 ‘,’

9.数据加减乘除 直接复制,会扩大位数。如果再进行其他运算 就会舍弃溢出位。

10.数据拼接 {2d'00,dat[11:2] }

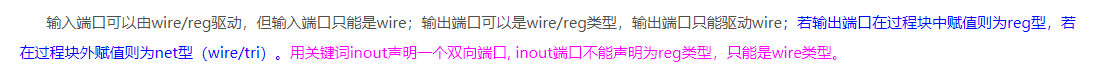

11.模块中如果要控制io端口,请使用wire

不指定就默认为1位wire类型。专门指定出wire类型,可能是多位或为使程序易读。wire只能被assign连续赋值,reg只能在initial和always中赋值。wire使用在连续赋值语句中,而reg使用在过程赋值语句中。

12.NET "data_in[0]" LOC = P44 | IOSTANDARD = "LVCMOS33"; //管脚约束 | 两边一定要留空间

13.wire 变量不能初始化,不能连接到1 或者0.或者初始化时候链接完毕。

14.对于没有输出缓冲的时钟,不能连接到多个模块。

15.

16.ram 时钟 如果启用了输入输出时钟,相关操作要延迟加一个周期。

17.如果顶层的网线只是将引脚传递给底层,该线路将被系统移除。

18.

fpga 内部使用布线操作,该种方法特别适合于 按位操作。

19.Assignment under multiple single edges is not supported for synthesis

@输入有两个信号,但是 if 却没有考虑两个信号的两种情况

20.仿真reg信号 init里面必须指定初始电平,不然直接使用 always a=~a;//将得到未知电平

21.function 内部初始化变量

22.

//处理用途?任务 有输出和输入 而且可以使用全局变量 函数可以相互调用,不能使用 输出类型

task automatic data_process;

endtask

23.verilog误区:定义reg和wire尽量不要赋初值,百度网友可能会告诉你这个初值系统会省略,实际上ise会通过逻辑实现,而不是省略。如果这个初值与时钟沿判断相反,将会造成更大的资源浪费,正确的做法应该是在 reset里面赋初值。

24.时序约束也要注意,还有 init函数。网友可能说的有问题。