平台介绍

Zynq7000是赛灵思公司(Xilinx)推出的行业第一个可扩展处理平台Zynq系列。旨在为视频监视、汽车驾驶员辅助以及工厂自动化等高端嵌入式应用提供所需的处理与计算性能水平。

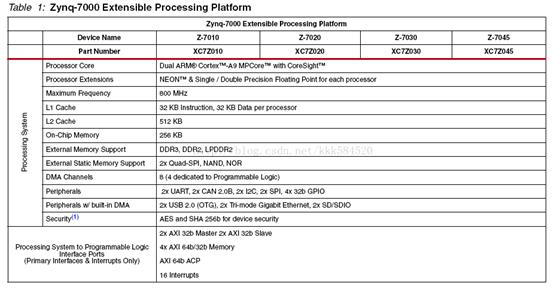

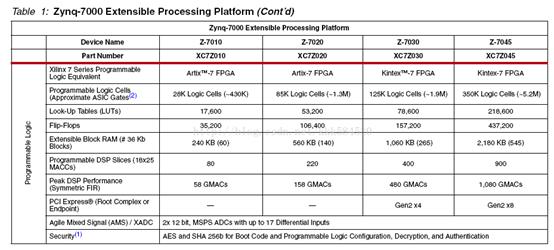

在2010年4月硅谷举行的嵌入式系统大会上,赛灵思发布了可扩展处理平台的架构详情,这款基于无处不在的ARM处理器的SoC可满足复杂嵌入式系统的高性能、低功耗和多核处理能力要求。赛灵思可扩展处理平台芯片硬件的核心本质就是将通用基础双ARMCortex-A9MPCore处理器系统作为“主系统”,结合低功耗28nm工艺技术,以实现高度的灵活性、强大的配置功能和高性能。由于该新型器件的可编程逻辑部分基于赛灵思28nm7系列FPGA,因此该系列产品的名称中添加了“7000”,以保持与7系列FPGA的一致性,同时也方便日后本系列新产品的命名。

Zynq-7000系列的可编程逻辑完全基于赛灵思7系列FPGA架构来设计,可确保28nm系列器件的IP核、工具和性能100%兼容。最小型的Zynq-7000、Zynq-7010和Zynq-7020均基于专门针对低成本和低功耗优化的Artix-7系列;较大型的Zynq-7030和Zynq-7040器件基于包括4至12个10.3Gbps收发器通道,可支持高速片外连接的中端Kintex-7系列。所有四款产品均采用基于2个12位1MspsADC(模数转换器)模块的新型模拟混合信号模块。

Zynq®-7000 SoC 系列集成 ARM® 处理器的软件可编程性与 FPGA 的硬件可编程性,不仅可实现重要分析与硬件加速,同时还在单个器件上高度集成 CPU、DSP、ASSP 以及混合信号功能。Zynq-7000 系列包括单核 Zynq-7000S 器件和双核 Zynq-7000 器件,是单位功耗性价比最高的全面可扩展的 SoC 平台,可充分满足您的独特应用需求。

芯片架构

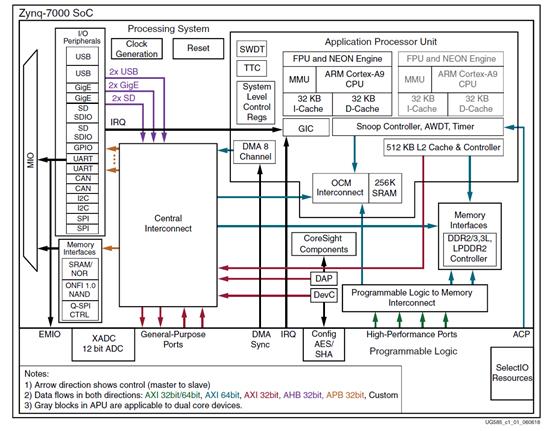

ZYNQ 7000SOC构成: Cortex-A9 + FPGA。

Cortex-A9 处理器:提供了具有高扩展性和高功耗效率的解决方案。利用动态长度、八级超标量结构、多事件管道及推断性乱序执行( Speculative out-of-order execution),它能在频率超过1GHz的设备中,在每个循环中执行多达四条指令,同时还能减少主流八级处理器的成本并提高效率。

主要外围器件

在ZYNQ 7000的SOC中,主要分为2个部分:PS(Processing System)、PL(Progarmmable Logic)。

PS:

-

APU:应用处理单元(Application processor unit) -

内存接口(Memory interfaces) -

IOP:I/O 外设(I/O peripherals) -

内部通信总线(Interconnect)

上电启动过程

Zynq启动流程和ARM处理器类似,PS部分是启动和配置过程的主设备,芯片引导必须由处理器驱动。在没有外部JTAG的情况下,处理系统(PS)与可编程逻辑(PL)都必须依靠PS来完成芯片的初始化配置。

ZYNQ有两大类启动模式:从BootROM主动启动,从JTAG被动启动。

BootROM支持:SD卡启动、QSPI-Flash启动

在BootROM模式中,上电复位后会读取设备模式引脚来决定从什么设备启动芯片。

0、zynq 芯片里有个 rom 里面固化了一段不可修改的程序, 只有 zynq 一上电, 这段程序就会执行, 它将初始化CPU和 NAND、 NOR、 SD卡等基本外设。初始化好,BootROM读取存储器中的程序代码,并将FSBL拷贝到OCM(On-chip memory)里。

1、第一阶段引导程序(First Stage Boot Loader,FSBL)启动,BOOT.bin开始执行:首先继续配置PS,PS初始化好后,再配置PL,最后还可以加载阶段2的代码。

2、开始执行PS端代码,也可以是第二阶段引导程序(Second Stage Boot Loader,SSBL)。完全在用户的控制之下,是可选的。

SDK构建

完整的SDK包括:2个IDE + 1个构建ARM-LINUX工具(可选)

2个IDE:Xilinx Vivado + Xilinx SDK(Windows,Linux可运行)

1个构建工具:PetaLinux(仅Linux)

Vivado + SDK的开发流程:

-

(FPGA工程师)根据硬件情况,使用Vivado配置有关的硬件,开发好逻辑以后,导出硬件信息以及bitstream。

-

嵌入式软件工程师根据提供的硬件信息,建立有关的工程。

PetaLinux的开发流程:

1.(基于Vivado导出的结果)构建工程。

-

导入硬件信息。

-

配置Linux、根文件系统后自动构建。

-

构建全部,包括Linux、根文件系统。

-

烧写到板子中。

注:打包、固化可由SDK或完成。