http://www.zembedded.com/cortex-m3-registers-in-depth/

Thanks for the overwhelm response you show in our first tutorial on Cortex_M3 series controllers.

This is going to be the second tutorial, where we are going to discuss about the registers available

on Cortex-M3 series of microcontrollers.

If you are yet to go through the first tutorial then please click here to read it first.

I will repeat, for a deep knowledge to these registers please read the datasheet

or user manual provided by NXP or other manufacturer.

At the end of the tutorial I am providing the links for user manual for cortex-M3 controllers by NXP.

A brief about Registers:

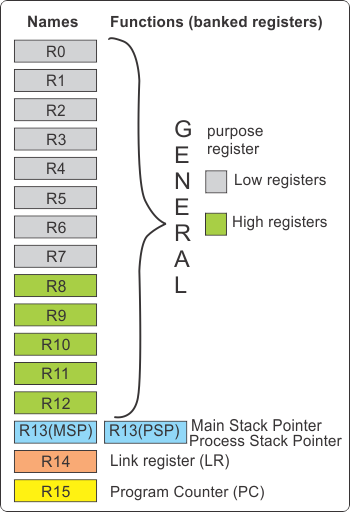

It has a register bank R0 to R15, where R0-R7 are called as low registers and R8-R15 are high registers.

R-13 is stack pointer (SP). This SP(stack pointer) is banked, with only one copy of the R-13 visible at a time.

Out of these 16 registers, R0 to R12 are 32-bit general purpose registers for data operations.

A few of Thumb instructions can only access a sub set of this general purpose registers (low registers R0-R-7). Let’s dig into it.

R0 through R7:

These R0 to R7 registers are also called as low registers.

These registers can access by both 16-bit Thumb instructions and 32-bit Thumb-2 instructions.

R8 through R12:

These registers are also called as High registers.

They are accessible by all Thumb-2instructions but not by all 16-bit Thumb instructions.

Stack Pointer R13:

This R13 is stack pointer (SP).

In Cortex-M3 there are two separate stack pointers.

This twostack pointers are allowed to set up two separate stack memories.

If you use the R13 name, in that case you can access only current SP.

The other one is inaccessible unless you use special instructions to move to special register

from general-purpose register (MSR) and move special register to general-purpose register (MRS).

Main Stack Pointer (MSP):

This is default stack pointer and this is used by OS kernel and exception handlers.

Process Stack Pointer (PSP):

Used by use application mode only.

This is used by the base-level application code (when not running an exception handler).

Link Register: R14 is Link Register.

When we call subroutine, the return address is stored in the link register.

Inside an assembly program, you can write it as either R14 or LR.

LR is used to store the return program counter (PC) when a subroutine or function is called.

Program Counter: R15 is program counter.

This stores the current program address.

You can access PC in assembler code by either R15 or PC.

Because of thepipelined natureof the Cortex-M3 processor, when you read this register,

you will find that thevalue is different than thelocation of the executing instruction.

Special Registers:

- Program Status Registers (PSRs)

- Interrupt Mask Registers(PRIMASK, FAULTMASK and BASEPRI)

- Control Register(CONTROL)

Special Registers and their functions:

xPSR:

This register is to provide the arithmetic and logic processing flags (zero flag and carry flag),

execution status and current executing interrupt number.

PRIMANSK:

This can disable all the interrupts except nonmaskable interrupt (NMI) and hard fault.

FAULTMASK:

This register function is to disable all the interrupts except non maskable interrupt.

BASEPRI:

This register function is disabling all interrupts of specific priority level or lower priority level.

CONTROL:

It defines the privileged status and stack pointer selection.