一:数字逻辑综合概念

1: 概念

仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到 的标准。逻辑综合需要基于特定的综合库(工艺库),不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。

约束条件是人为加上去的,比如创建时钟,时钟频率等;工艺库是特定厂商提供

一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)

逻辑综合工具Synopsys的Design Compiler(DC),Cadence的 PKS,Synplicity的Synplify等。另外,和综合工具配合使用的还有很多其他工具,如静态时间分析工具,等效性检查工具等等。Synopsys公司和Cadence公司都提供完整的工具包。

2: 工具

对于ASIC,使用DC工具;对于FPGA,使用ISE,QUARTUS都可

3: synthesis=translation+logic optimization+gate mapping

translation:GTECH将不同的硬件语言翻译成统一格式,加上约束条件后,进行优化(optimization)和映射

gate mapping:将工艺库中基本信息拿出来,一一映射

最后得到网表(sdf文件),进行后仿真 (ddc文件) (ddc,sdf还有v文件,都是什么?)

二:求取延迟方式

1: WLM mode

线负载模型,将负载等效成RC模型,得到延迟信息;但延迟包括互连线延迟和基本单元延迟,所以有误差

2: 拓扑模式(Topographical mode)

在DC综合中通过物理库,预布局吐出脚本约束,得到延迟信息。

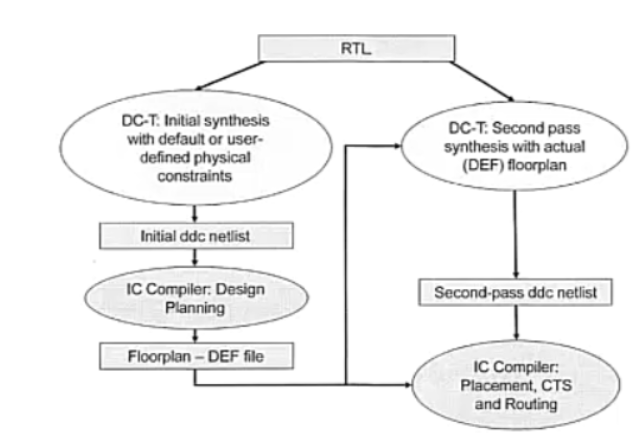

过程(如下图):DC-T第一次综合 ——> 预网表信息 ——> 预布局布线吐出脚本约束,得到器件布置的大致模型 ——>根据前面的大致模型计算延迟约束 ——> DC-T第二次综合。

三:综合目标

area,delay(性能)的权衡

四:DC三个界面

1:Design Vision(GUI)大规模的芯片设计不会使用,用于看局部电路

linux %design_vision -topographical

2: DC shell(shell,命令行格式)

linux%dc_shell -topographical_mode dc_shell-topp>

3: Batch mode

linux% dc_shell -topo -f run.tcl | tee -i run.log //run.tcl是运行的脚本;run.log是运行的某些结果报告。