一:关于RAM的存储容量

硬件数据手册在描述存储容量时,通常给出地址的总个数与一个地址的存储位宽(不包括错误检测位与奇偶校验位)

例如:256k*16的RAM芯片可以存储256kbit=256*1024bit=28*210=218bit,这里一个地址的存储位宽为16(数据线数目);总线的宽度为:218/16=214,即14根地址线;容量218=16*214(数据线数目*2地址线数目)。

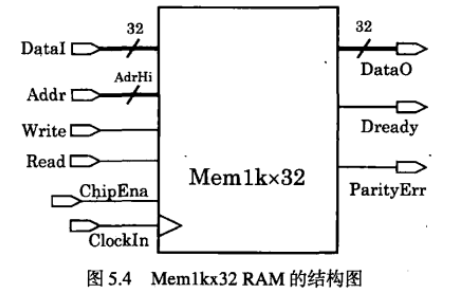

下面我们将设计一个带有奇偶校验位的“1kb*32”的静态RAM的verilog模型。该存储器的容量为1024bit;一个地址存储位宽为32(数据线数目);共有1024/32=32个地址,址线的寻址空间为0-32,addr的位宽为5(reg[4:0])。

二:奇偶校验位

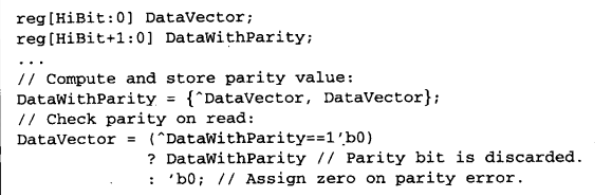

奇偶检验在RAM里很常用,每个地址的比特1(或者0)的数目都被记录了下来,然后每个地址分配一个额外的比特,根据1(或者0)的比特数目将它赋为1或0;

例如偶校验,在数据最高位加入1bit数据,使得1的个数位偶数;这里可以使用异或来表示;

三:计带有奇偶校验位的1kb*32的静态RAM

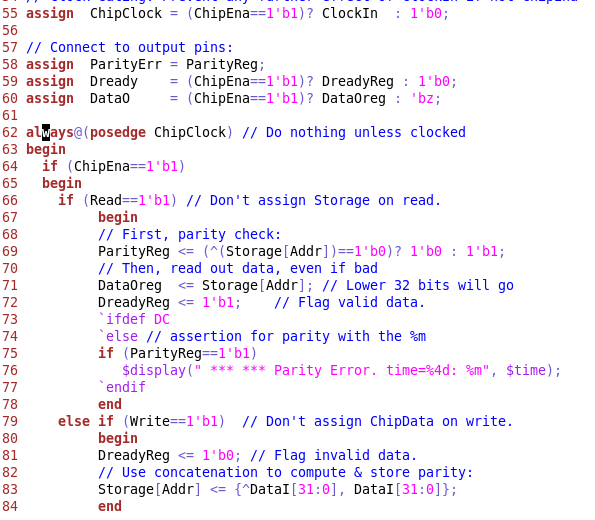

1:由上面的理解,Addr为reg[4:0],DataI为32位reg[31:0],内部存储器为reg[32:0] Storage[31:0],加上奇偶校验位一共32位,包含32个地址。

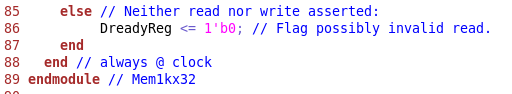

2:主要代码

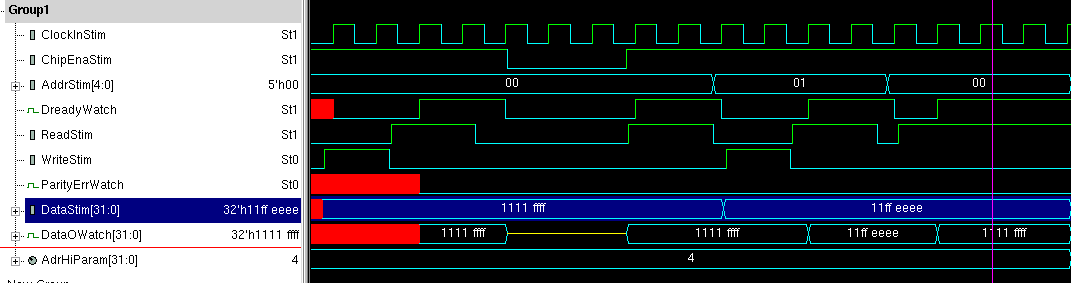

3:make

4:打开dve