一、特性参数

·300M内部时钟频率

·可进行频移键控(FSK),二元相移键控(BPSK),相移键控(PSK),脉冲调频(CHIRP),振幅调制(AM)操作

·正交的双通道12位D/A转换器

·超高速比较器,3皮秒有效抖动偏差

·外部动态特性:

80 dB无杂散动态范围(SFDR)@ 100 MHz (±1 MHz) AOUT

·4倍到20倍可编程基准时钟乘法器

·两个48位可编程频率寄存器

·两个14位可编程相位补偿寄存器

·12位振幅调制和可编程的通断整形键控功能

·单引脚FSK和BPSK数据输入接口

·PSK功能可由I/O接口实现

·具有线性和非线性的脉冲调频(FM CHIRP)功能,带有引脚可控暂停功能

·具有过渡FSK功能

·在时钟发生器模式下,有小于25 ps RMS抖动偏差

·可自动进行双向频率扫描

·能够对信号进行sin(x)/x校正

·简易的控制接口:

可配置为10MHZ串行接口,2线或3线SPI兼容接口或100MHZ 8位并行可编程接口

·3.3V单电源供电

·具有多路低功耗功能

·单输入或差分输入时钟

·小型80脚LQFP 封装

二、概述

AD9854数字合成器是高集成度的器件,它采用先进的DDS技术,片内整合了两路高速、高性能正交D/A转换器通过数字化编程可以输出I、Q两路合成信号。在高稳定度时钟的驱动下,AD9854将产生一高稳定的频率、相位、幅度可编程的正弦和余弦信号,作为本振用于通信,雷达等方面。AD9854的DDS核具有48位的频率分辨率(在300M系统时钟下,频率分辨率可达1uHZ)。输出17位相位截断保证了良好的无杂散动态范围指标。AD9854允许输出的信号频率高达150MHZ,而数字调制输出频率可达100MHZ。通过内部高速比较器正弦波转换为方波输出,可用作方便的时钟发生器。器件有两个14位相位寄存器和一个用作BPSK操作的引脚。对于高阶的PSK调制,可通过I/O接口改变相位控制字实现。具有改进DDS结构的12位I和Q通道D/A转换器可以提供较大的带宽并有较好的窄带无杂散动态范围(SFDR)。如果不使用Q通道的正交功能,它还可以通过配置,由用户编程控制D/A转换。当配置高速比较器时,12位D/A输出的方波可以用来做时钟发生器。它还有两个12位数字正交可编程幅度调制器,和通断整形键控功能,并有一个非常好的可控方波输出。同时脉冲调制功能在宽带扫频中也有重要应用。AD9854的300M系统时钟可以通过4X和20X可编程控制电路由较低的外部基准时钟得到。直接的300M时钟也可以通过单端或差分输入。AD9854还有单脚输入的常规FSK和改进的斜率FSK输出。AD9854采用先进的0.35微米COMS工艺在3.3V单电源供电的情况下提供强大的功能。

AD9854采用节省空间的80脚LQFP表面装配封装和改进散热的80脚LQFP封装。AD9854的引脚与AD9852的单频信号发生器模式相兼容。AD9854的特定操作允许温度是工业级范围:-40到85摄氏度。

三、引脚配置和功能描述

四、管脚功能表

五、操作说明

AD9854正交数字信号发生器是一款有着广泛应用的非常灵活的器件。器件包括一个48位的相位累加器,可编程基准时钟乘法器,反辛格滤波器,数字乘法器,两个12位/300HZ数模转换器,一个高速模拟比较器和内部逻辑电路。这款高度集成的器件可以用作本机震荡发生器,灵活的时钟发生器和FSK/BPSK调制器。

Analog Devics股份有限公司的技术指南提供了关于器件功能模块的操作说明。指南包括利用DDS器件产生信号的技术描述并提供了适合多种数字化实体的基本应用。文件,《关于数字信号发生器的技术指南》在AD公司DDS网页www.analog.com/dds DDS技术库中提供。

1、操作模式

AD9854有5种可编程操作模式。为了选择某一模式,必须对控制寄存器(并行操作地址:1FH)中的3个相关位进行编程设置。具体描述在下表:

| 模式 2 | 模式1 | 模式 0 | 结果 |

| 0 | 0 | 0 | Single Tone |

| 0 | 0 | 1 | FSK |

| 0 | 1 | 0 | Ramped FSK |

| 0 | 1 | 1 | Chirp |

| 1 | 0 | 0 | BPSK |

在每种模式下都有许多功能不被允许。

(1)单信号模式(模式000)

这是用户复位之后的一种默认模式。也可以通过用户编程使能这种模式。相位累加器用以产生信号的频率,它有48位有效值,取自频率调整寄存器1,它的默认值为0。保留寄存器的默认值更能决定输出信号的质量。

用户复位后,默认设置配置器件,输出0HZ,0相位的信号。在上电复位时,在I和Q通道输出的是一半满幅电流的直流信号。这是默认模式的0幅度输出。选择幅度开关键控模式则需要更多细节的输出幅度控制。若输出用户定义的信号需要对28个寄存器全部或部分进行编程。

(2)无斜率FSK(模式001)

当这种模式被选中,输出的DDS频率是一个选择频率控制寄存器1和2的函数,它的输出取决于29脚逻辑电平的高低。29脚为逻辑低电平时选择F1(频率控制字1,并行地址为04H到09H),29脚为逻辑高电平时选择F2(频率控制字2,并行地址为0AH到0FH)。改变频率相位连续,并且和FSK数据引脚内部一致。但是,FSK数据信号和DAC输出存在线性时延。

无斜率FSK ,是传统FSK,它传输的是数字信号,它在数字通信中有着重要作用。但是它会影响RF发射机的使用带宽,因此用斜率FSK来改善使用带宽。

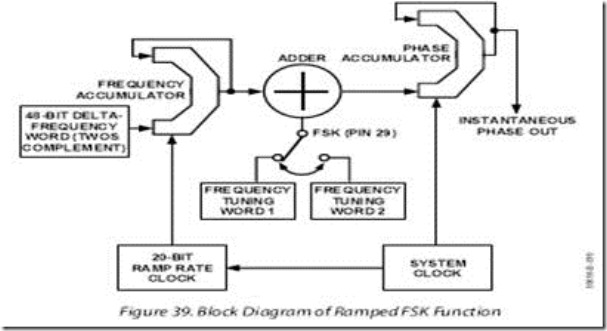

(3)斜率FSK(模式010)

这种FSK模式下,频率从F1到F2不是直接变化,而是通过扫频和斜率形成。线性扫频和斜率形成可以很容易的自动完成,不过这都是许多设置中的一项。其它频率传输的设置,用户可以配置增量控制寄存器,来编程控制扫频间隔和扫频速度。

频率斜率变化不管是线性还是非线性都会输出许多介于F1和F2之间的频率,而不仅是这两个基本输出。图37和38描述了一线性斜率FSK信号的频率输出与时间的关系。

需要注意,在斜率FSK模式下,频率步进字是要求编程设置的,它被用作双作用的补足值。须要注意的另一个问题是,最低频率一定要放在频率控制寄存器1中。

斜率FSK通过同缓慢的、用户定义变化率的实时频率来改善传统FSK对带宽的限制。输出信号在F1和F2频率点保持时间与其它实时点相同或稍大。与传统FSK不同,斜率FSK要求:F1和F2分别存储低频率和高频率,而不能任意。

用户必须通过编程来设定DDSd的中间频率变化的步进量of C48位)和每一步所持续的时间△T (20位)。另外,如果要想让频率输出从0开始变化必须先给CLR ACC1位送一个正脉冲。对于分段的非线性频率传输,必须对影响输出的寄存器进行编程设置。

并行寄存器1AHex~1CHex构成一个20位的斜率时钟寄存器。它是一个减计数器,当计数值为0时输出一个脉冲信号。在29脚的输入电平没有变化时计数器一直有效。这个计数器在系统时钟下运行,最大频率是300MHZ。每两个脉冲之间的时间周期用下式表示:

(N+1)*(System Clock Period)

此处N是用户编程设置的20位斜率变化率。N的允许范围是1到(2^20-1)。斜率变化时钟决定频率F1和F2 之间的实时频率持续时间。当频率达到目标频率时计数器自动停止,而F1和F2两频率点的持续时间由29脚输入的电平决定,电平的高低决定到达的频率点的状态。

并行寄存器10Hex~15Hex构成一个48位的双作用的斜率步进寄存器。当接收到斜率变化时钟时,这个48位控制字被累加。此控制字被用来加或减到控制正弦或余弦输出的相位步进的频率控制字寄存器F1或F2。在这种模式下,29脚的电平状态决定输出的频率是增量或减量斜率。其频率变化率是20位斜率变化寄存器的功能,一旦目标频率到达,计数器将停止计数即频率累加过程停止。

一般来说,频率步进字与频率控制字相比是一个比较小的值,举个例子,如果F1和F2分别是1KHZ和13MHZ,那么步进频率字只有25HZ。

图41显示了,电平过早的变化使频率的斜率变化翻转,并且以相同的变化率返回原状态。控制寄存器(1FHex)中含有一个“三角形”位。在010模式下设置此位为高电平将会再频率F1和F2之间进行三角形自动扫频,而不会受29脚电平变化的影响,如图40。一旦这个位设置为1,29脚的状态将不会起作用。这一功能需要设置频率变化率和频率步进字来保证F1和F2之间的连续线性扫频具有相同的持续时间。使用此功能,可以对直流到最大输出频率之间的自动扫频。

在斜率FSK模式下29脚的电平和“三角形”位的上升沿决定扫频是从F1或F2开始(如图42)。如果29脚电平是高电平而不是低电平,扫频则从F2开始而不是F1。在F1和F2之间的斜率变化时,通过改变20位频率变化控制字和频率步进控制字,可增加斜率FSK模式的灵活性。结合多个线性斜率变化和各分段的不同斜率设置,可实现非线性的频率变化。在不同的设置下,DDS的输出频率在Fl和F2之间以不同的方式变化,实现多种方式扫频。

(4)脉冲调频(模式011)

“Chirp”也称为“脉冲调频”( Pulsed FM) 。该模式下,输出信号的频率在指定的范围和精度上发生线性或非线性的变化,扫描方向可以编程控制。该模式需要用户通过“HOLD”状态(29 管脚高电平) 控制停止频率点,并控制频扫停止后的状态。Chirp模式是在指定的频率范围和频率精度上,频率可以是线性或非线性变化输出,而且扫频方向可控。在此模式中,大多数Chirp系统采用FM扫描方式,即FM Chirp模式,分线性和非线性脉冲调频两种方式。先设置频率控制字F 1,然后设置频率变化的步进量OF和每一步所持续的时间△T,最后使能更新实现脉冲调频。如果OF为正(最高位为0),频率从F1向正方向扫描;4F为负(最高位为1),则频率从F1向负方向扫描。与RampedFSK模式相比,该模式需要用户自己通过‘`HOLD" (P29高电平)控制停止频率点,同时控制停止后的状态。一些复杂的跳频功能在这个模式下可以实现。

当AD9854工作在Chirp模式下时,基本编程步骤如下:

(1)将初始频率控制字WFc写入48位FTWI (Frequency Tuning Word 1)中。

(2)将频率步进量写入48位DFW (Delta Frequency Word)中。

(3)将时间步进量写入20位RRC (Ramp Rate Clock)中。

(4)更新脉冲,将数据送入DDS核进行合成,输出信号。

在两个互补DWT中定义FM Chirp跳动的方向是有必要的。若果48位是DWT负的(MSB是高),则频率增量将会从FTW1向负方向改变。若果48位DWT字是正的(MSB是低),则频率增量将会向正方向改变。

值得注意的是FTW1仅仅是FM Chirp的开始点。这里没有约束返回FTW1的要求,一旦FM Chirp产生,它将会在奈奎斯特带宽(直流到系统时钟1/2速率)自由跳动(在编程控制范围下)。

在FM Chirp模式中有两个控制位可以利用,将会使能够返回开始频率FTW1,或返回到0HZ。首先,当CLR ACC1位(寄存器地址1F HEX)设置为高,48位频率累加(ACC1)的输出被清除,在一个持续一个系统时钟周期的retriggerable短脉冲后。输入到累加器的48位DWT字不影响CLR ACC1位。若果CLR ACC1位保持为高,单一短脉冲将会被释放到频率累加器(ACC1),在每一个I/O更新时钟的上升沿,其作用是干扰当前的调频,设置频率回到FTW1,以先前编程写好的速率和变化的方向继续该调频。在该调频模式中,清除频率累加器的输出如图19所示。如图中所示的I/O更新时钟,可以是使用者提供的或内部产生的。在该数据库中到处可以见到讨论I/O更新的描述。

另外,CLR ACC2控制位(寄存器地址1F HEX)是用于清除频率累加器和相位累加器的。当该位设置为高,相位累加器的输出将会从DDS中输出0HZ。只要该位设置为高,频率和相位累加器将会被清除。从0HZ从新输出。要从新回到先前的DDS操作,CLR ACC2必需设置为逻辑低,该位在脉冲产生FM中是非常之有用的。

图20表示作用于CLR ACC2位上的DDS输出频率。注意到寄存器被编程,当CLR ACC2位是高允许新的FTW1频率和斜升速率被生成。

另一种功能,只用于调频模式中,它就是HOLD引脚,引脚29。该功能是停止进入斜升速率计数器的时钟信号。因此阻止任何更高时钟脉冲进入频率累加器,ACC1。其作用是保持调频跳动在目前的频率上面,在HOLD被拉高之前。当HOLD引脚回到底电平,始终重新使用和调频继续进行。在HOLD条件期间,使用者可以改变寄存器的编程,然而,斜升速率计数器必需重新操作在原来的速率直到计数器计数为0,也包含在以各新的斜升速率技术产生。图21表示来HOLD功能在DDS输出频率的作用。

32位自动I/O更新计数器可以用于复杂结构的调频或斜升FSK序列。由于该内部计数器是以AD9854系统时钟合成的。它允许精确的时间编程改变被要求。在该情况下,仅仅要求使用者编写想要的仅存器早于更新时钟被产生。

在调频模式中,中心频率不是直接具体指定的,若用户不能控制调频,DDS将会在DC(直流频率)到奈奎斯特范围中自己选择。除非被用户终止,否则调频将会持续到系统能有能力(也就是系统没有电提供)。

当调频的中心频率达到后,有几个问题自然的会产生:

⊙在中心频率停止使用HOLD引脚,或者写全0入频率累加器DWT寄存器中。

⊙使用HOLD引脚功能停止调频的跳动,用数字相乘器和Shaped Keying引脚,引脚30,或经过可编程寄存器控制(地址21-24 HEX)。

⊙使用CLR ACC2位控制突发中断传输。

⊙使用反方向,返回先前的频率或另一个频率点,中频以线性或用户直接方法继续调频。如果其与下行频率有关,一个负极性的48位DWT位(MSB设置为高’1’)必须寄存入寄存器地址10-15 HEX。DWT字的频率减少步进要求MSB设置为逻辑高电平。

⊙连续调频由立刻返回到起点频率(F1) 锯齿时期和重覆先前的调频过程。这是CLR ACC1 控制位被使用的地方。自动, 重覆调频可能被设定使用32 位更新时钟发出CLR ACC1 指令在精确时间间隔时间。调整间隔时间或改变DWT频率字将改变调频的范围。这是新任在用户平衡调频期间和频率决议达到适当的频率范围。

(5)二进制相移键控(模式100)

BPSK模式:与FSK 模式的控制方式相同,只是F1 为载波频率,29 管脚选择相位控制字P1 (低电平)和P2 (高电平) 中的相位作为信号的相位输出。此外,还要通过频率寄存器对输出信号的频率进行控制。实现过程为:先将载波频率送频率控制寄存器1,然后将相位控制字送至相位控制寄存器1和2,再将BPSK的调制数据加载到BPSK端口,最后使能更新。

当AD9854工作在BPSK模式下时,基本编程步骤如下:

(1)将初始频率控制字WFC写入48位FTWI (Frequency Tuning Word 1)中。

(2)将两个14位相位控制字分别送入相位调节寄存器P1和P2中。

(3)将时间步进量写入20位RRC (Ramp Rate Clock)中。

(4)更新脉冲,将数据送入DDS核进行合成,输出信号。