|

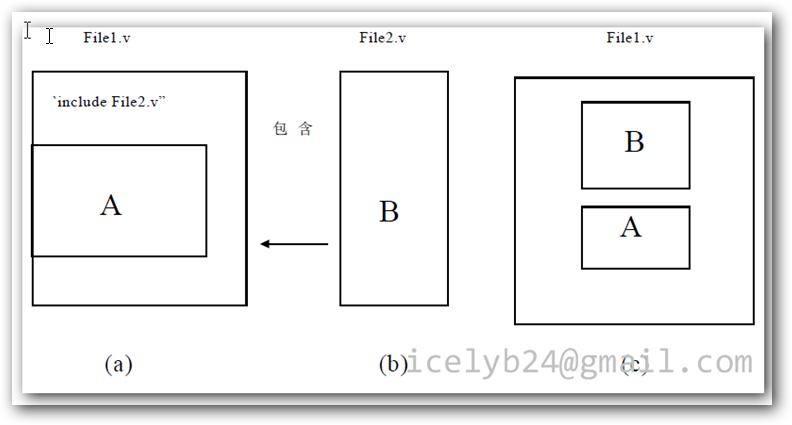

"文件包含"处理`include 所谓"文件包含"处理是一个源文件可以将另外一个源文件的全部内容包含进来,即将另外的文件包含到本文件之中。Verilog HDL语言提供了`include命令用来实现"文件包含"的操作。其一般形式为: `include "文件名"

图中意思为:在编译的时候,需要对`include命令进行"文件包含"预处理:将File2.v的全部内容复制插入到`include "File2.v"命令出现的地方,即将File2.v被包含到File1.v中,得到图C的结果。在接着往下进行编译中,将"包含"以后的File1.v作为一个源文件单位进行编译。 "文件包含"命令是很有用的,它可以节省程序设计人员的重复劳动。可以将一些常用的宏定义命令或任务(task)组成一个文件,然后用`include命令将这些宏定义包含到自己所写的源文件中,相当于工业上的标准元件拿来使用。另外在编写Verilog HDL源文件时,一个源文件可能经常要用到另外几个源文件中的模块,遇到这种情况即可用`include命令将所需模块的源文件包含进来。 [例1]: (1)文件aaa.v module aaa(a,b,out); input a, b; output out; wire out; assign out = a^b; endmodule (2)文件 bbb.v `include "aaa.v" module bbb(c,d,e,out); input c,d,e; output out; wire out_a; wire out; aaa aaa(.a(c),.b(d),.out(out_a)); assign out=e&out_a; endmodule 在上面的例子中,文件bbb.v用到了文件aaa.v中的模块aaa的实例器件,通过"文件包含"处理来调用。模块aaa实际上是作为模块bbb的子模块来被调用的。在经过编译预处理后,文件bbb.v实际相当于下面的程序文件bbb.v: module aaa(a,b,out); input a, b; output out; wire out; assign out = a ^ b; endmodule module bbb( c, d, e, out); input c, d, e; output out; wire out_a; wire out; aaa aaa(.a(c),.b(d),.out(out_a)); assign out= e & out_a; endmodule

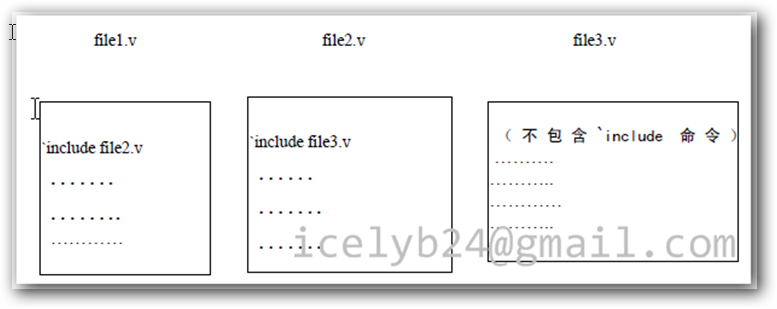

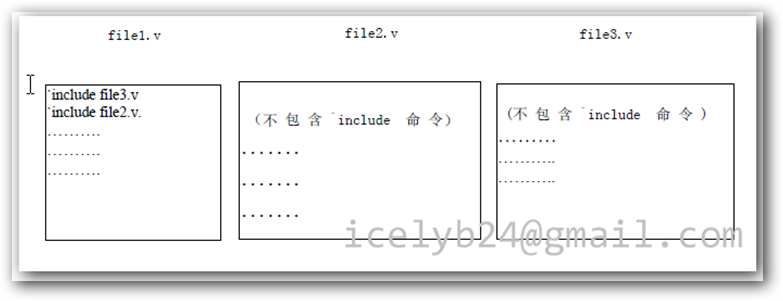

关于"文件包含"处理的四点说明: 1) 一个`include命令只能指定一个被包含的文件,如果要包含n个文件,要用n个`include命令。注意下面的写法是非法的`include"aaa.v""bbb.v" 2) `include命令可以出现在Verilog HDL源程序的任何地方,被包含文件名可以是相对路径名,也可以是绝对路径名。例如:'include"parts/count.v" 3) 可以将多个`include命令写在一行,在`include命令行,只可以出空格和注释行。例如下面的写法是合法的。 'include "fileB" 'include "fileC" //including fileB and fileC 4) 如果文件1包含文件2,而文件2要用到文件3的内容,则可以在文件1用两个`include命令分别包含文件2和文件3,而且文件3应出现在文件2之前。例如在下面的例子中,即在file1.v 中定义: `include"file3.v" `include"file2.v" module test(a,b,out); input[1:`size2] a, b; output[1:`size2] out; wire[1:`size2] out; assign out= a+b; endmodule file2.v的内容为: `define size2 `size1+1 . . . file3.v的内容为: `define size1 4 . . . 这样,file1.v和file2.v都可以用到file3.v的内容。在file2.v中不必再用 `include "file3.v"了。 5) 在一个被包含文件中又可以包含另一个被包含文件,即文件包含是可以嵌套的。例如 上面的问题也可以这样处理。

它的作用和下图的作用是相同的。

本文摘自夏宇闻老师的《Verilog HDL教程》

By:冰凤溪谷

|